# The family of 4-phase latch controllers

Graham Birtwistle Ken Stevens DCS, Sheffield ECE, Utah

Async 2008 (April) Newcastle

A systematic way of studying the designspace for untimed, bundled, 4-phase latch controllers.

- 1. Shape of the most concurrent protocol.

- 2. Its family of less-state rich shapes.

- $3.\ {\rm Categorising/relating}$  the family.

- 4. Tabulation of pipeline behaviours.

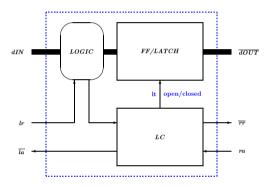

Setting:

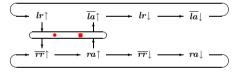

notation  $in, \overline{out}$

#### Suitable abstraction for LC behaviours?

We argue that:

• internal states: implicit part of a spec • logic: just delays lr (or  $\overline{la}$ )

• enable: another lateral delay

STG: Furber and Day, sect 6

- In our abstractions, internal states a and

b are hidden; likewise lt.

- The constraints they impose will remain.

- Each abstraction will have several circuit implementations, each of which have the same pipeline characteristics.

# Pipeline models

Outputs  $\overline{rr}/\overline{la}$  and Inputs lr/ra

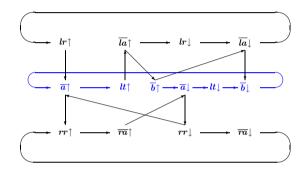

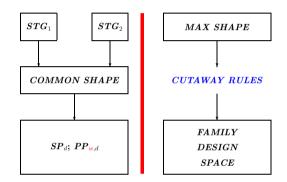

# STGs/Abstract Shape/Family

- 1. Several STG's  $\rightarrow$  same abstract shape.

- 2. We can compare shapes.

- 3. We can define the maximal shape ... and its derivative family.

#### Max latch controller protocol

$$egin{array}{lll} L & = & lr \uparrow & . & \overline{la} \uparrow & . & lr \downarrow & . & \overline{la} \downarrow & . & L \ & & = & \overline{rr} \uparrow & . & ra \uparrow & . & \overline{rr} \downarrow & . & \overline{ra} \downarrow & . & R \ & LC & = & ( & L \mid R & ) \end{array}$$

In CCS  $lr\uparrow.\overline{la}\uparrow$  is read as  $lr\uparrow$  then some time later  $\overline{la}\uparrow$  All possible interleavings are traced

$$L \hspace{0.5cm} = \hspace{0.1cm} lr \! \uparrow \hspace{0.1cm} . \hspace{0.1cm} \bullet \hspace{0.1cm} . \hspace{0.1cm} \overline{la} \! \uparrow \hspace{0.5cm} . \hspace{0.1cm} lr \! \downarrow \hspace{0.1cm} . \hspace{0.1cm} \overline{la} \! \downarrow \hspace{0.1cm} . \hspace{0.1cm} L$$

$$R = ullet \cdot \overline{rr} \!\! \uparrow \quad \cdot ra \!\! \uparrow \cdot lacktriangle \cdot \overline{rr} \!\! \downarrow \cdot \overline{ra} \!\! \downarrow \cdot R$$

$$LC_{max} = (L \mid R \mid \bullet \mid \blacksquare) \setminus \{\bullet, \blacksquare\}$$

# **UNTIMED Cutaway Rules**

Cheap version:  $LC_{max}$ , shape 9599.

- 1. same state when quiescent

- 2. no holes in the state graph

- 3. always accept an input lr/ra

- 4. may delay an output  $\overline{la}/\overline{rr}$

# The Cut-Away Notation

. 0 0 0 0 0 0 0 0

Left cut-aways constrain  $\overline{rr}/ra$ .

Right cut-aways constrain  $\overline{la}/lr$ .

#### **Cut-Away Notation II**

- L1001 o R0040 (Furber/Day, sect. 6)

- ullet ALL L o R o generates the whole family

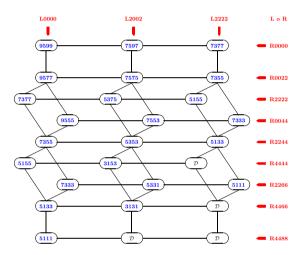

- The cutaway options make it trivial to order the family into a lattice

$$egin{aligned} & m{L}_1 \ \mathbf{o} \ m{R}_1 \supseteq m{L}_2 \ \mathbf{o} \ m{R}_2 \ & \mathbf{IFF} \ & m{L}_1 \supseteq m{L}_2 \ \mathbf{AND} \ m{R}_1 \supseteq m{R}_2 \end{aligned}$$

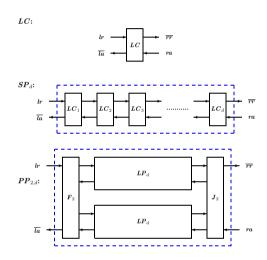

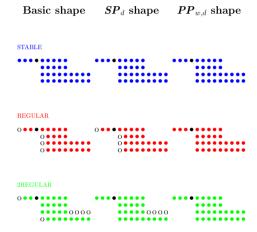

#### Pipeline categories

Is shape preserved when pipelined?

#### Protocol categories

- 6 categories emerge:

- : STABLE

- **.:** 2reg

- : linear

regular: O(8): as O(16)

$\frac{dead}{dead}$ :

10

11

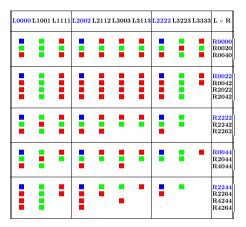

# Parallel pipelines

# $PP_{w,d}$

| L0000 | L1001 | L1111 | L2002 | L2112 | L3003 | L3113 | L2222 | L3223 | L3333 | BL o R                           |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|----------------------------------|

| :     | :     | :     | •     | :     | :     | :     | :     | :     | :     | R0000<br>R0020<br>R0040          |

| :     |       |       | ••••  | :     | :     |       | :     | :     | :     | R0022<br>R0042<br>R2022<br>R2042 |

| :     | :     | :     | •     | :     | :     | :     | :     | :     |       | R2222<br>R2242<br>R2262          |

| •••   | :     | :     | •••   | :     | :     | :     | •     | :     | •     | R0044<br>R2044<br>R4044          |

| :     | :     | :     | • • • | :     | :     | •     | •     | •     |       | R2244<br>R2264<br>R4244<br>R4264 |

#### Independent of w.

Same result throughout each block.

Maths says TL; Engineering BR?

# Single pipelines

| 0000     | L1001    | L1111    | L2002    | L2112         | L3003         | L3113    | L2222    | L3223         | L3333         | LoR            |

|----------|----------|----------|----------|---------------|---------------|----------|----------|---------------|---------------|----------------|

| 48       | 48       | 44       | 44       | 42            | 42            | 40       | 40       | 36            | 36            | R0000          |

| 48<br>44 | 48<br>44 | 44<br>40 | 44<br>40 | 42<br>38      | 42<br>38      | 40<br>36 | 40<br>36 | 36<br>32      |               | R0020<br>R0040 |

|          |          |          |          |               |               |          |          |               |               |                |

| 44<br>42 | 44<br>42 | 40<br>38 | 40<br>38 | 38<br>36      | 38<br>36      | 36<br>34 | 36<br>34 | 32<br>30      |               | R0022<br>R0042 |

| 42       | 42       | 38       | 38       | 36            | 36            | 34       | 34       | 30            |               | R2022          |

| 40       | 40       | 36       | 36       | 34            | 34            | 32       | 32       | 28            |               | R2022          |

| 40       | 40       | 30       | - 30     | 34            | 34            | 32       | - 32     | 20            | D             | R2042          |

| 40       | 40       | 36       | 36       | 34            | 34            | 32       | 32       | 28            | $\mathcal{D}$ | R2222          |

| 36       | 36       | 32       | 32       | 30            | 30            | 28       | 28       | 24            | $\mathcal{D}$ | R2242          |

| 36       | 36       | 32       | 32       | 30            | $\mathcal{D}$ | D        | 28       | $\mathcal{D}$ | $\mathcal{D}$ | R2262          |

| 40       | 40       | 36       | 36       | 34            | 34            | 32       | 32       | 28            | 28            | R004           |

| 36       | 36       | 32       | 32       | 30            | 30            | 28       | 28       | 24            |               | R2044          |

| 36       | 36       | D        | 32       | $\mathcal{D}$ | 30            | 20<br>D  | D 20     | $\mathcal{D}$ |               | R4044          |

$\mathbf{SP}_2$

lacktriangle shapes behave as lacktriangle shapes for  $d \geq 2$ . Many distinct shapes. Equivalences stay in the same box.

24 22 22 22 20  $\mathcal{D}$ 22  $\mathcal{D}$  20 20  $\mathcal{D}$

24 22 D D

28 28 26 26 26 26 24 24

# Lattice of stable shapes

13

14

#### Published circuit shapes

| L0000 L1001 L1111 | L2002 L2112 L3003 L3113 | L2222 L3223 L3333 | $\mathbf{L} \circ \mathbf{R}$    |

|-------------------|-------------------------|-------------------|----------------------------------|

|                   | •                       |                   | R0000<br>R0020<br>R0040          |

|                   |                         |                   | R0022<br>R0042<br>R2022<br>R2042 |

|                   | •                       | •                 | R2222<br>R2242<br>R2262          |

|                   | •                       |                   | R0044<br>R2044<br>R4044          |

|                   | •                       |                   | R2244<br>R2264<br>R4244<br>R4264 |

Includes: Early; Broadish; Broad Un-/Semi-/Fully-Decoupled Normally open/normally closed

#### What's been done

- 1. Idea of an abstract design shape and how it composes.

- Each shape may have many implementations but each will maintain the piped behaviour of its shape

- 2. Family of untimed, bundled protocols derived by cutaways from the most state rich shape.

- Cutaways enable us to order the family.

- 3. We have classified pipeline behaviours for the whole family of shapes.

- And can predict mixed parallel pipeline behaviour from their cutaways.

#### What's to be done

- 1. Circuit chrestomathy and shape cook book. Any other circuits out there?

- 2. Including lt signals (goes exponential).

- 3. Mixed parallel pipelines  $\sqrt{.}$  Single pipelines en route.

- 4. Maths/Engineering interplay and insights.

- 5. Timed disciplines.

- 6. Y (Ken is generating circuits).

16

17