## A Level-Encoded Transition Signaling Protocol for High-Throughput Asynchronous Global Communication

Peggy B. McGee, Melinda Y. Agyekum, Moustafa M. Mohamed and Steven M. Nowick

{pmcgee, melinda, mmohamed, nowick}@cs.columbia.edu

Department of Computer Science Columbia University

April 10, 2008

## **Trends in Digital Systems Design**

#### Increased design complexity

- More functionality on a single chip

- $\rightarrow$  Smaller transistor size

- $\rightarrow \text{Larger die size}$

- Multiple clock domains

#### High-performance computing

- Multi-Giga Hertz clock rate

- Multiple independent computation nodes

- $\rightarrow$  Processor cores, memories, etc.

#### Plug-&-play components

• For re-usability

## System-on-Chip (SoC): Challenges

#### Heterogeneity

- Multiple clock domains

- Mixed asynchronous/synchronous components

- Wires do not scale at the same rate as transistors

- Increasing proportion of delay in interconnects

- Challenges for global routing in physical design

#### Deep submicron effects

- Handling dynamic timing variability, crosstalk, EMI, noise, etc.

- Clock jittering and/or drifting effects

- Power dissipation

- Interconnects a significant source of of power

#### Need for new approaches for interconnect design

## SoC Communication Fabric: Ideal Requirements

#### ► Speed

• High throughput, low latency

#### Low power

Low switching activity

#### Robustness

- Against timing variation

- Handling dynamic voltage scaling

- Handling single-event upset effects (soft errors)

#### ► Flexibility

• Easy integration of modular Intellectual Properties (IPs)

## Asynchronous Design for SoC Communication

#### Potential benefits of asynchronous design

- Significant power advantage

- $\rightarrow$  No clock routing

- $\rightarrow$  "Compute-on-demand" approach

- Timing robustness using delay-insensitive (DI) encoding

- $\rightarrow$  Eliminates global timing constraints

- $\rightarrow$  Accommodates uncertainties in routing delay

- $\rightarrow$  Accommodates skew between bits

- Supports modular design methodologies

- $\rightarrow$  e.g. GALS (globally-asynchronous, locally-synchronous)

- $\rightarrow$  Mixed synchronous/asynchronous components

# Asynchronous design well-suited for ideal requirements of SoC communication

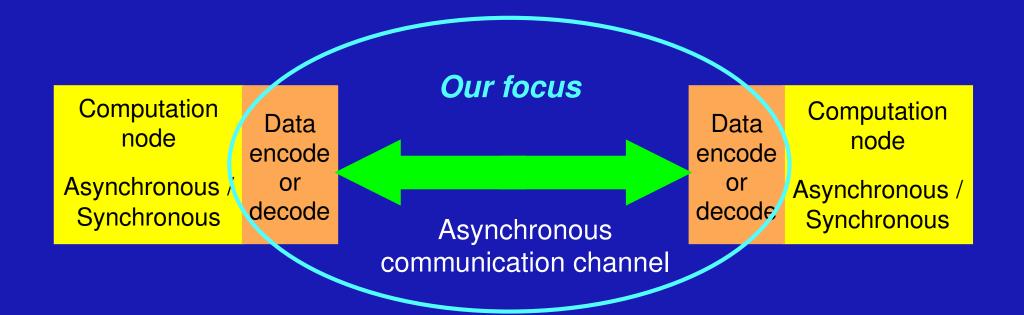

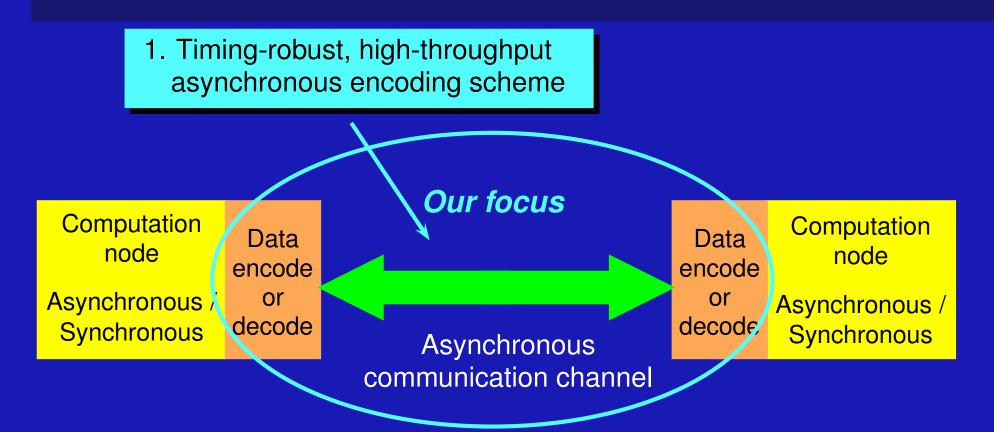

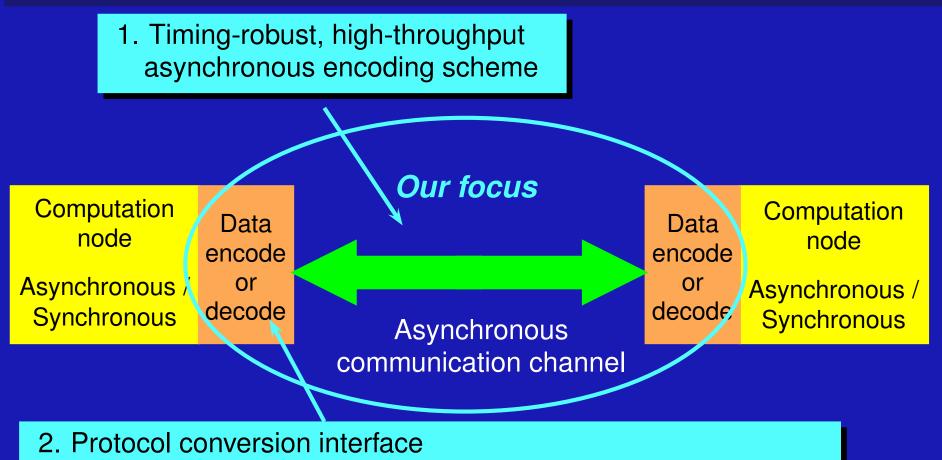

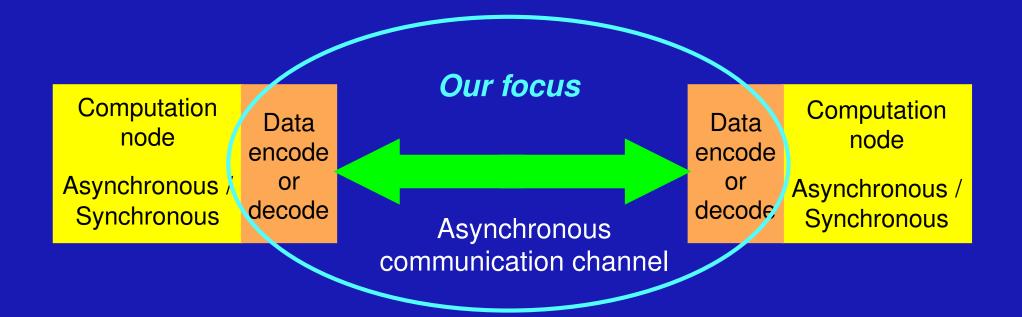

- --- Allows separation of computation and communication

- Some codes are better for computation

- Some codes are better for communication

Current focus is on asynchronous computation nodes  $\rightarrow$  Expandable to synchronous

## **Key Contributions: Theoretical**

#### A new class of delay-insensitive code for global communication

"Level-Encoded Transition Signaling (LETS)"

- Delay-insensitive

- $\rightarrow$  Timing-robust

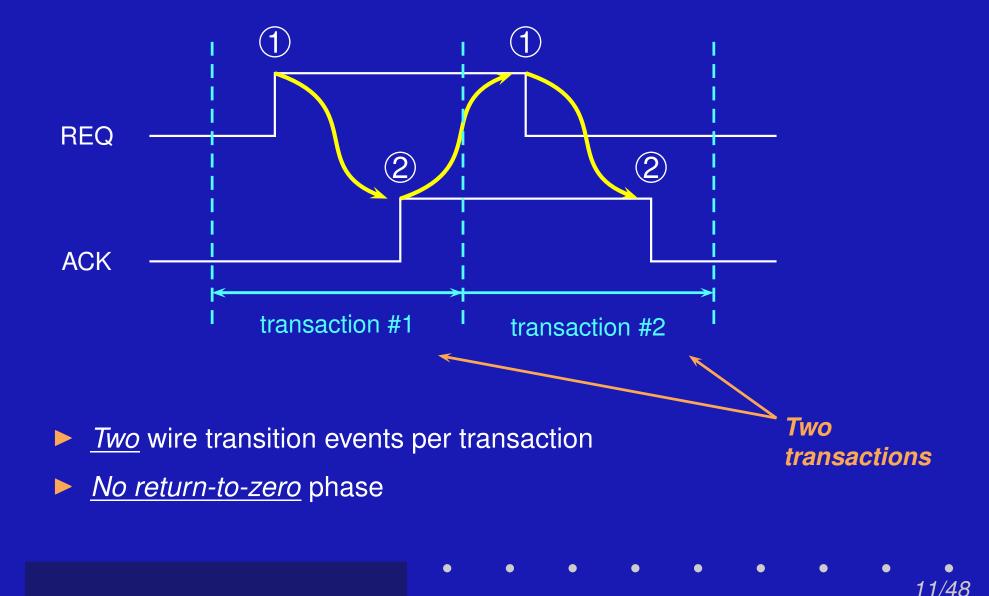

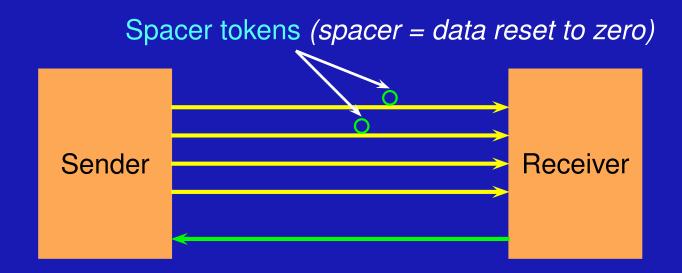

- Uses two-phase (transition) signaling

- → High throughput: no return-to-zero phase

- $\rightarrow$  most existing schemes use four-phase: have spacer phase

- $\rightarrow$  Low switching activity

- Level-encoded data

- $\rightarrow$  Data values easily extracted from encoding

- Supports 1-of-N encoding

- $\rightarrow$  Lower switching activity

- $\rightarrow$  compared to existing level-encoded transition signaling code

7/48

$\rightarrow$  Main focus: 1-of-4 codes

## **Key Contributions: Practical**

#### Practical 1-of-4 LETS codes

- Two example codes shown

- $\rightarrow$  "Quasi-1-hot/cold"

- $\rightarrow$  "Quasi-binary"

#### Generalization to 1-of-N LETS codes

- First to demonstrate 1-of-N level-encoded codes

- Systematic procedure to generate LETS codes for all  $N = 2^n$

#### Hardware support

- Efficient conversion circuit for 1-of-4 LETS proposed

- → To/from 4-phase dual-rail signaling

- Pipeline design for global communication proposed

- $\rightarrow$  Improves throughput

## Outline

- Introduction

- Background

- Handshake protocol control signaling

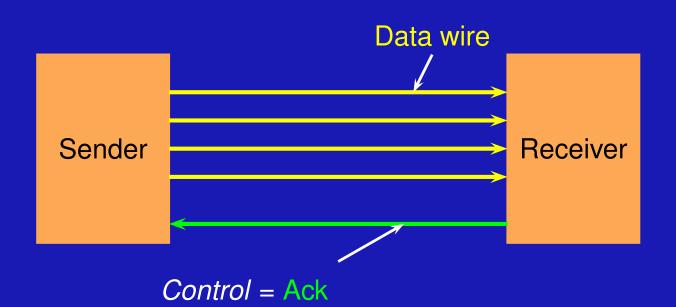

- Handshake protocol: control signaling + data

- Asynchronous data encoding

- 1-of-4 LETS codes

- 1-of-N LETS codes

- Hardware support

- Analytical evaluation

- Conclusions

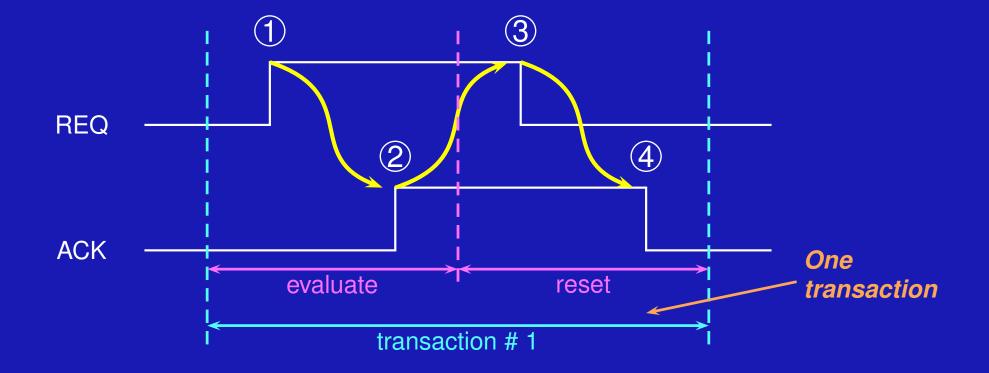

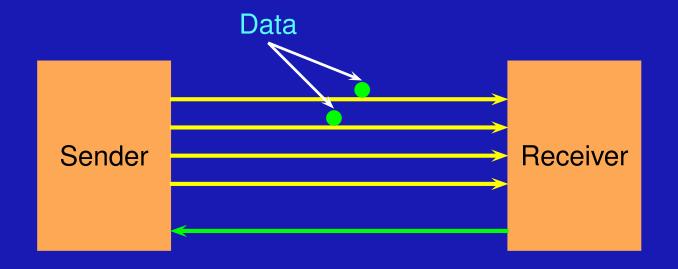

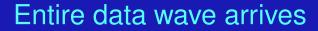

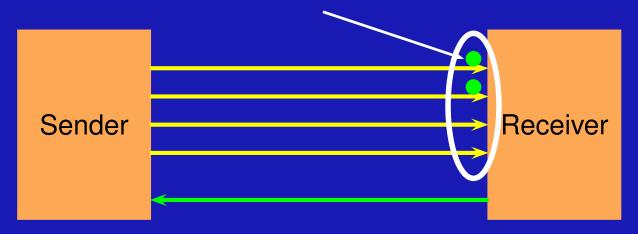

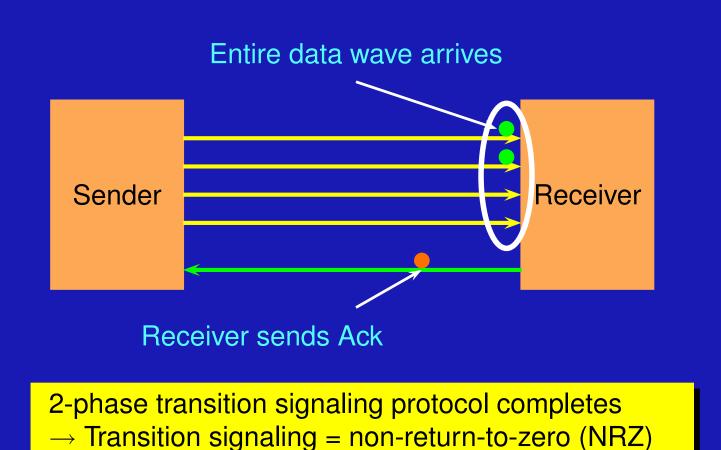

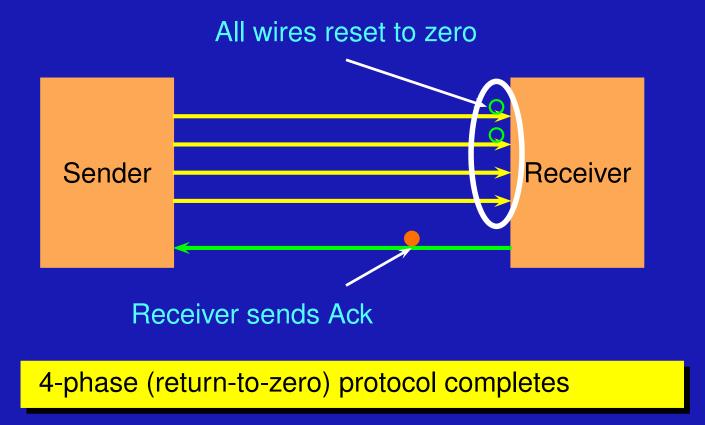

### Handshake Protocol Control Signaling: 4-Phase

- Four wire transition events per transaction

- All wires must <u>return to zero</u>

- $\rightarrow$  Before next transaction

## Handshake Protocol Control Signaling: 2-Phase

12/48

•

•

12/48

•

#### Round trip for 4-phase (return-to-zero) protocol

## Asynchronous Data Encoding: DI Codes

Properties of delay-insensitive (DI) codes

- Timing-robust

- $\rightarrow$  Insensitive to input arrival time

- Completion of data transaction encoded into data itself

$\rightarrow$  Unambiguous recognition of code

$\rightarrow$  no valid codeword seen when transitioning between codewords

## DI Return-to-Zero (RZ) Code #1: Dual-Rail

#### **Two wires to encode a single bit**

| Encoding |       | Symbolic value |  |

|----------|-------|----------------|--|

| $a_1$    | $a_0$ | a              |  |

| 0        | 0     | "reset" value  |  |

| 0        | 1     | 0              |  |

| 1        | 0     | 1              |  |

| 1        | 1     | illegal        |  |

14/48

#### Each dual-rail pair provides

- Data value: whether 1 or 0 is being transmitted

- Data validity: whether data is a value, illegal or reset

- ► Main benefit: allows simple hardware for computation blocks

- Main disadvantage: low throughput and high power → Needs reset phase: all bits always reset to zero

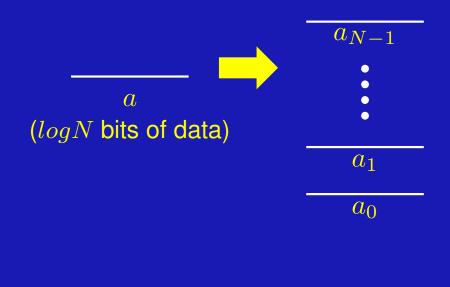

## DI Return-to-Zero (RZ) Code #2: 1-of-N

N wires to encode log N bits (one-hot encoding)

|       | Enco                        | oding | Symbolic value |               |  |  |  |

|-------|-----------------------------|-------|----------------|---------------|--|--|--|

| $a_3$ | $a_2$                       | $a_1$ | $a_0$          | a             |  |  |  |

| 0     | 0                           | 0     | 0              | "reset" value |  |  |  |

| 0     | 0                           | 0     | 1              | 00            |  |  |  |

| 0     | 0                           | 1     | 0              | 01            |  |  |  |

| 0     | 1                           | 0     | 0              | 10            |  |  |  |

| 1     | 0                           | 0     | 0              | 11            |  |  |  |

|       | All other codewords illegal |       |                |               |  |  |  |

15/48

Example: 1-of-4 code

Main benefit: uses lower power than dual-rail

$\rightarrow$  1 out of N rails changes value per data transaction

- Main disadvantage: gets expensive beyond 1-of-4

- $\rightarrow$  Coding density decrease

- $\rightarrow$  Complicated to concatenate irregularly-sized data streams

•

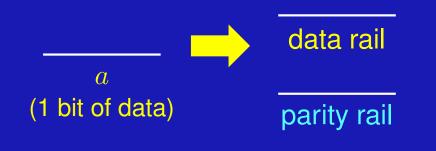

## DI Non-Return-to-Zero (NRZ) Code #1: LEDR

#### LEDR = Level-Encoded Dual-Rail

Two wires to encode a single bit

| E     | Symbolic |      |       |

|-------|----------|------|-------|

|       |          |      | value |

| Phase | Parity   | Data | a     |

|       | rail     | rail |       |

| Even  | 0        | 0    | 0     |

|       | 1        | 1    | 1     |

| Odd   | 1        | 0    | 0     |

|       | 0        | 1    | 1     |

16/48

#### Properties of LEDR codes:

- Level encoded: can retrieve data value directly from wires

- *Alternating phase protocol:* between odd and even phases

- Only 1 rail changes value: per bit per data transaction

Dean et al., "Efficient Self-Timing with Level-Encoded 2-Phase Dual-Rail (LEDR)", Proc. of UCSC Conf. on Adv. Research in VLSI, '91

#### DI Non-Return-to-Zero (NRZ) Code #1: LEDR (cont'd)

#### Main benefits

- No return-to-zero phase

- $\rightarrow$  High throughput, low power

- Easy to extract data

#### Main disadvantages

- Significantly more complicated function blocks

- $\rightarrow$  No practical solutions have been proposed

- $\rightarrow$  Potential solution strategy:

- $\rightarrow$  LEDR for *global communication*

- $\rightarrow$  4-phase RZ (dual-rail or single-rail) for computation

- → Need efficient hardware for conversion between protocols:

Mitra, McLaughlin and Nowick, "Efficient asynchronous protocol converters

for two-phase delay-insensitive global communication", ASYNC'07

- Uses more power than synchronous communication

- $\rightarrow\,$  Uses less power than RZ

## Outline

- Introduction

- Background

- 1-of-4 LETS codes

- 1-of-N LETS codes

- Hardware support

- Analytical evaluation

18/48

Conclusions

## **LETS Codes: Motivation & Contributions**

#### "LETS = Level-Encoded Transition Signaling"

#### ► A new class of delay-insensitive codes

- Extension of LEDR = 1-of-2 LETS

- $\rightarrow$  Uses fewer wire transitions per data transaction

- $\rightarrow$  Analogous to 1-of-N extension to dual-rail in RZ

- Goal:

- $\rightarrow$  Generate and evaluate entire family of 1-of-N codes

#### Key benefits

- Maintains benefits of LEDR

- $\rightarrow$  High throughput

- → Delay-insensitive

- → Efficient hardware conversion to 4-phase protocols

- Additional benefit

- $\rightarrow\,$  Lower power consumption than LEDR

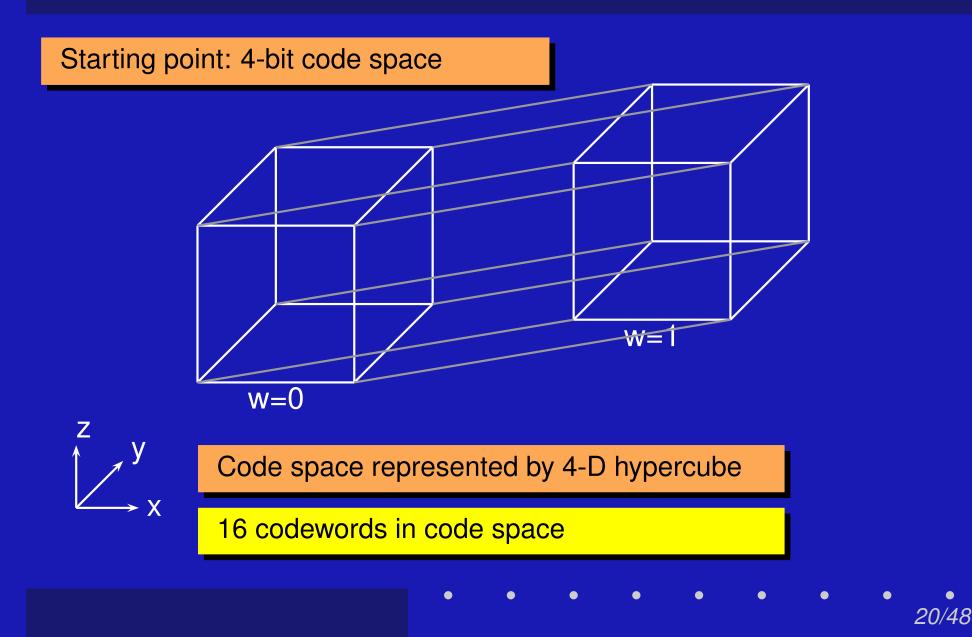

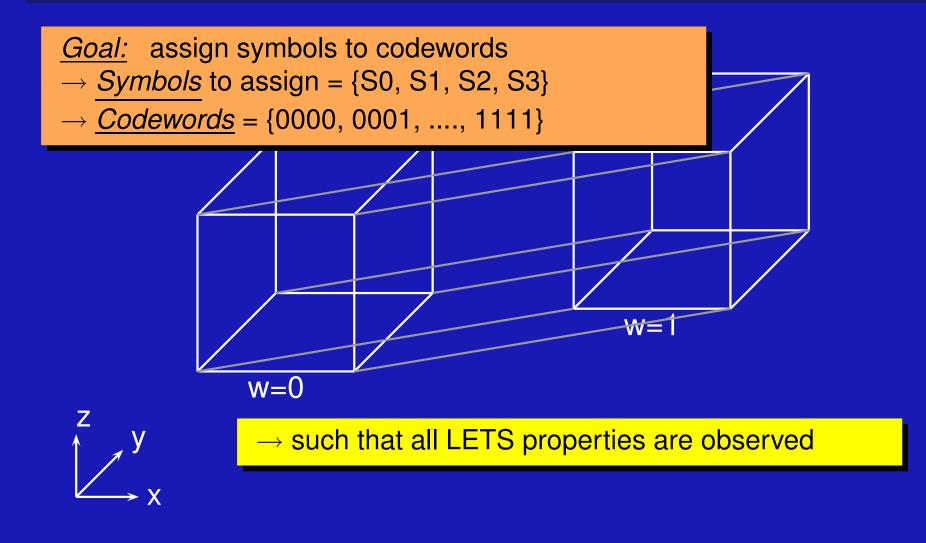

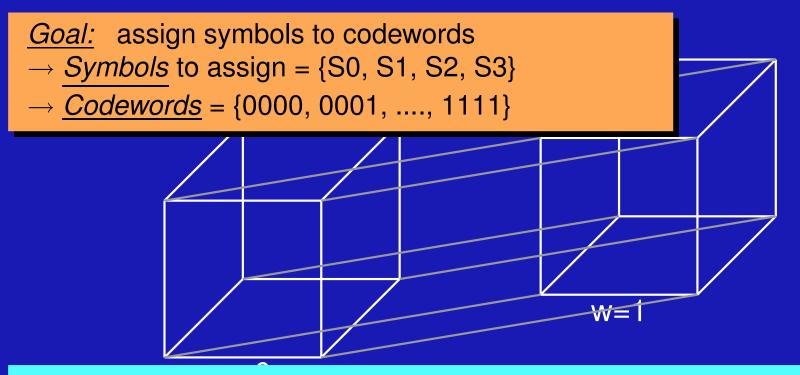

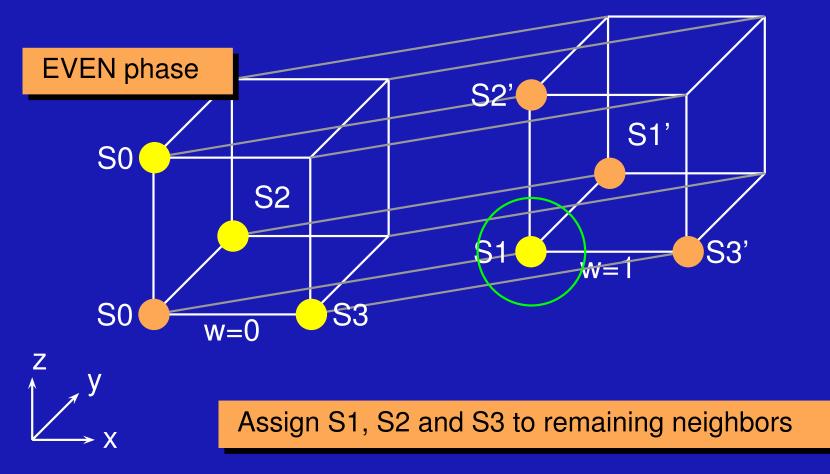

## 1-of-4 LETS Code Derivation: Overview

## 1-of-4 LETS Code Derivation: Overview

## 1-of-4 LETS Code Derivation: Overview

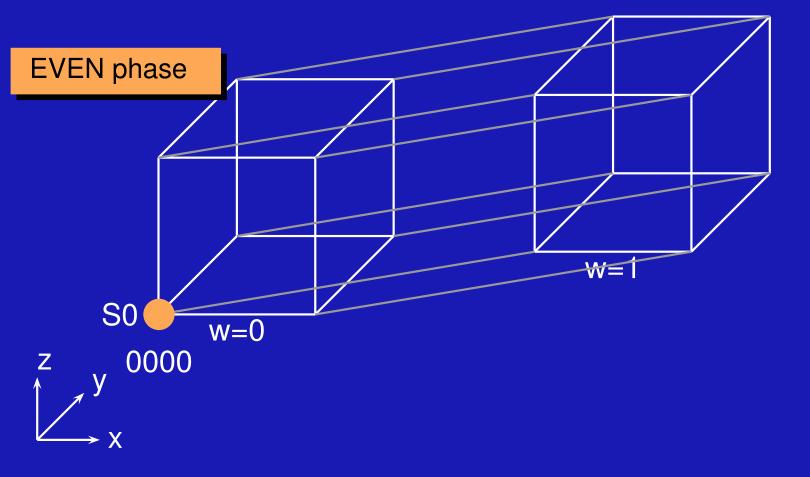

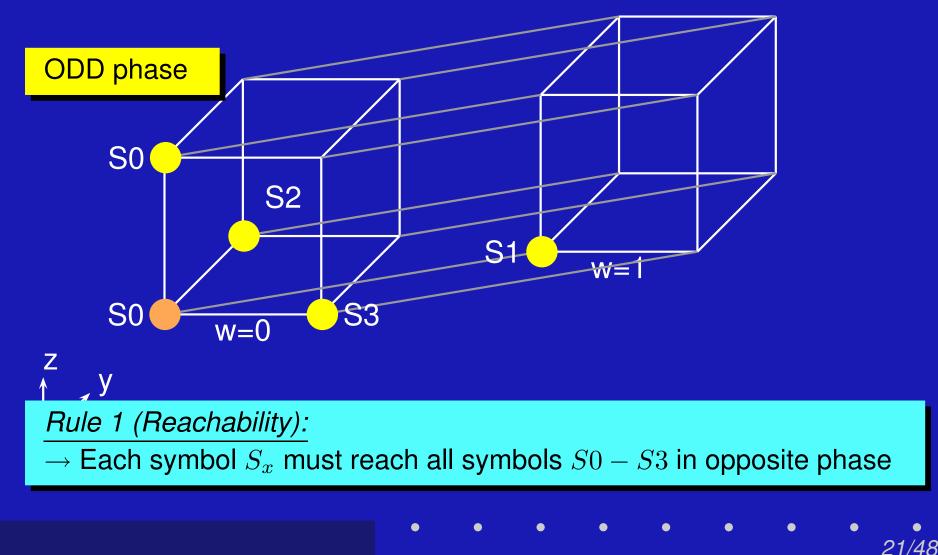

*Rule 1 (Alternating phases):*  $\rightarrow$  Odd and even phases must alternate

#### Rule 2 (Reachability):

$\rightarrow$  Each symbol  $S_x$  must reach all symbols S0 - S3 in opposite phase

•

Step 1: assign arbitrary symbol to arbitrary codeword

•

Step 2: assign symbols to all neighbors of S0 at 0000 in ODD phase

•

•

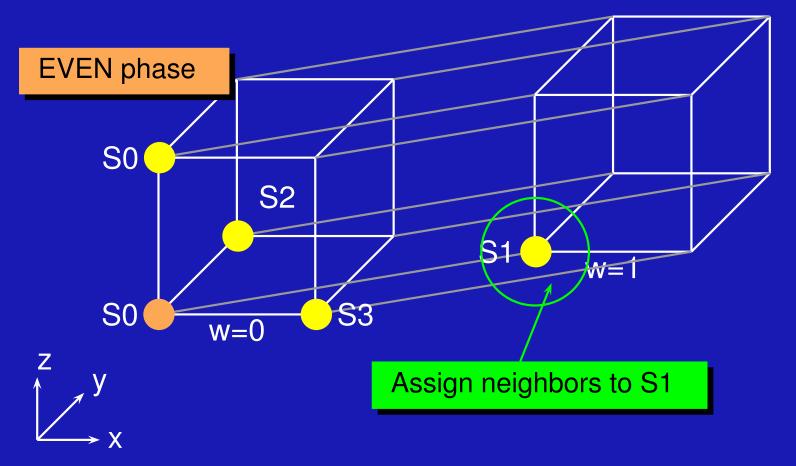

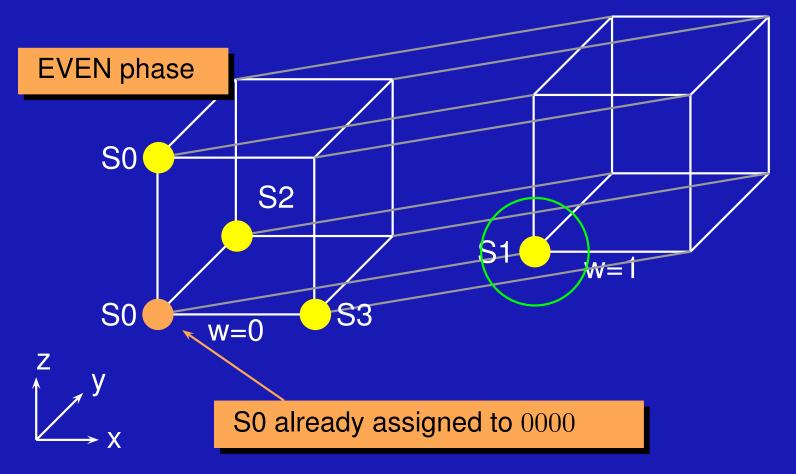

Step 3: assign symbols to all neighbors of S1 at 1000 in EVEN phase

•

Step 3: assign symbols to all neighbors of S1 at 1000 in EVEN phase

•

Step 3: assign symbols to all neighbors of S1 at 1000 in EVEN phase

## 1-of-4 LETS Code Derivation: Details

#### Final steps: complete symbol assignment **S**0' **S**3' **S**3 **S1** S2' S2' S1' **S**0 **S1** S0' S2 **S**2 S3' S1W= **S**0 **S**3 w=0 Follow same reasoning in previous steps

21/48

•

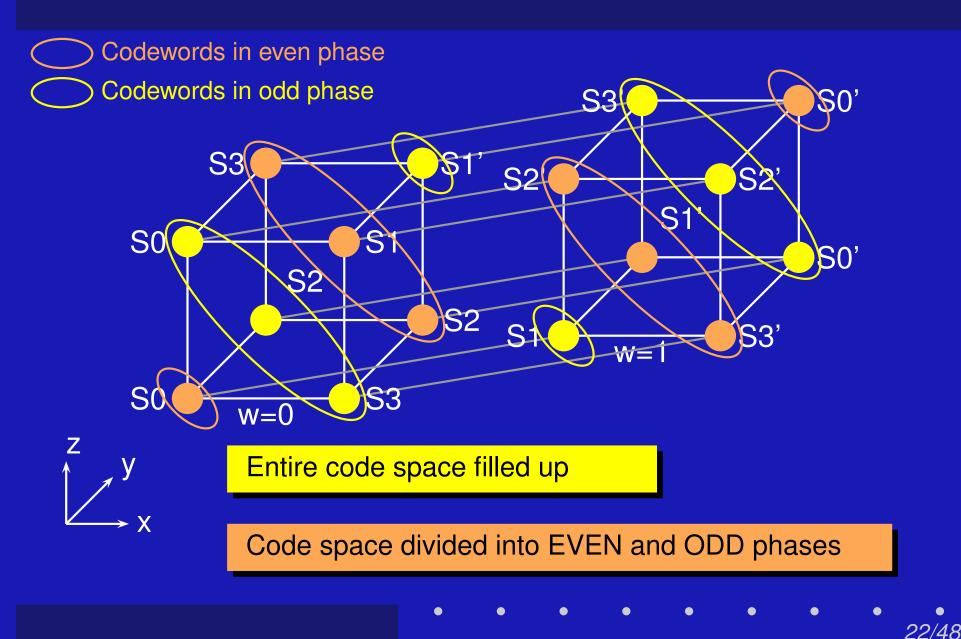

## 1-of-4 LETS Code Derivation: Summary

## 1-of-4 LETS Codes: Code Space

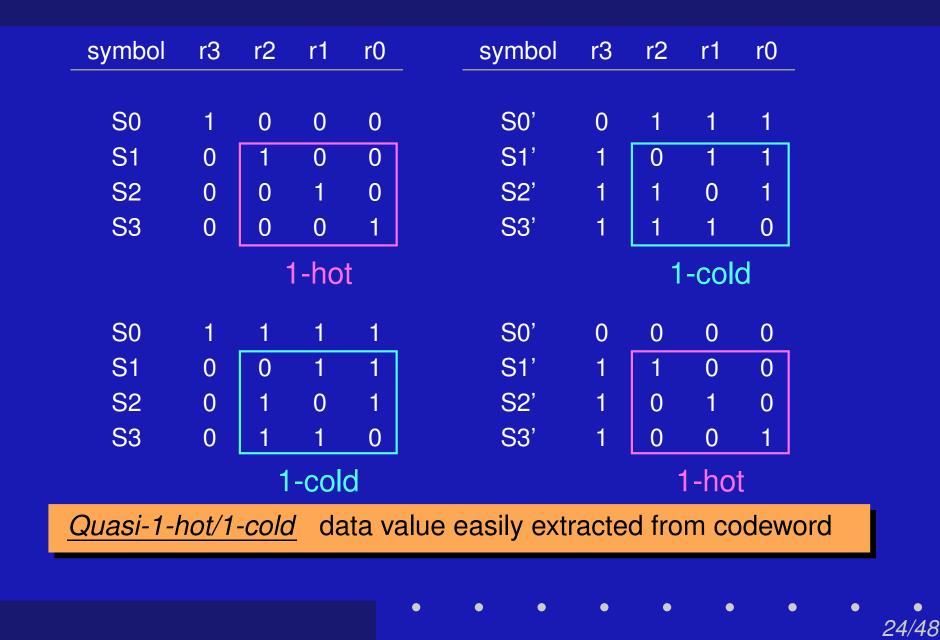

#### Many valid 1-of-4 codes possible

<u>1152</u> unique codes derivable from method shown

→ Complete enumeration derived in paper

Some codes more "practical" than others

All data values easily extracted from codeword

Our focus: Two "Practical" codes

- "Quasi-1-hot/cold"

- "Quasi-binary"

| symbol     | r3 | r2 | r1 | r0 | symbol      | r3 | r2 | r1 | rO |

|------------|----|----|----|----|-------------|----|----|----|----|

|            |    |    |    |    |             |    |    |    |    |

| <b>S</b> 0 | 1  | 0  | 0  | 0  | <b>S</b> 0' | 0  | 1  | 1  | 1  |

| S1         | 0  | 1  | 0  | 0  | S1'         | 1  | 0  | 1  | 1  |

| S2         | 0  | 0  | 1  | 0  | S2'         | 1  | 1  | 0  | 1  |

| S3         | 0  | 0  | 0  | 1  | S3'         | 1  | 1  | 1  | 0  |

|            |    |    |    |    |             |    |    |    |    |

|            |    |    |    |    |             |    |    |    |    |

| S0         | 1  | 1  | 1  | 1  | S0'         | 0  | 0  | 0  | 0  |

| S1         | 0  | 0  | 1  | 1  | S1'         | 1  | 1  | 0  | 0  |

| S2         | 0  | 1  | 0  | 1  | S2'         | 1  | 0  | 1  | 0  |

| S3         | 0  | 1  | 1  | 0  | S3'         | 1  | 0  | 0  | 1  |

16 codewords for 4 symbols

| _                      | symbol           | r3               | r2               | r1               | r0               | symbol                   | r3               | r2               | r1               | r0               | _ |

|------------------------|------------------|------------------|------------------|------------------|------------------|--------------------------|------------------|------------------|------------------|------------------|---|

| ODD<br>code-<br>words  | $\mathbf{S}_{2}$ | 1<br>0<br>0<br>0 | 0<br>1<br>0<br>0 | 0<br>0<br>1<br>0 | 0<br>0<br>0<br>1 | S0'<br>S1'<br>S2'<br>S3' | 0<br>1<br>1<br>1 | 1<br>0<br>1<br>1 | 1<br>1<br>0<br>1 | 1<br>1<br>1<br>0 |   |

| EVEN<br>code-<br>words | S1               | 1<br>0<br>0<br>0 | 1<br>0<br>1<br>1 | 1<br>1<br>0<br>1 | 1<br>1<br>1<br>0 | S0'<br>S1'<br>S2'<br>S3' | 0<br>1<br>1<br>1 | 0<br>1<br>0<br>0 | 0<br>0<br>1<br>0 | 0<br>0<br>0<br>1 |   |

Code space divided into ODD and EVEN phases

| _                      | symbol | r3               | r2               | r1               | r0               | symbol                   | r3               | r2               | r1               | r0               |  |

|------------------------|--------|------------------|------------------|------------------|------------------|--------------------------|------------------|------------------|------------------|------------------|--|

| ODD<br>code-<br>words  |        | 1<br>0<br>0<br>0 | 0<br>1<br>0<br>0 | 0<br>0<br>1<br>0 | 0<br>0<br>0<br>1 | S0'<br>S1'<br>S2'<br>S3' | 0<br>1<br>1<br>1 | 1<br>0<br>1<br>1 | 1<br>1<br>0<br>1 | 1<br>1<br>1<br>0 |  |

| EVEN<br>code-<br>words | S1     | 1<br>0<br>0<br>0 | 1<br>0<br>1<br>1 | 1<br>1<br>0<br>1 | 1<br>1<br>1<br>0 | S0'<br>S1'<br>S2'<br>S3' | 0<br>1<br>1<br>1 | 0<br>1<br>0<br>0 | 0<br>0<br>1<br>0 | 0<br>0<br>0<br>1 |  |

*<u>Multicode:</u>* 2 codewords for each symbol in each phase

•

# Outline

- Introduction

- Background

- 1-of-4 LETS codes

- 1-of-N LETS codes

- Hardware support

- Analytical evaluation

25/48

Conclusions

## 1-of-N LETS Codes

### ► Goal

To extend solution for 1-of-4 LETS codes to 1-of-N

### Challenge:

- Solution is not obvious for arbitrary N

- Must satisfy several properties

- $\rightarrow$  Level-encoding: data can be extracted directly from codeword

- $\rightarrow$  Transition signaling: each symbol must reach all others via 1 flip

26/48

$\rightarrow$  alternating phase

### Contributions

- Proof: existence of legal LETS codes for every  $N = 2^n$

- Systematic procedure to generate LETS codes

- $\rightarrow$  LETS properties formulated as set of constraints

- $\rightarrow$  Constraints captured in code generator matrix

- $\rightarrow$  Many different LETS codes exist for each N

- See paper for details

## Outline

- Introduction

- Background

- 1-of-4 LETS codes

- 1-of-N LETS codes

- Hardware support

- Conversion circuit: interfacing channels to nodes

- LETS pipeline circuit: improving channel throughput

- Analytical evaluation

- Conclusions

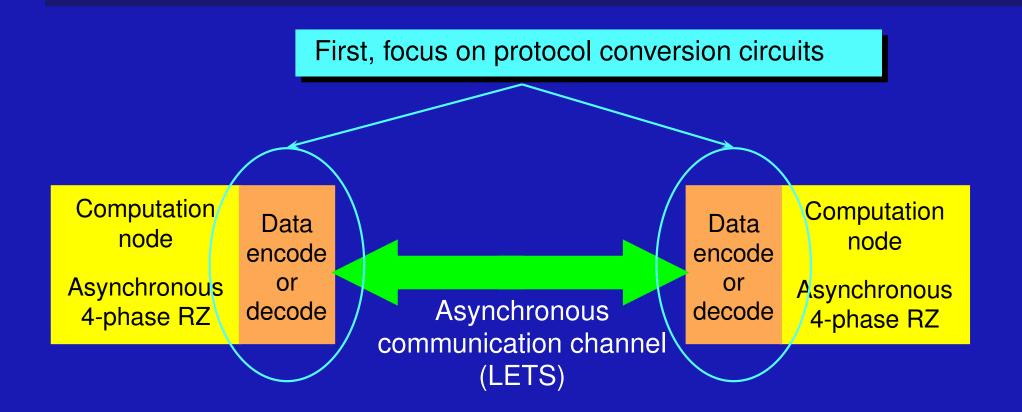

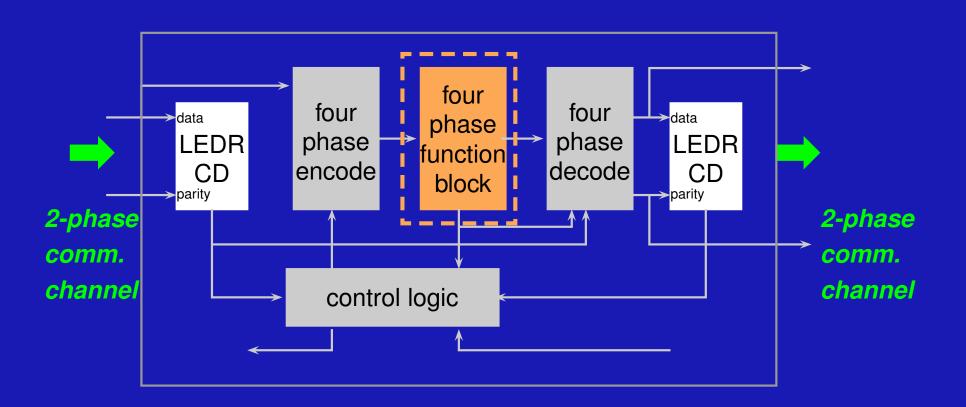

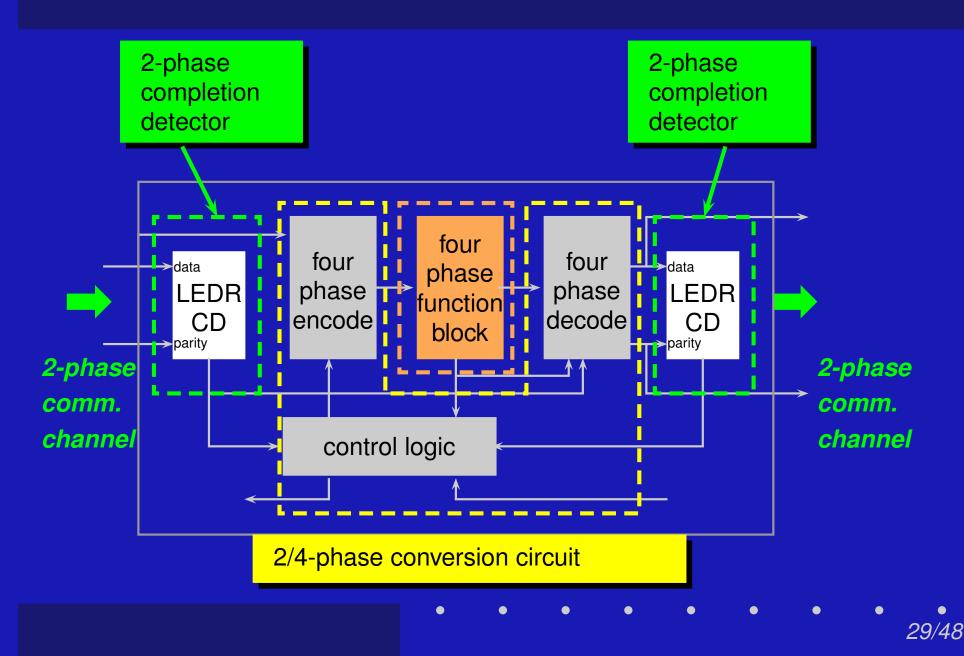

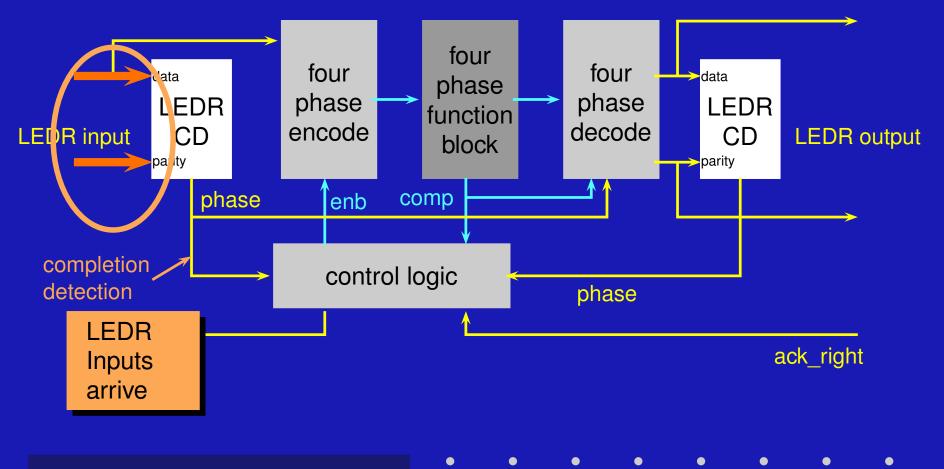

## LETS Hardware Support: Protocol Conversion

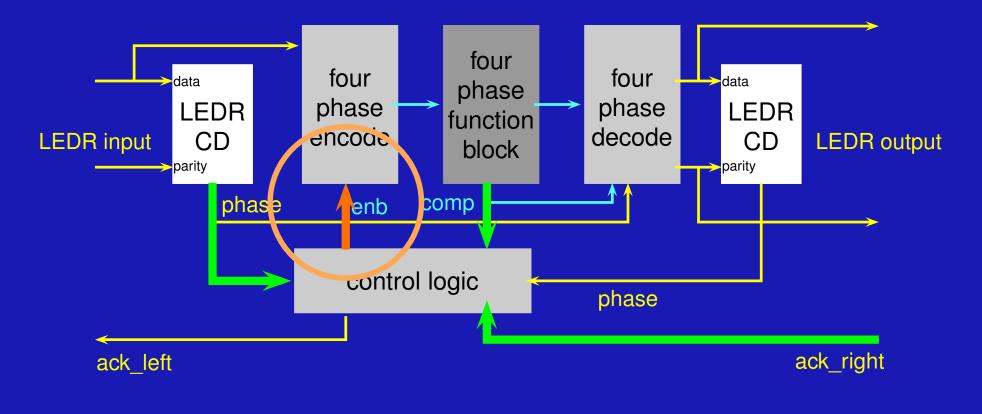

## **LEDR Converter: Prior Architecture Overview**

LEDR Converter from Mitra et al., "Efficient Asynchronous Protocol Converters for Two-Phase Delay-Insensitive Global Communication", ASYNC'07

## LEDR Converter: Prior Architecture Overview

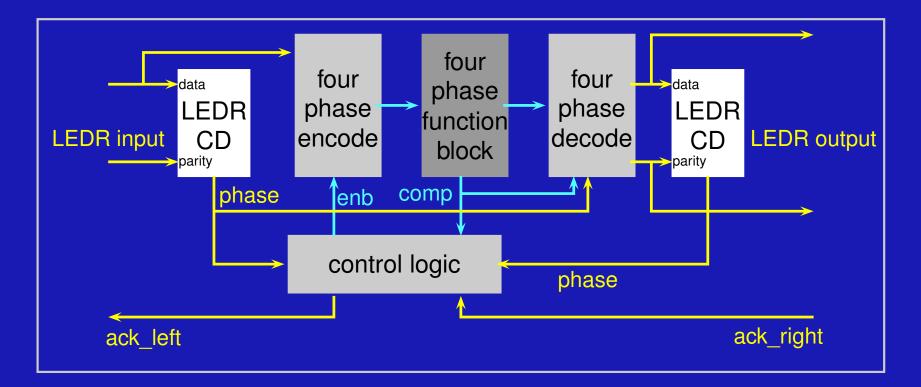

## **LEDR Converter: Control Signals**

### $\rightarrow$ four phase signals

•

$\rightarrow$  two phase signals

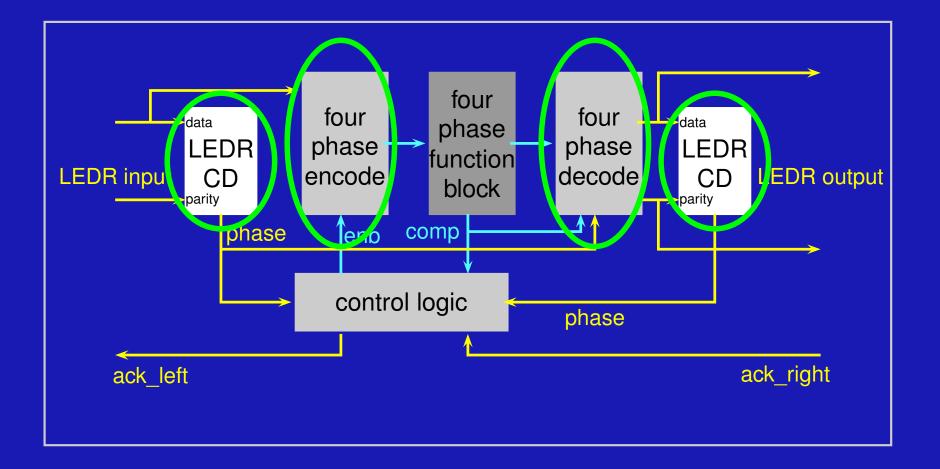

## New contribution: 1-of-4 LETS Converter

#### Based on existing LEDR (1-of-2 LETS) converter

- Only minor modifications needed

- $\rightarrow$  Same overall architecture

- $\rightarrow$  Most pieces identical

- $\rightarrow$  Internal logic of some blocks have minimal changes

.31/48

## 1-of-4 LETS Converter

•

### Changed logic blocks

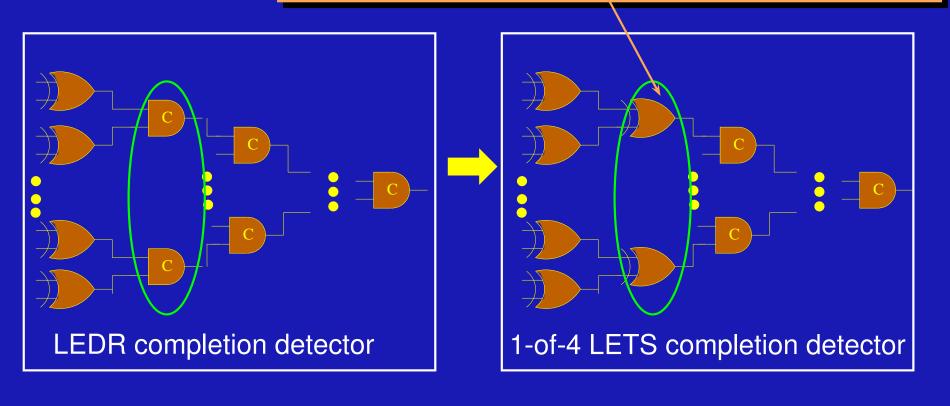

## Completion Detector: LEDR vs. 1-of-4 LETS

### - completion detector

One layer of C-elements replaced by XNOR gates

33/48

•

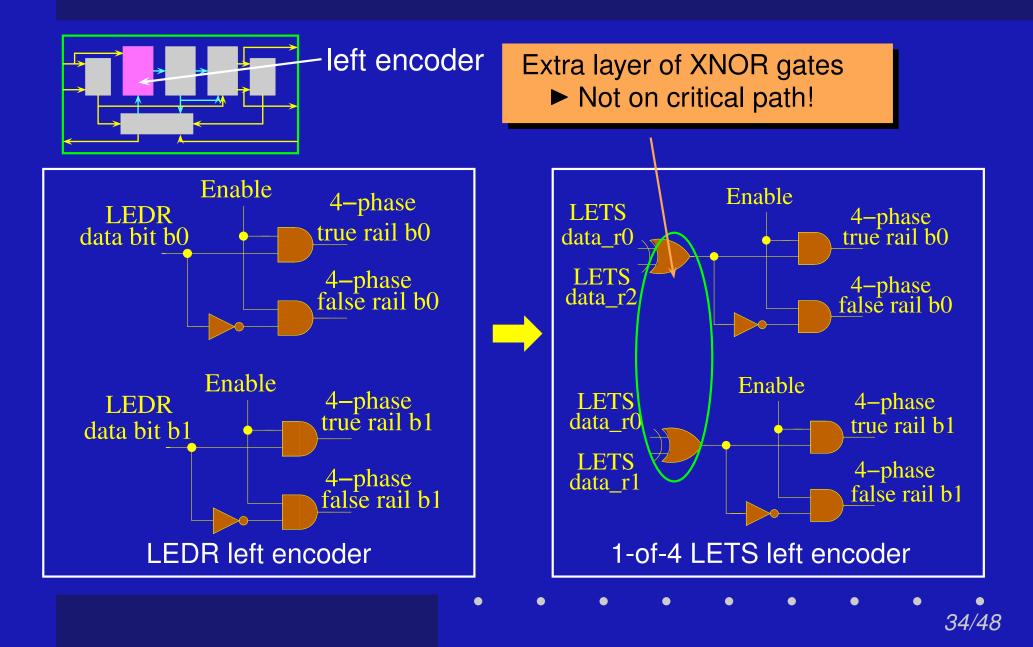

## Left Encoder: LEDR vs. 1-of-4 LETS

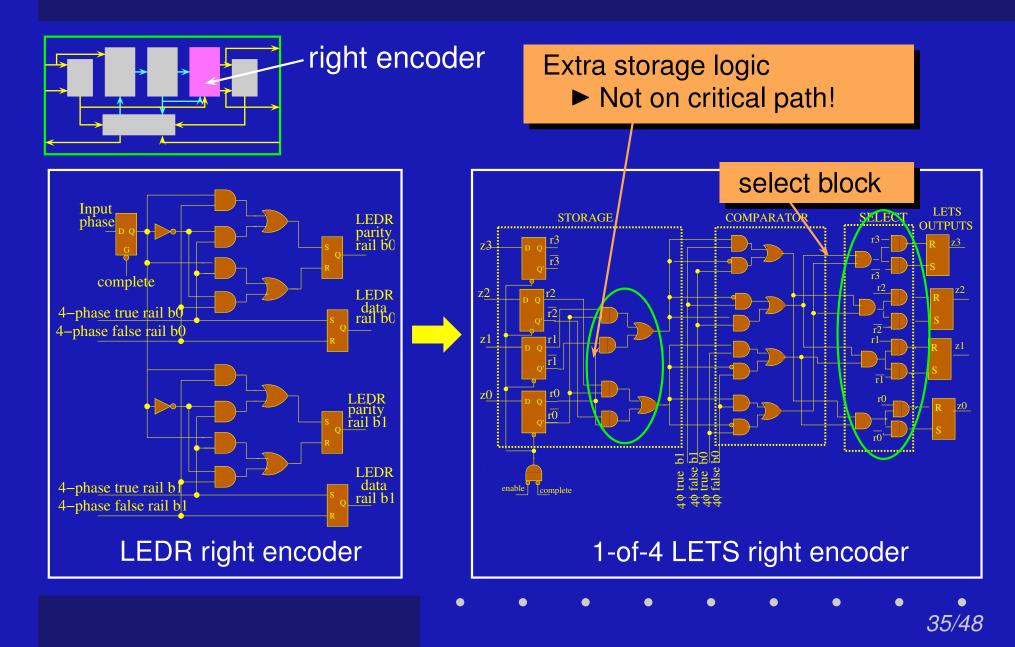

## Right Encoder: LEDR vs. 1-of-4 LETS

## 1-of-4 LETS Converter Performance Evaluation

Layout performed for LEDR (1-of-2 LETS) conversion circuits

Mitra et al., "Efficient Asynchronous Protocol Converters for Two-Phase Delay-Insensitive Global Communication", ASYNC'07

- With a 4-phase multiplier function block

- $0.18 \mu m$  TSMC CMOS process

- Summary of simulation results:

| Forward latency      | input arrival $\rightarrow$ output data available | 6.8ns  |  |

|----------------------|---------------------------------------------------|--------|--|

| Stabilization time   | input arrival $\rightarrow$ reset complete        | 10.5ns |  |

| Pipelined cycle time | min processing time / data item (steady state)    | 8.3ns  |  |

36/4

1-of-4 LETS expected to add 15 - 20% overhead

#### Design is delay-insensitive

$\rightarrow$  Except for two simple one-sided timing constraints

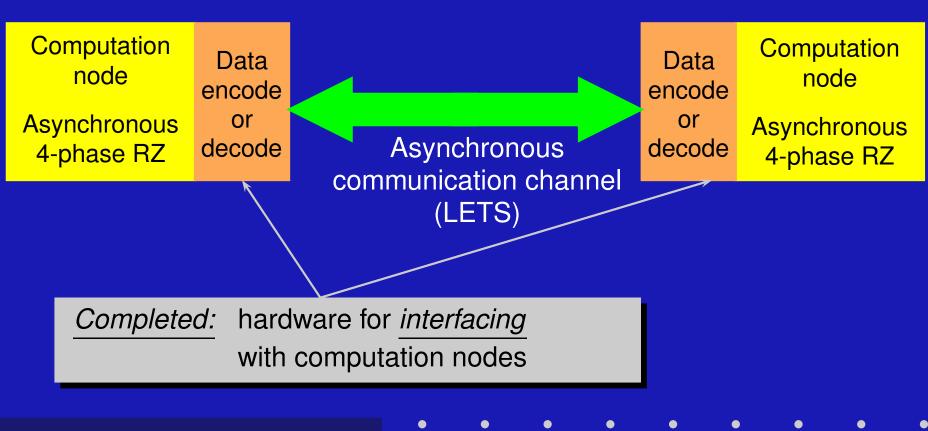

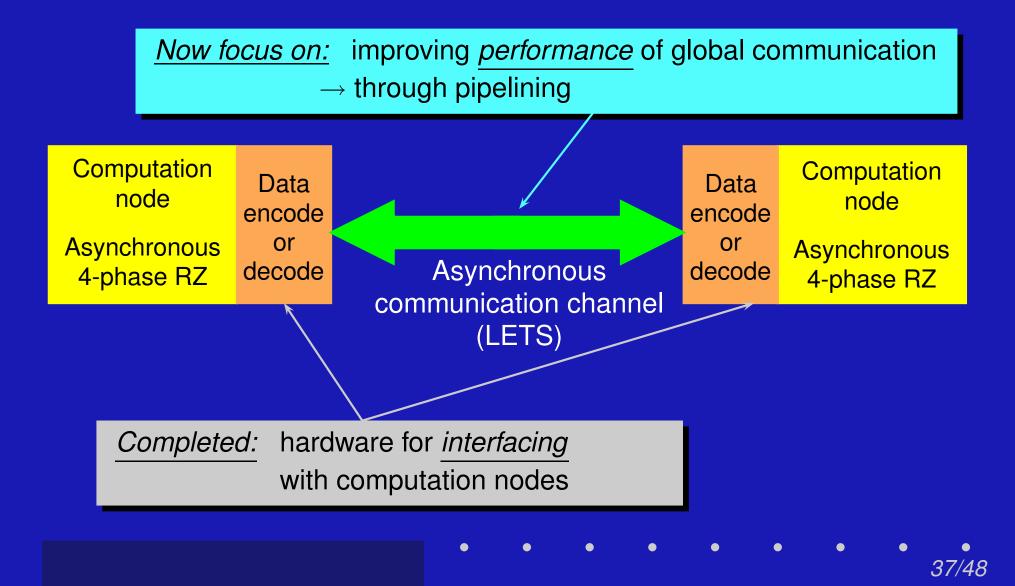

## **LETS Hardware Support: Pipelining Channels**

## **LETS Hardware Support: Pipelining Channels**

## **LETS Pipeline: Improving Channel Throughput**

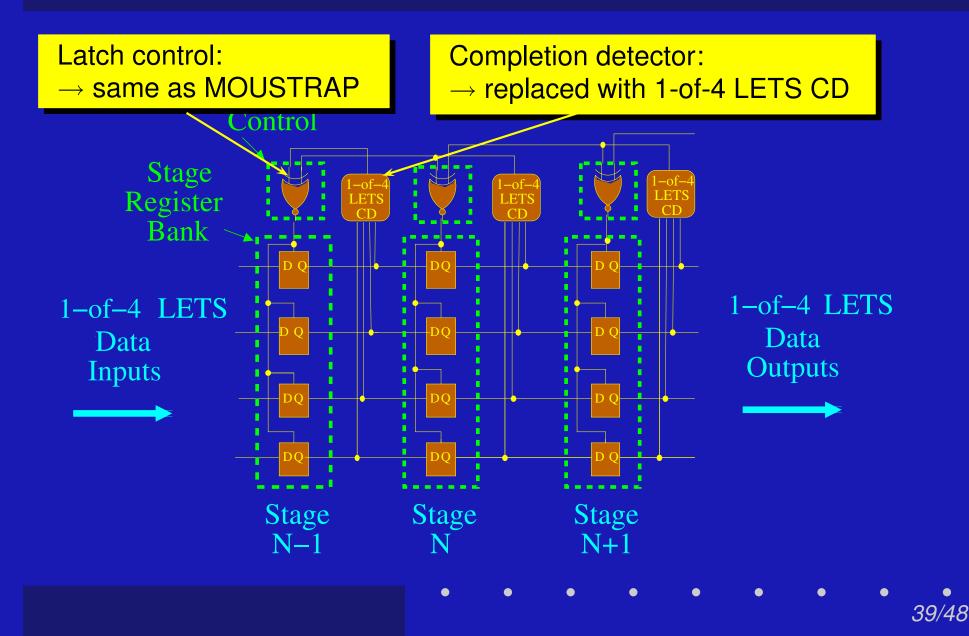

#### Support #1: MOUSETRAP-based design

Singh & Nowick, "MOUSETRAP: High-Speed Transition Signaling Asynchronous Pipelines", TVLSI'07

- Original MOUSETRAP pipeline

- $\rightarrow$  High-speed pipeline scheme for <u>bundled-data</u> encoding

- Proposed design

- $\rightarrow$  Pipelines DI communication channel based on MOUSETRAP

- $\rightarrow$  Eliminates MOUSETRAP bundled-data timing requirements

- $\rightarrow$  only retains one simple 1-sided timing constraint

- Simple hardware design

#### Support #2: LEDR-based design

Dean et al., "Efficient Self-Timing with Level-Encoded 2-Phase Dual-Rail (LEDR)", Proc. of UCSC Conf. on Adv. Research in VLSI, '91

38/48

• Timing-robust approach, see paper for details

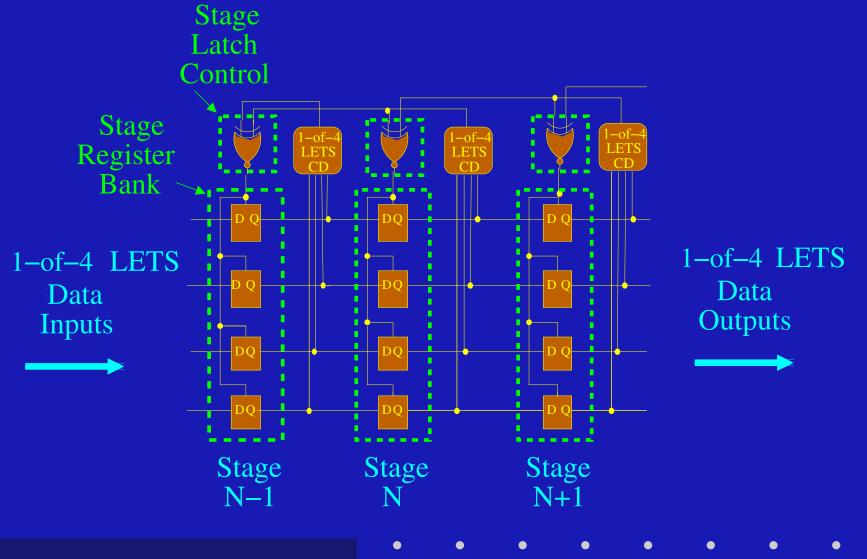

## 1-of-4 LETS Pipeline: MOUSETRAP-based design

•

## 1-of-4 LETS Pipeline: MOUSETRAP-based design

## Outline

- Introduction

- Background

- 1-of-4 LETS codes

- 1-of-N LETS codes

- Hardware support

- Analytical evaluation

- Coding efficiency and transition power metric

40/48

Conclusions

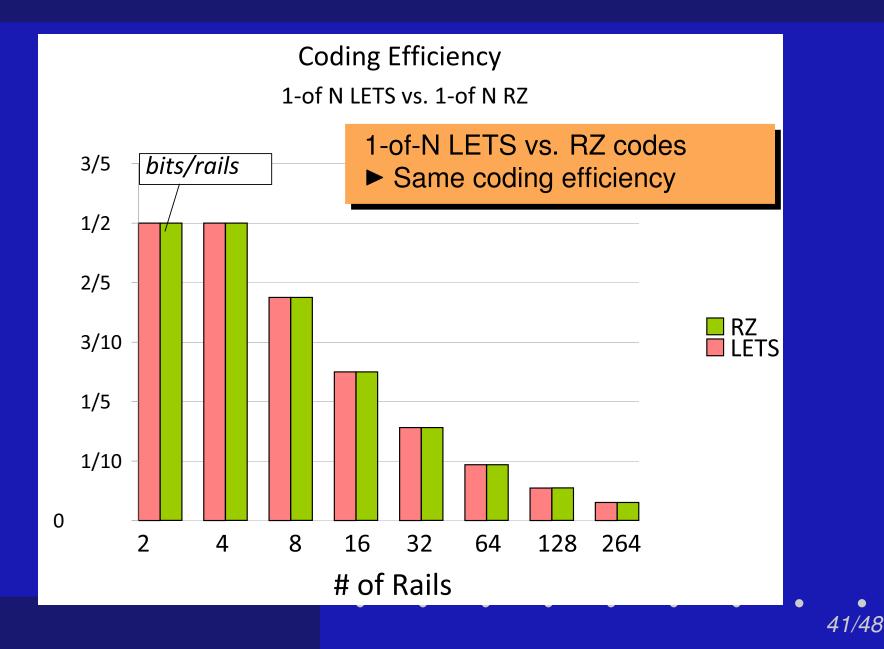

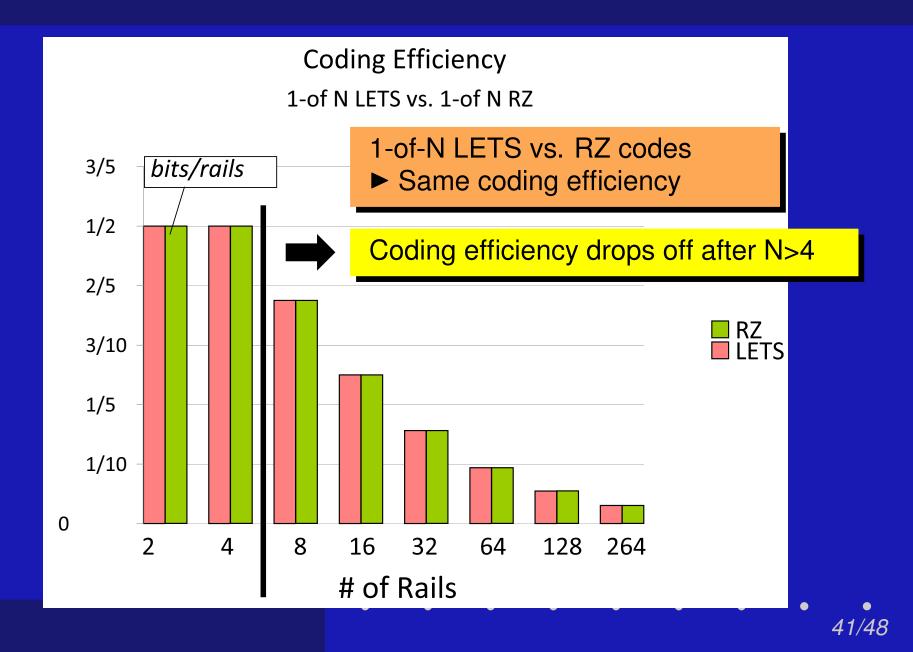

### Analytical Evaluation: Coding Efficiency (LETS vs. RZ)

•

### Analytical Evaluation: Coding Efficiency (LETS vs. RZ)

•

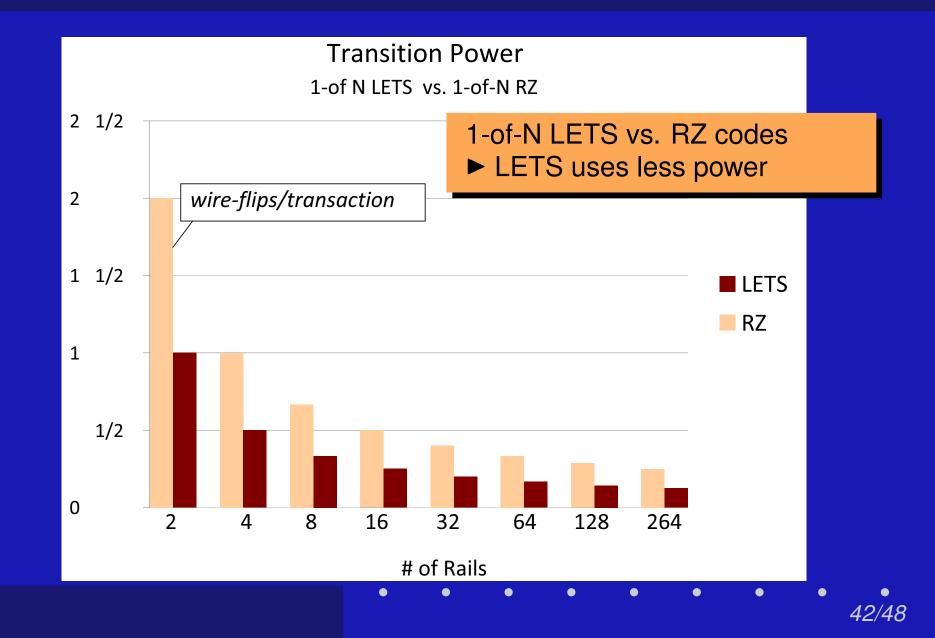

### Analytical Evaluation: Transition Power (LETS vs. RZ)

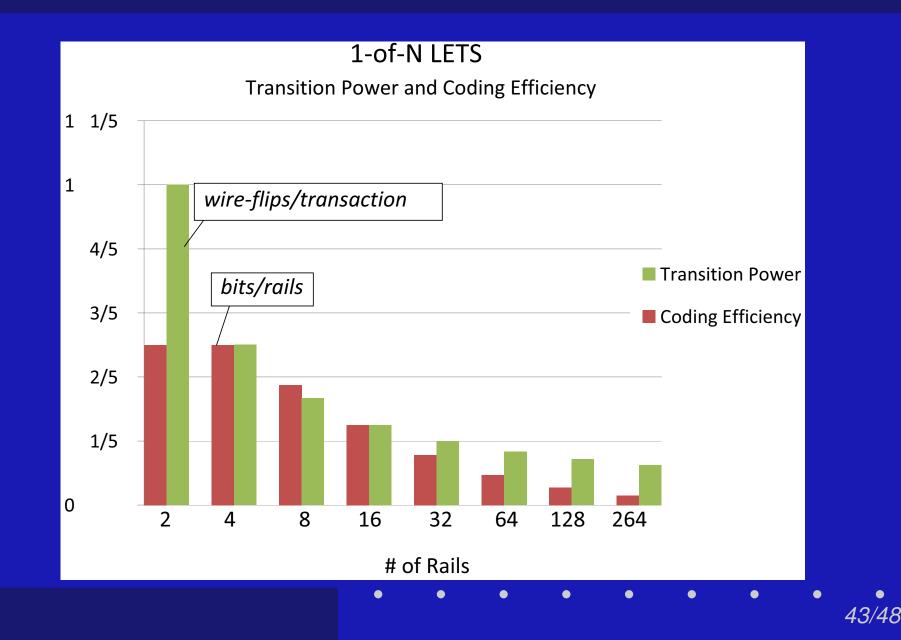

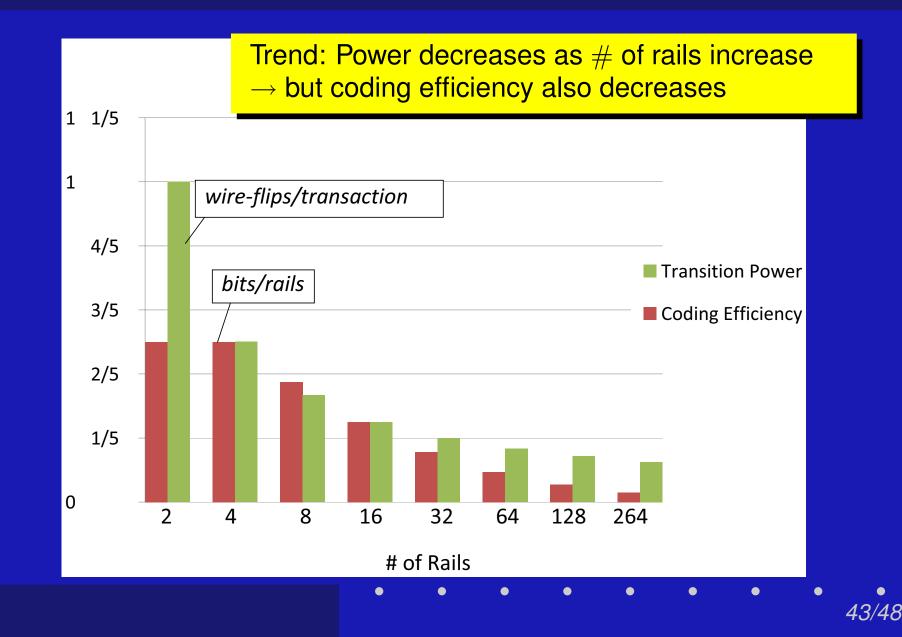

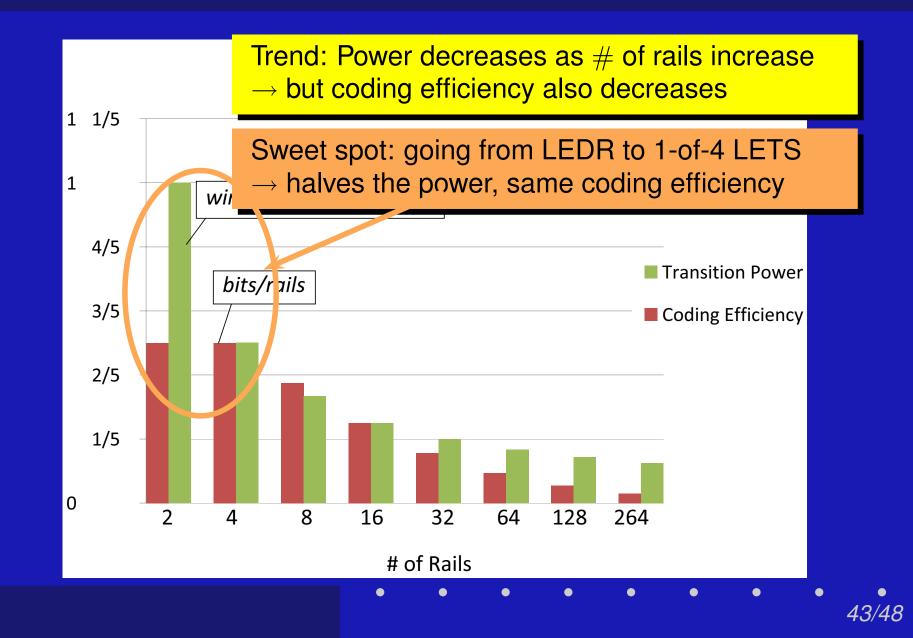

### Analytical Evaluation: Interpreting LETS Scaling

•

### Analytical Evaluation: Interpreting LETS Scaling

### Analytical Evaluation: Interpreting LETS Scaling

### Analytical Evaluation: LETS vs. Synchronous

Coding efficiency (# bits encoded/wire)

- Synchronous better than 1-of-N LETS

- $\rightarrow$  Synchronous: N bits for N wires

- $\rightarrow$  1-of-N LETS: log N bits for N wires

Transition power metric (# transitions/wire/data transaction)

- 1-of-N LETS better than synchronous as N increases

- → Synchronous: constant

- $\rightarrow$  assumes equal probability of wire transition

- $\rightarrow$  1-of-N LETS: decreases as N grows  $\rightarrow = 1 / \log N$

- $\rightarrow$  Transition power metric same for N = 4

# Conclusions

#### A new class of delay-insensitive codes "Level-Encoded Transition Signaling (LETS)"

- High throughput, low power for global communication

- Two example 1-of-4 LETS codes shown

- Generalization to 1-of-N LETS

- $\rightarrow$  first 1-of-N level-encoded transition signaling scheme

#### Efficient hardware

- For protocol conversion to/from four-phase dual-rail signaling

- For pipelining global communication channel

### Power and throughput improvements over existing codes

• Demonstrated via analytical evaluation

## **Future Work**

Better evaluation of performance/power metrics

- Layout of proposed circuits

- Evaluation of second-order effects

- $\rightarrow$  e.g. cross-coupling, noise, etc

Extend conversion circuits to support other encoding styles

46/48

• e.g. 1-of-4 RZ, single-rail bundled

- •

- •

### Appendix

• 47/48

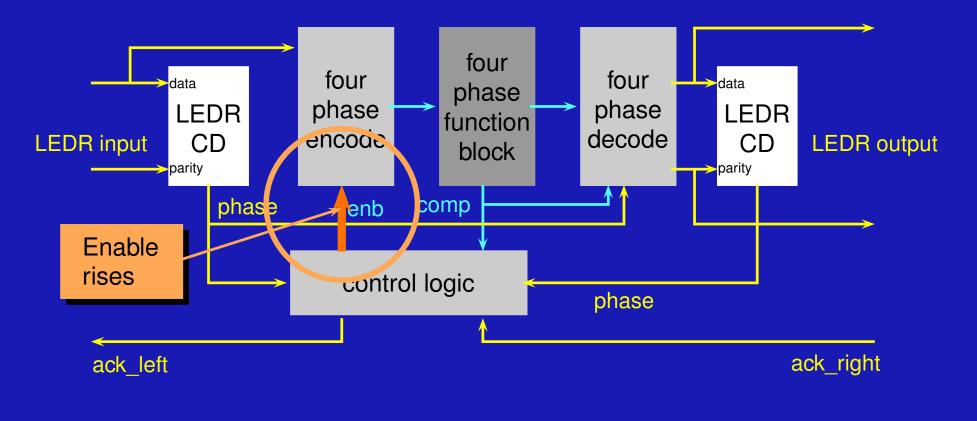

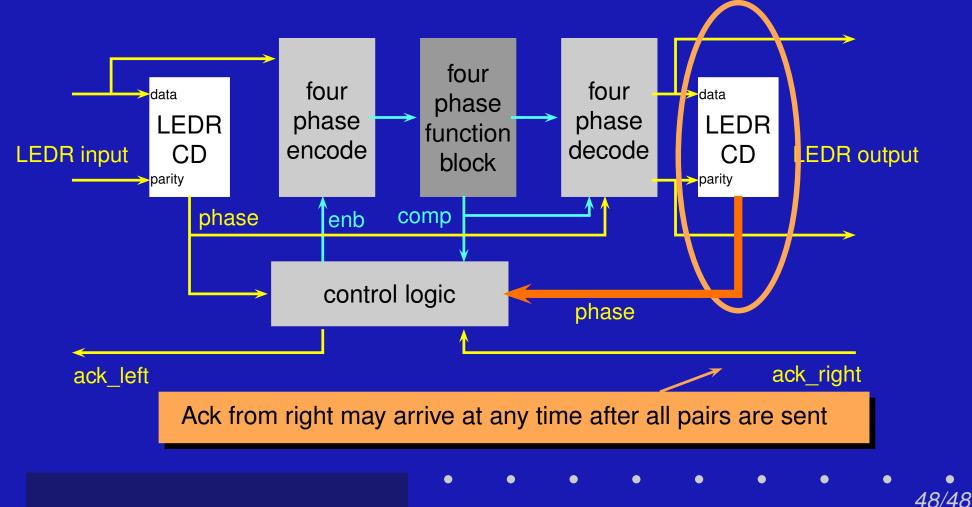

### Step 1: Two-phase inputs arrive

•

LEDR inputs begin arriving at quiescent system

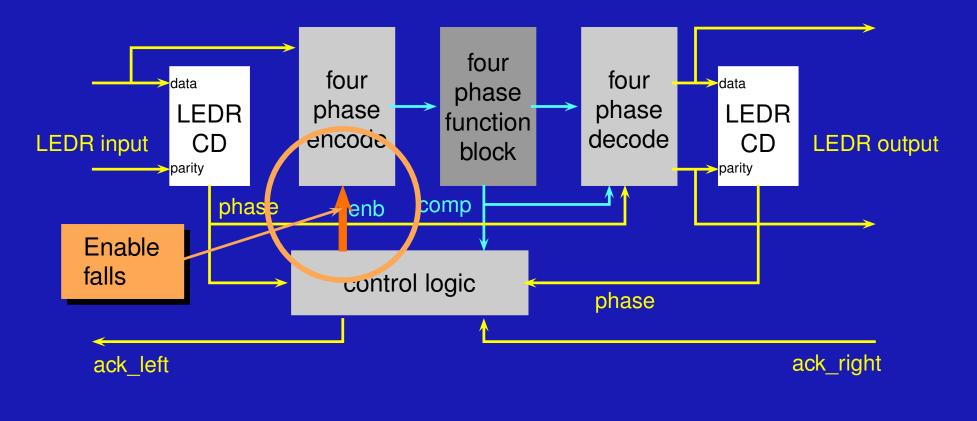

### Step 2: Two-to-four phase conversion

•

#### Input completion detection sent to control

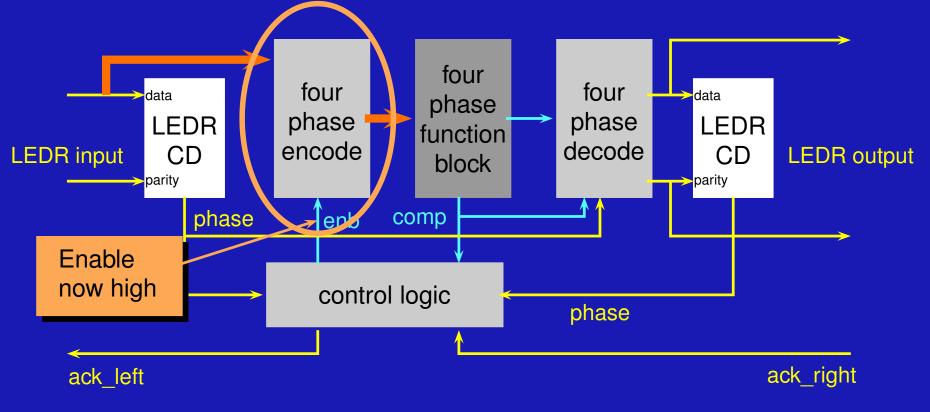

### Step 2: Two-to-four phase conversion

•

Control enables four-phase evaluate phase

### Step 2: Two-to-four phase conversion

•

LEDR input converted to four-phase

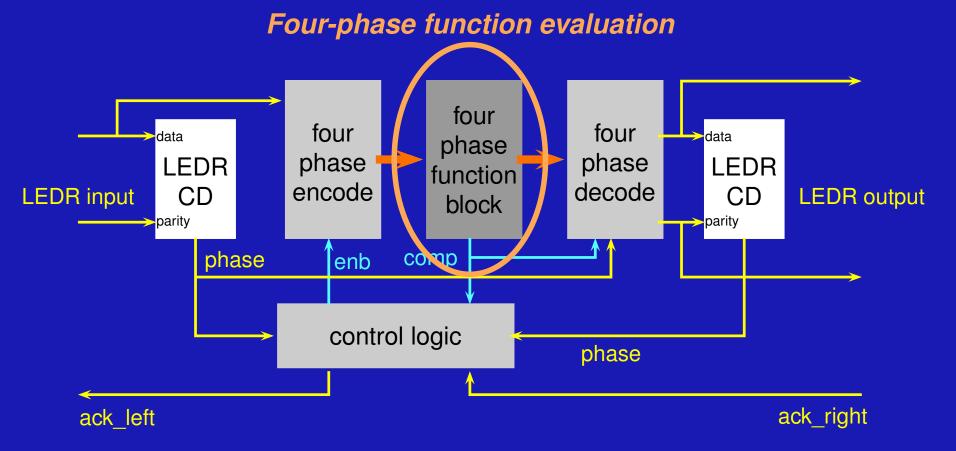

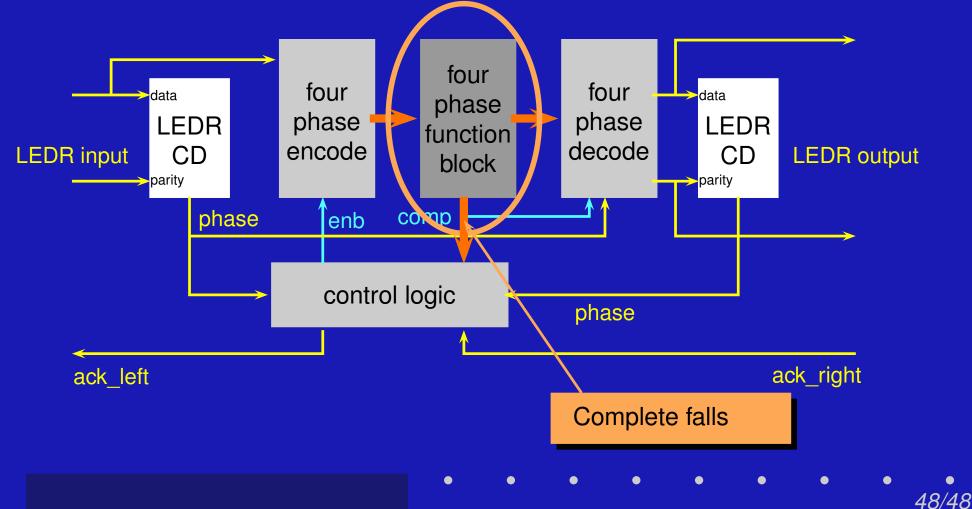

### Step 3: Four-phase evaluate

48/48

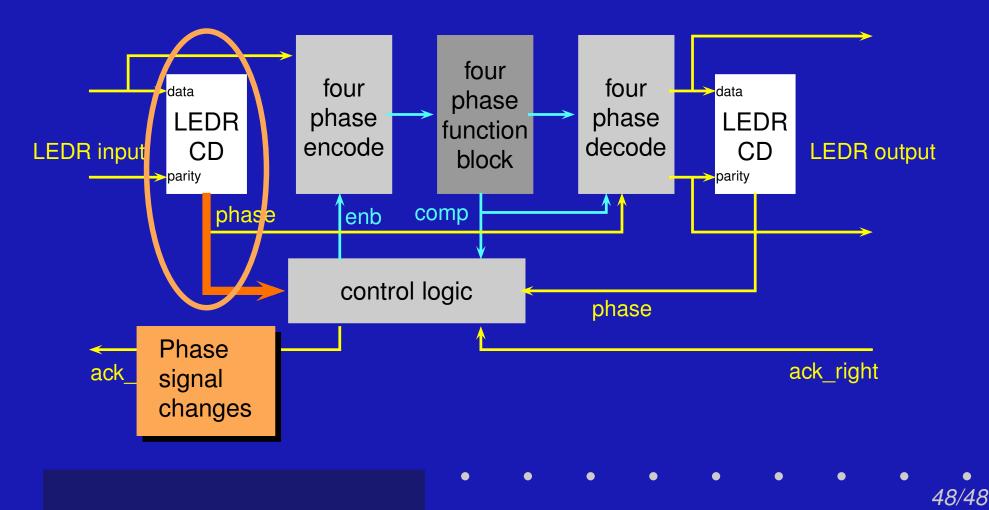

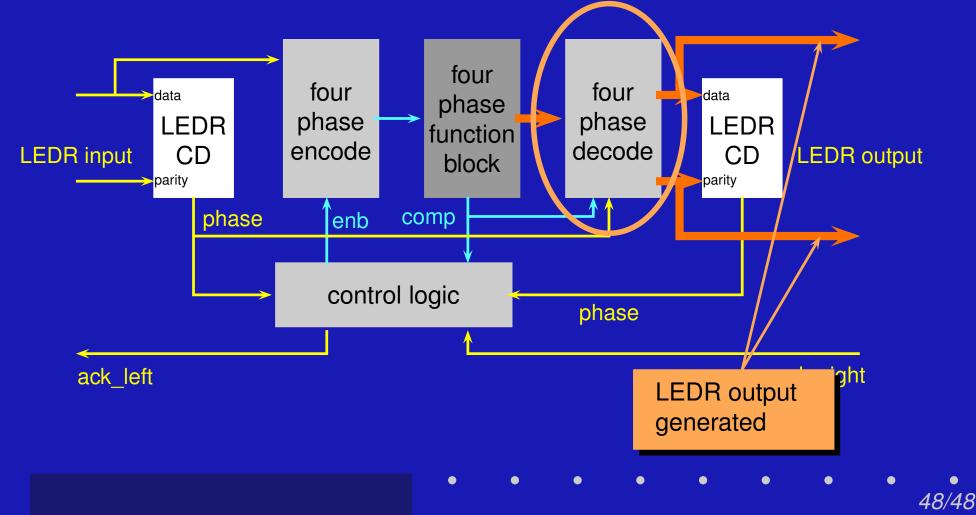

### Step 4: Four-to-two phase conversion

•

Four-phase bits decoded to LEDR

## Step 4: Four-to-two phase conversion

LEDR output completion detection

•

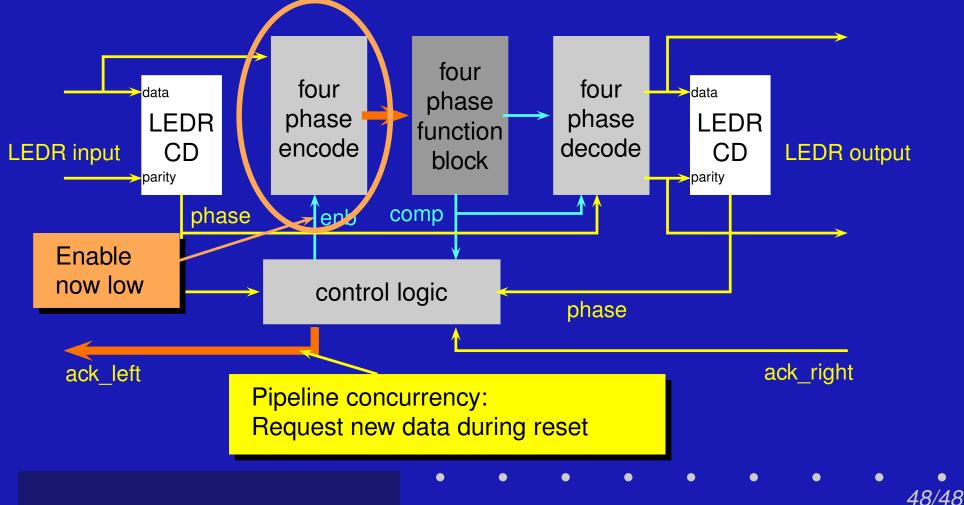

### Step 5: Four-phase reset

•

### Control enables four-phase reset phase

### Step 5: Four-phase reset

#### Step 5: Four-phase reset

•

Four-phase reset propagates through logic block

### Ready to evaluate again

•

### New evaluate phase begins when enable rises again