## Potential impact of emerging System-in-Package technologies on system design

### Eric Beyne IMEC

## Workshop W2 - Date2006

Future interconnects and networks on chip

#### March 10, 2006

ICM Munich, Germany

**IMEC**NOLOGY

© imec 2006

#### Strategy drivers High Density Interconnection and Packaging

- IC technology roadmaps: "System on chip", SOC

- "Vertical scaling" :

- Density: High I/O density (more I/O's on smaller area) High speed (digital & rf), high power density

- New materials: Cu/low k

- "Horizontal scaling": Divergence among Si-technologies : specific technologies for Logic, Memory, mixed-signal, analog, rf, high voltage, high power,... + MEMS

- System roadmaps: "System-in-a-Package", SIP

- One system = multiple die : "Horizontal scaling"

- Systems consist of many non-silicon components : Passives, Displays, sensors, antennas, connectors, …

System-in-a-Package", SIP = Multiple components on a high density interconnect substrate, realizing a (sub)-system function

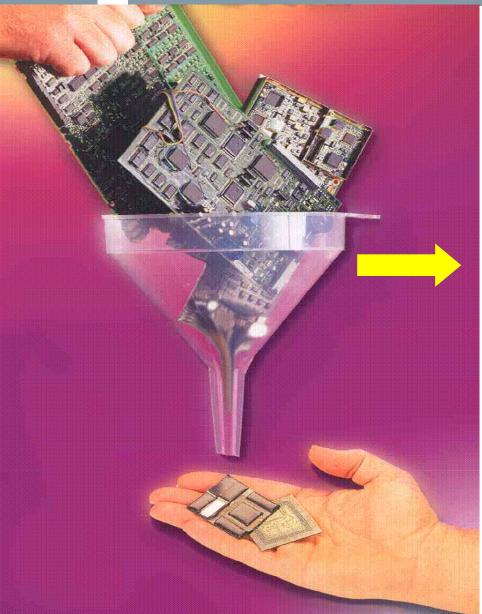

## **Miniaturisation of Electronic Systems**

#### **Enabling Technologies :**

- Si-integration : SOC

- High Density Interconnection technologies

SIP – "System-in-a-package"

#### Today :

"small PCB design" : adapted PCB design tools, traditional design flow. IC's and net list fully defined before the actual SIP design.

Limitations :

- No system-level optimization

- Complex wiring schemes

Values passive components not optimum for SIP implementation

....

Required :

#### **Chip-package co-design**

Examples :

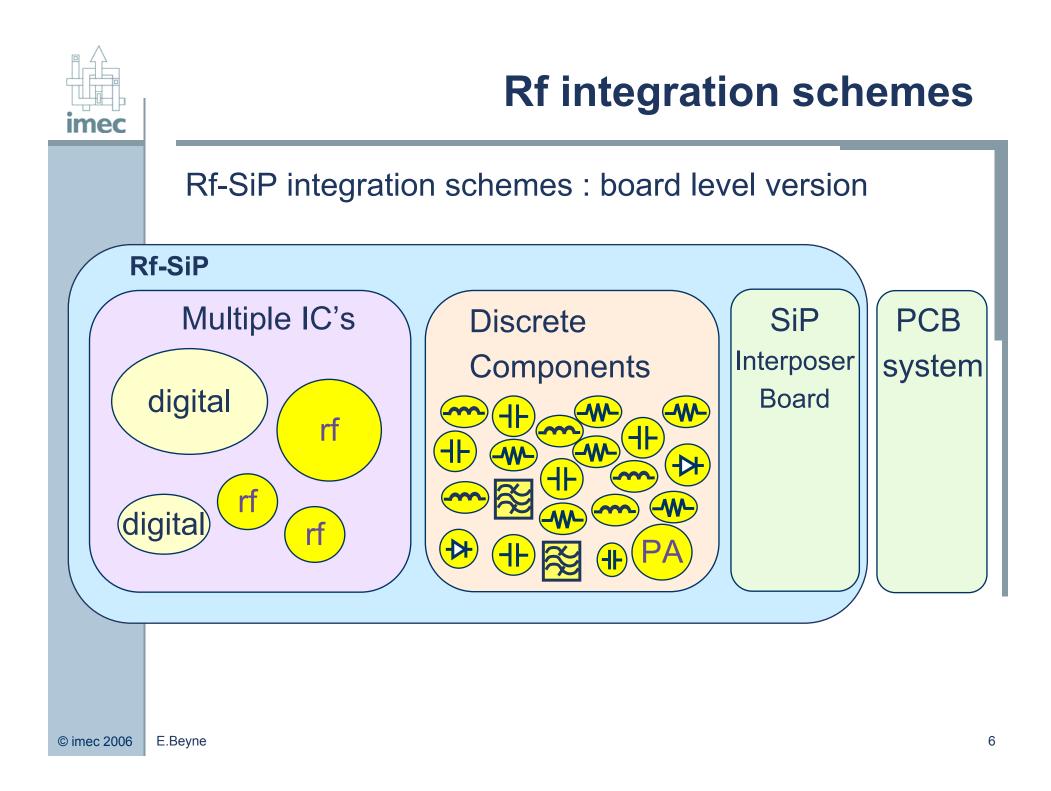

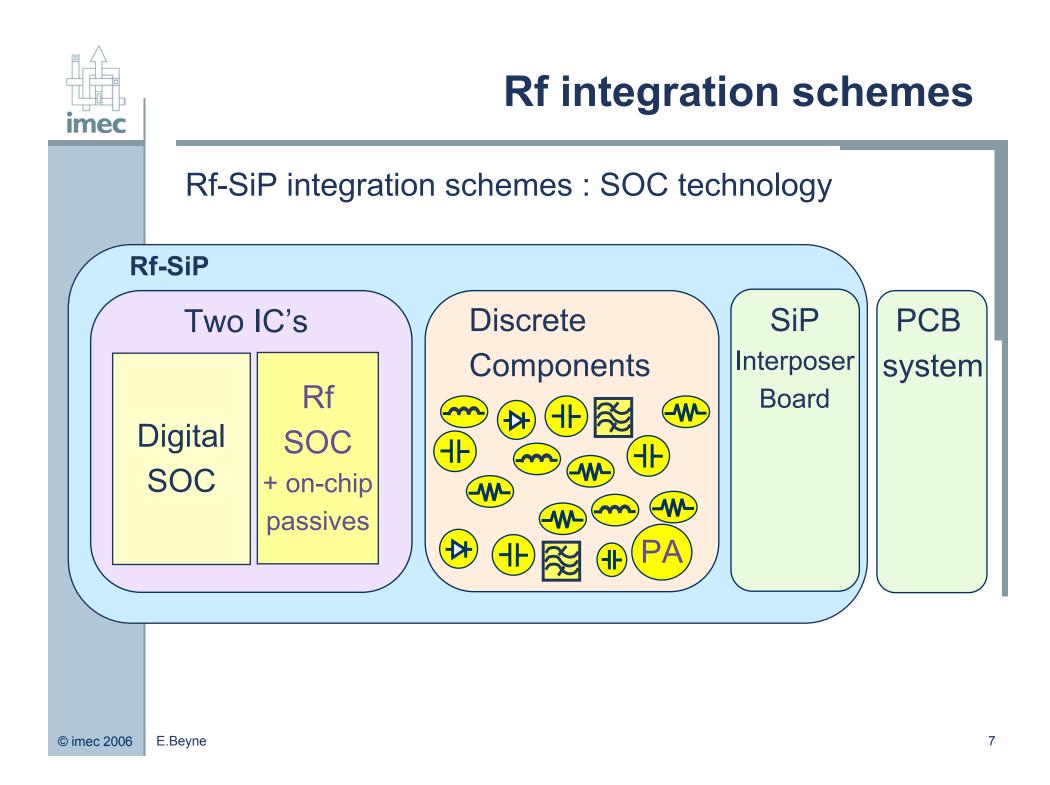

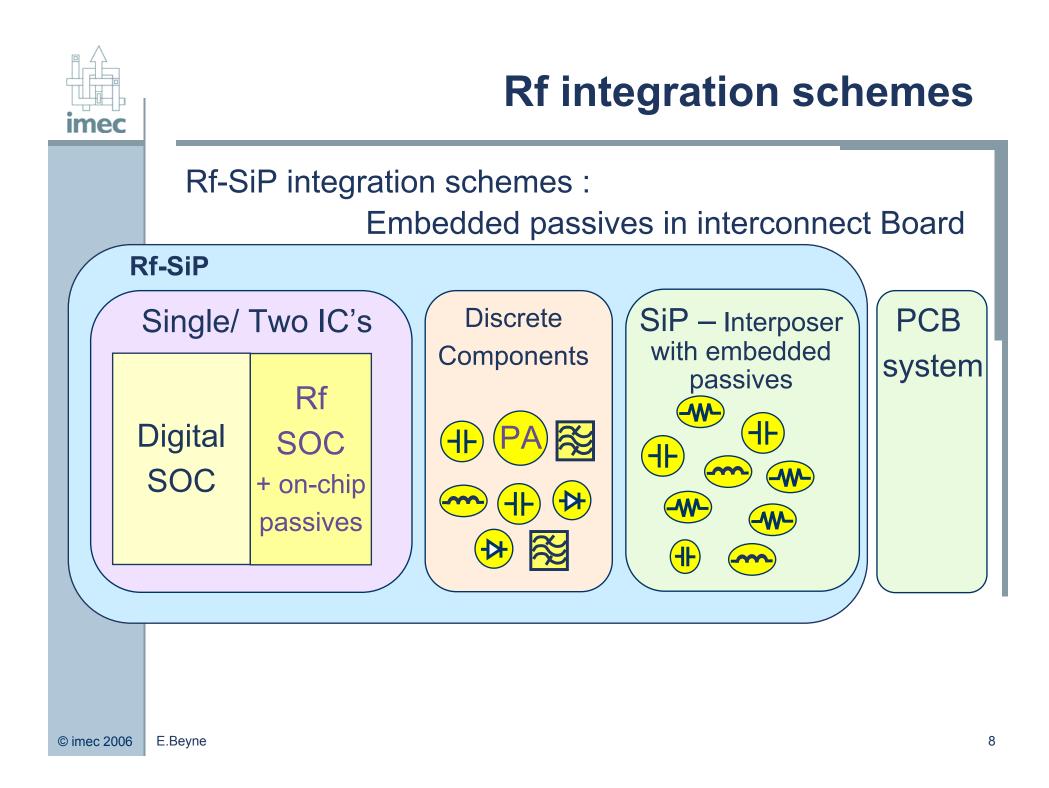

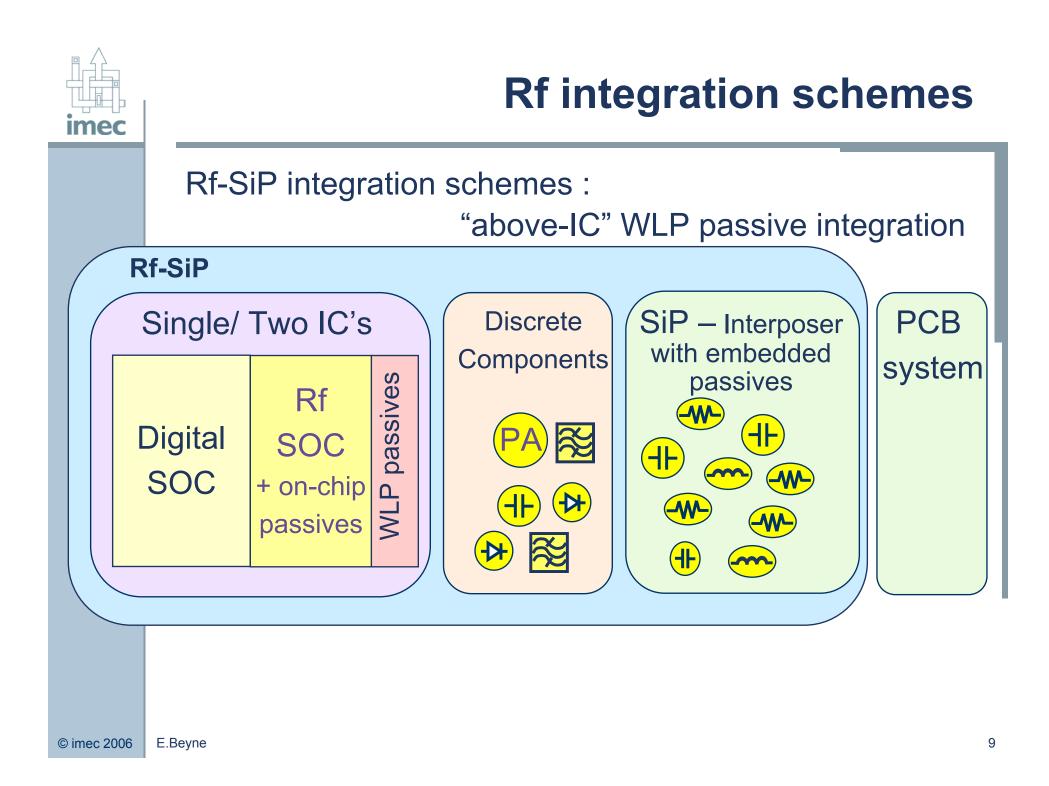

∎rf-SIP

3D stacked SIP

3D stacked IC's

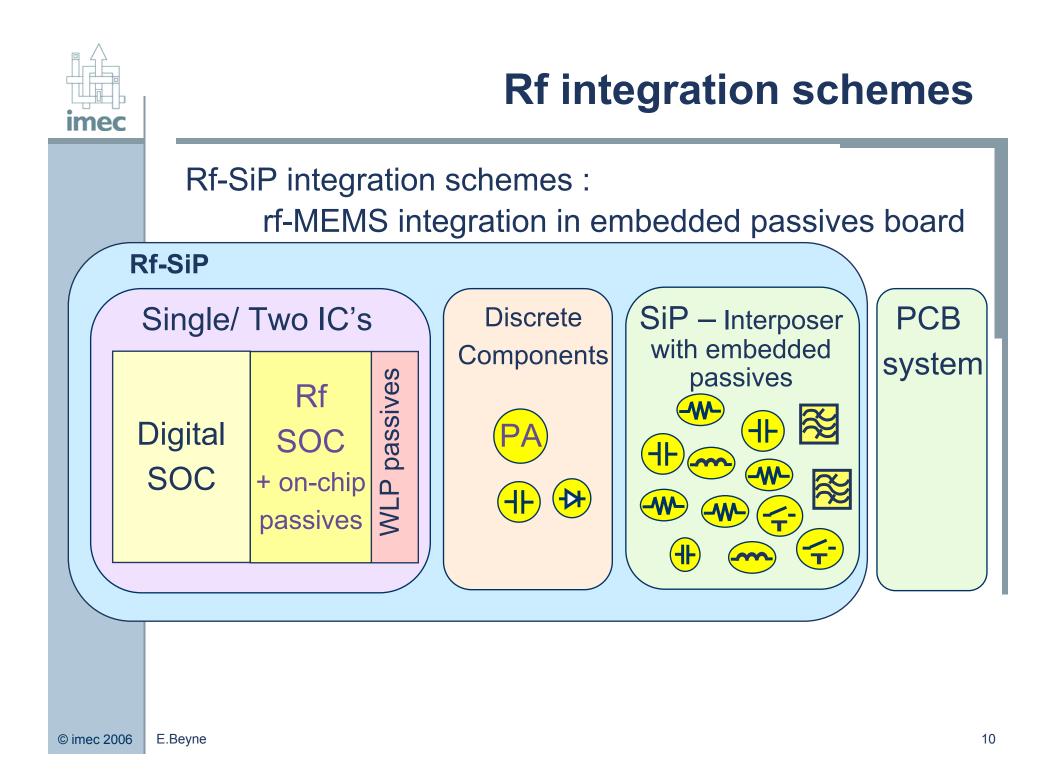

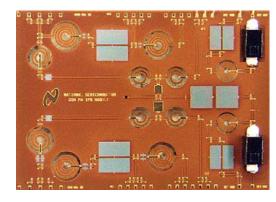

## **Technology requirements for rf-SiP**

# Integration of passive components in the SiP interconnect substrate

Which technology to choose?

- Laminate based : PCB, flex

- Ceramic based, low temperature cofired ceramic, LTCC

- Thin film lithography based

Use of different technologies together?

Partial integration on the rf- chip?

▲ Partitioning of the system is key !!

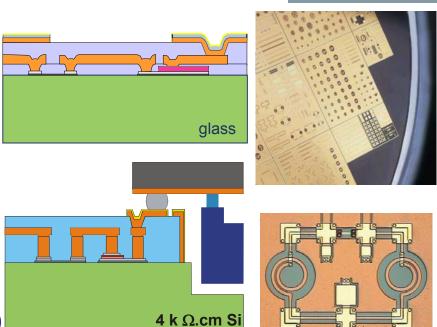

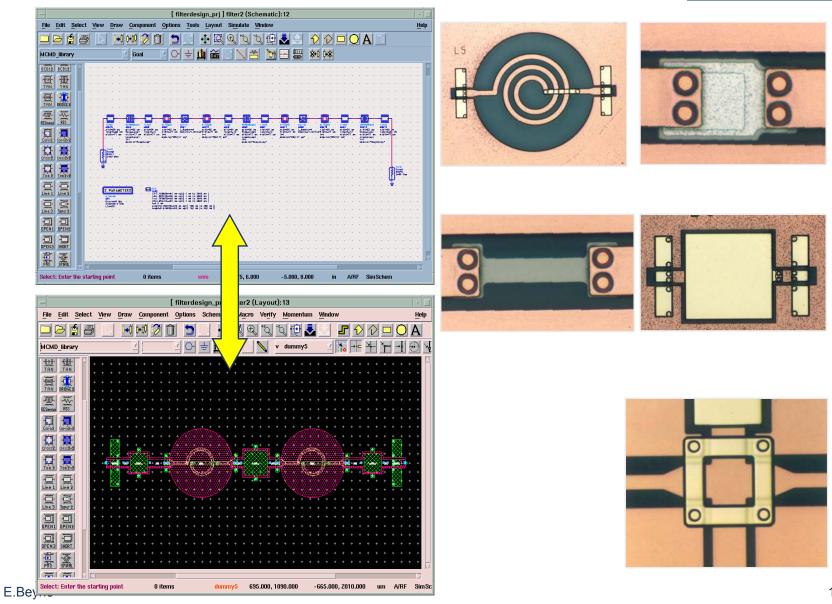

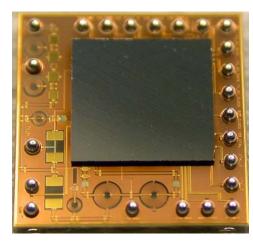

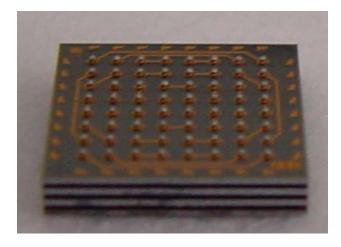

## SIP Interposer Technology with Integrated Passives

#### Multilayer thin film offers:

- Wafer-level Processing

- Photo-lithography defined features:

- Excellent control over lateral dimensions

- High repeatability

- High degree of miniaturization

- Thin film deposited resistor & dielectric layers:

- High density

- High precision, repeatable, small tolerances

- MMIC design style possible

Substrate choice:

- AF45 Glass

- HR-Si : thermal advantages, Micro-machining capabilities (cavities, through-hole vias)

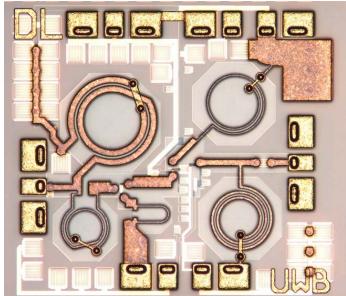

### **Multilayer Thin Film with Integrated Passives**

#### Main features :

- Coplanar and microstrip lines

- **■Electroplated Cu lines (3-5 µm)**

- BCB dielectric layers

- ■Resistors : TaN (25 Ω/□),

- ■Capacitors : Ta<sub>2</sub>O<sub>5</sub> (0.72 nF/mm<sup>2</sup>) & BCB (6.5 pF/ mm<sup>2</sup>)

- Al resistor and capacitor contacts

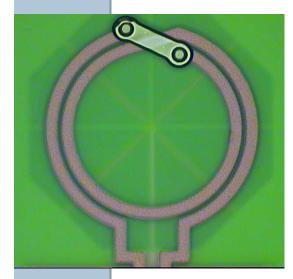

- ■Inductors : up to 80 nH, Q : 30-150

© imec 2006

## Multilayer thin film with integrated passives

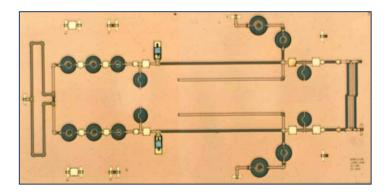

#### Multilayer thin film with integrated passives Circuit implementations examples

Integrated Passive device multiband cell phone Amplifier

RF section WLAN receiver - 5.2 GHz With integrated antenna BGA package

Sub-harmonic QPSK modulator LO @ 7 GHz, RF @ 14 GHz

## **High Q on chip Inductors**

Main Limitations on chip Inductors :

High resistivity conductors (low L/R)

High loss in silicon substrate

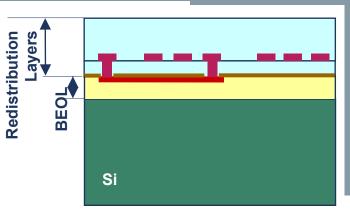

"Above-IC" processing inductors using multilayer thin film technology:

Thick Cu (up to 10 μm) : high L/R

Larger distance to the Si-substrate: lower substrate losses and lower parasitic capacitances

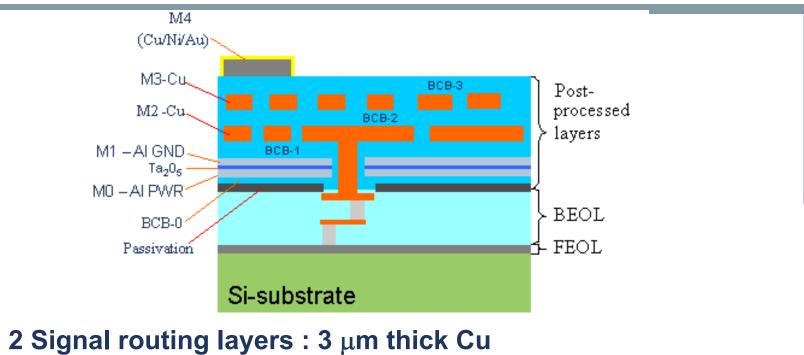

#### "Above IC" high speed digital interconnect routing using multilayer thin film technology

- Low-k BCB ILD ( $\varepsilon_r = 2.65$ ) : 5  $\mu$ m thick

- BCB-0 only in Multi project Wafers : 1 μm thick

- Low impedance Power and Ground planes :

- 1  $\mu$ m thick Al

- High-k dielectric  $Ta_20_5$  ( $\varepsilon_r = 25$ ) : 100nm thick, resulting in a 1nF/mm<sup>2</sup> decoupling capacitor (scalable to 10nF/mm<sup>2</sup>)

E.Beyne Contact pads in M4

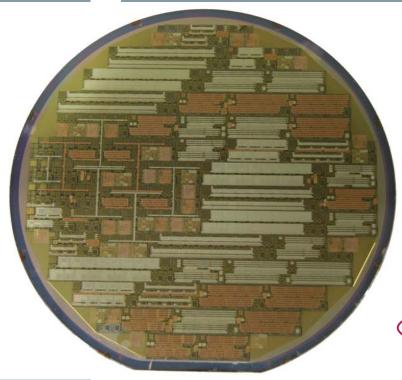

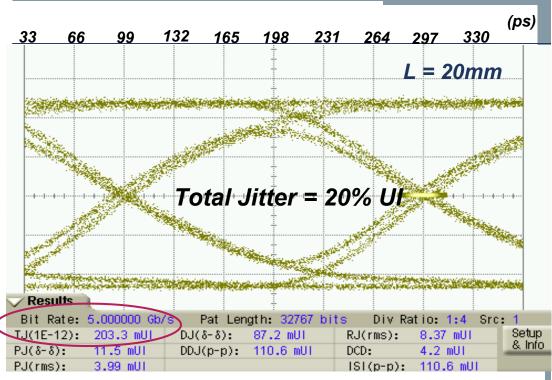

## Differential driver-receiver achieves bit rate of 5Gbps on 0.35 µm CMOS

"above-IC" post processing

0n Europractice AMIS

0.35 μm CMOS MPC wafer

- 80% Eye opening @ 5Gbps

- *Low power:* 26.4mW → 5.3pJ @ 5 Gbps

- Similar results for microstrip and IMPS

Required :

#### Chip-package co-design

Examples :

∎rf-SIP

3D stacked SIP

3D stacked IC's

© imec 2006 E.Beyne

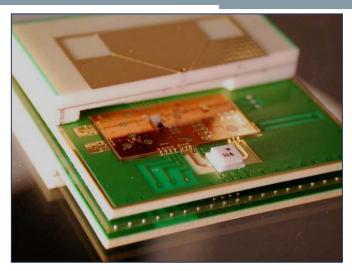

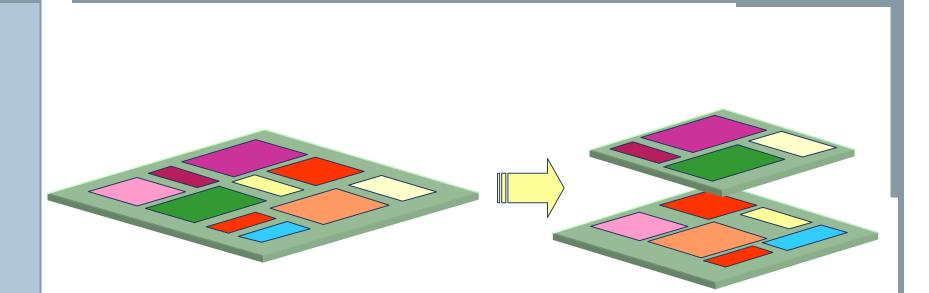

## **3D Integration technologies**

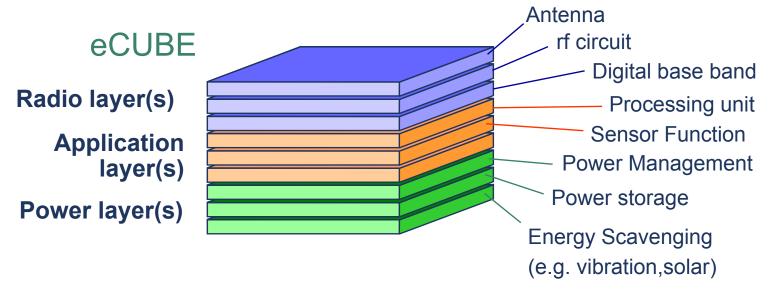

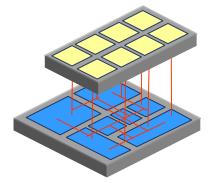

#### 3D-SIP

- Stacking of SIP sub-systems

- Most generic type

- Best yield and manufacturability

- Relatively low 3D interconnectivity

- Testability of separate layers

- Realisation of "e-Cubes"

## Wireless 3D Stack IMEC'S human++ Program

#### 1cm<sup>3</sup> EEG/ECG SIP

© imec 2006 E.Beyne / Human ++

imec

Required :

#### **Chip-package co-design**

Examples :

∎rf-SIP

■3D stacked SIP

3D stacked IC's

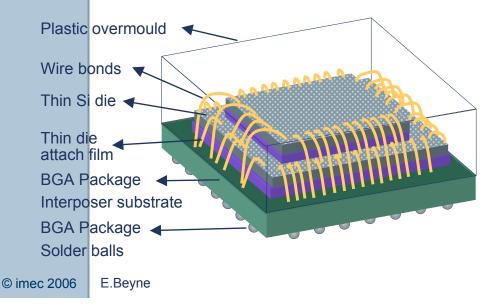

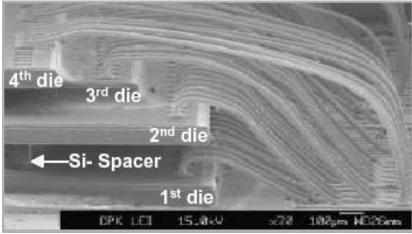

## **3D packaging technology today**

#### Stacked-die packages:

Assembly by wire bonding of stacked die in a single package High volume, mainly: portable phone application: various types of memory on cell-phone processor chips Technology :

#### standard wire-bond packaging technology

23

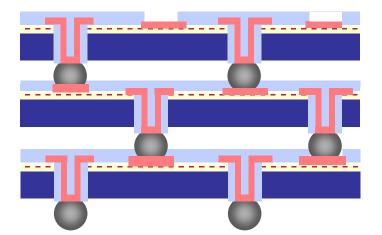

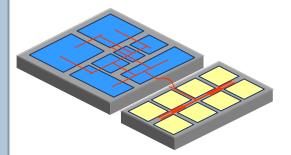

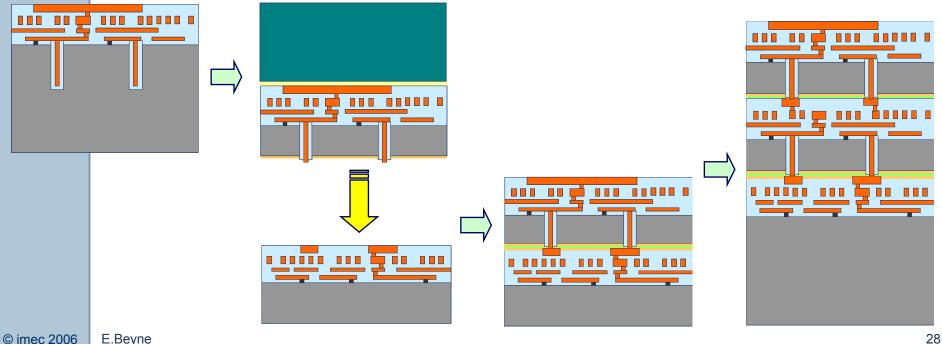

## **3D-IC-stacking**

Si-Through-hole and flip chip die-to-die bonding : Interconnects between die at the bond-pad level

High density 3D-technology opportunity:

- 3D is not limited to connecting the I/O bond-pads of different die.

- It is also possibility to interconnect functional blocks ("tiles") on a die to other tiles on other die: Interconnect at the Global on-chip interconnect level

This results in a considerably higher I/O

interconnect requirement

If the functional "tiles" on the chip could be stacked in the 3rd dimensions, the chip area would be reduced, resulting in much shorter global interconnect lines.

2D interconnect: Long lines shared bus

SOC solution: Large die

Large size Memory cells

3D interconnect Short, direct lines

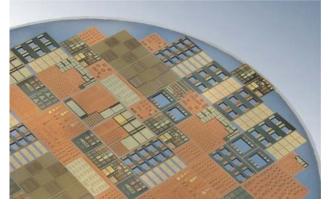

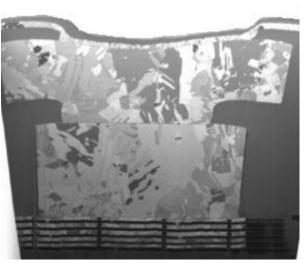

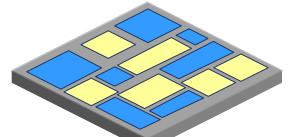

## **IMEC's 3D-SIC** approach

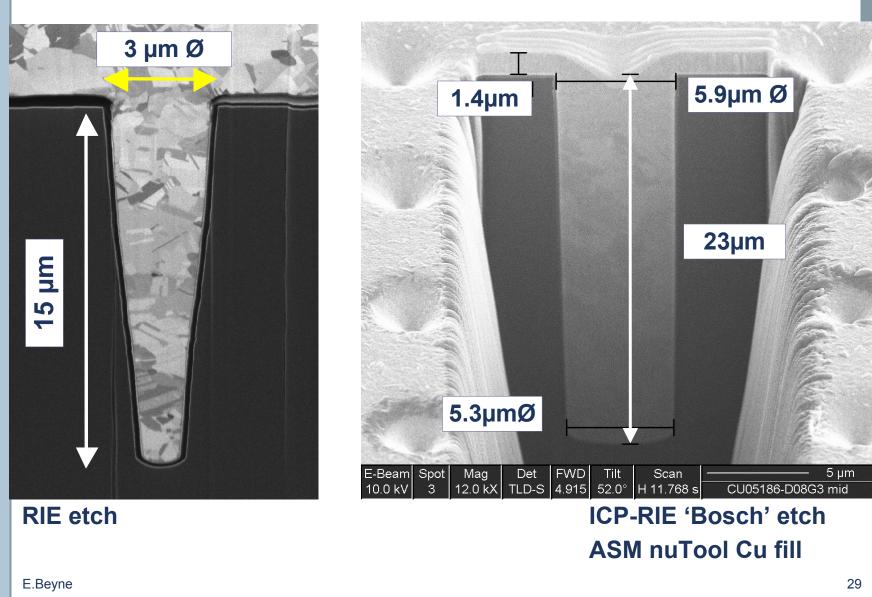

IC-stacking technology at 'tile'-level:

- 10 µm pitch 3D vias

- Burried "Cu-nails" between FEOL and BEOL

- No blockage of BEOL layers

- Cu-Cu thermo compression bonding

- Collective KGD Die-to-wafer bonding

## **3D-IC Cu nails**

## **Technology for 3D-interconnects**

- 3D interconnects may be realized at different levels of the micro-electronic system,

- Different microelectronic technologies may be used:

- Traditional packaging & interconnection technologies: 3D-SIP

- Wafer-level packaging technologies: 3D-WLP

- IC-foundry technologies: 3D-SIC and 3D-IC

- These technologies result in different 3Dinterconnect densities and capabilities.

- Choice of technology depends on the interconnect requirements of a given application

Trend to Increasing system complexity and system miniaturization requires SOC and SIP Technologies

New SIP technologies allow for new design Methodologies

Novel technology requires novel design tools to emerge from the feasibility stage

#### SEEDS FOR TOMORROW'S WORLD IMECNOLOGY