# Microelectronics System Design Research Group School of Electrical, Electronic & Computer Engineering

# Optimizing the integration and energy efficiency of through silicon via-based 3D interconnects

Panagiotis Asimakopoulos

**Technical Report Series**

NCL-EECE-MSD-TR-2011-173

$Contact: \verb"panagiotis.asimakopoulos@ncl.ac.uk"$

NCL-EECE-MSD-TR-2011-173

Copyright © 2011 Newcastle University

Microelectronics System Design Research Group School of Electrical, Electronic & Computer Engineering Merz Court Newcastle University Newcastle upon Tyne, NE1 7RU, UK

http://async.org.uk/

# OPTIMIZING THE INTEGRATION AND ENERGY EFFICIENCY OF THROUGH SILICON VIA-BASED 3D INTERCONNECTS

#### PANAGIOTIS ASIMAKOPOULOS

A Thesis Submitted for the Degree of Doctor of Philosophy at Newcastle University

School of Electrical, Electronic and Computer Engineering

Newcastle upon Tyne

November 2011

Panagiotis Asimakopoulos: *Optimizing the integration and energy efficiency of through silicon via-based 3D interconnects,* PhD Thesis, © November 2011

The aggressive scaling of CMOS process technology has been driving the rapid growth of the semiconductor industry for more than three decades. In recent years, the performance gains enabled by CMOS scaling have been increasingly challenged by highly-parasitic on-chip interconnects as wire parasitics do not scale at the same pace. Emerging 3D integration technologies based on vertical through-silicon vias (TSVs) promise a solution to the interconnect performance bottleneck, along with reduced fabrication cost and heterogeneous integration.

As TSVs are a relatively recent interconnect technology, innovative test structures are required to evaluate and optimise the process, as well as extract parameters for the generation of design rules and models. From the circuit designer's perspective, critical TSV characteristics are its parasitic capacitance, and thermomechanical stress distribution. This work proposes new test structures for extracting these characteristics. The structures were fabricated on a 65nm 3D process and used for the evaluation of that technology.

Furthermore, as TSVs are implemented in large, densely interconnected 3D-system-on-chips (SoCs), the TSV parasitic capacitance may become an important source of energy dissipation. Typical low-power techniques based on voltage scaling can be used, though this represents a technical challenge in modern technology nodes. In this work, a novel TSV interconnection scheme is proposed based on reversible computing, which shows frequency-dependent energy dissipation. The scheme is analysed using theoretical modelling, while a demonstrator IC was designed based on the developed theory and fabricated on a 130nm 3D process.

Some ideas and figures have appeared previously in the following publications:

- 1. D. Perry, J. Cho, S. Domae, **P. Asimakopoulos**, A. Yakovlev, P. Marchal, G. Van der Plas, and N. Minas. An efficient array structure to characterize the impact of through silicon vias on fet devices. In Proc. IEEE Int Microelectronic Test Structures (ICMTS) Conf, pages 118–122, 2011. (**best paper award**)

- 2. A. Mercha, G. Van der Plas, V. Moroz, I. De Wolf, P. Asimakopoulos, N. Minas, S. Domae, D. Perry, M. Choi, A. Redolfi, C. Okoro, Y. Yang, J. Van Olmen, S. Thangaraju, D. S. Tezcan, P. Soussan, J. H. Cho, A. Yakovlev, P. Marchal, Y. Travaly, E. Beyne, S. Biesemans, and B. Swinnen. Comprehensive analysis of the impact of single and arrays of through silicon vias induced stress on high-k / metal gate cmos performance. In Proc. IEEE Int. Electron Devices Meeting (IEDM), 2010.

- 3. A. Mercha, A. Redolfi, M. Stucchi, N. Minas, J. Van Olmen, S. Thangaraju, D. Velenis, S. Domae, Y. Yang, G. Katti, R. La-bie, C. Okoro, M. Zhao, **P. Asimakopoulos**, I. De Wolf, T. Chiarella, T. Schram, E. Rohr, A. Van Ammel, A. Jourdain, W. Ruythooren, S. Armini, A. Radisic, H. Philipsen, N. Heylen, M. Kostermans, P. Jaenen, E. Sleeckx, D. Sabuncuoglu Tezcan, I. Debusschere, P. Soussan, D. Perry, G. Van der Plas, J. H. Cho, P. Marchal, Y. Travaly, E. Beyne, S. Biesemans, and B. Swinnen. Impact of thinning and through silicon via proximity on high-k / metal gate first cmos performance. In Proc. Symp. VLSI Technology (VLSIT), pages 109–110, 2010.

- 4. P. Asimakopoulos, G. Van der Plas, A. Yakovlev, and P. Marchal. Evaluation of energy-recovering interconnects for low-power 3d stacked ics. In Proc. IEEE Int. Conf. 3D System Integration 3DIC 2009, pages 1–5, 2009.

- 5. **P. Asimakopoulos** and A. Yakovlev. An Adiabatic Power-Supply Controller For Asynchronous Logic Circuits. 20th UK Asynchronous Forum, pages 1–4, 2008.

— Steve Wozniak [79]

#### **ACKNOWLEDGEMENTS**

First and foremost I would like to express my gratitude to my supervisor, Prof. Alex Yakovlev, who provided the perfect balance between freedom and guidance, allowing me to obtain spherical knowledge and scope in microelectronics but at the same time to promptly complete my studies. I'm also grateful to the Engineering and Physical Science Research Council (EPSRC) for funding my PhD studies through their Doctoral Training Accounts.

As part of my research project I had the opportunity to spend some time at Imec, Belgium. The experiences and lessons learned during my stay at Imec will undoubtedly prove valuable in my forthcoming professional career. I would like to thank Dan Perry from Qualcomm for sharing his experience and ideas for the design of the characterization structures implemented on the 65nm Imec process. Special thanks to Shinichi Domae from Panasonic and Dr. Dimitrios Velenis for their assistance with the 65nm wafer measurements, as well as Marco Facchini for the time he spend trying to measure the energy-recovery circuits. Last but not least, I'd like to thank Geert Van der Plas and Paul Marchal for their advices and guidance throughout my stay at Imec.

Finally, many thanks to my colleagues at Newcastle University for assisting me in diverse ways during my studies. I would like to especially mention Dr. Santosh Shedabale and James Docherty for reviewing and commenting on parts of this text, as well as Dr. Robin Emery for the numerous technical discussions and for helping setup the design tools.

# CONTENTS

| 1 | Intr       | duction                                          | 1 |

|---|------------|--------------------------------------------------|---|

|   | 1.1        | Research goals and contribution                  | 2 |

|   | 1.2        | m ·                                              | 3 |

| 2 | Bacl       | _                                                | 5 |

|   | 2.1        | -                                                | 5 |

|   |            | -                                                | 6 |

|   |            |                                                  | 9 |

|   | 2.2        | Energy-recovery logic                            |   |

|   |            | 2.2.1 Energy-recovery architectures              |   |

|   |            | 2.2.2 Power-clock generators                     |   |

|   | 2.3        | Full-custom design flow                          | 0 |

|   | 2.4        | Summary                                          | 1 |

| 3 | Cha        | acterization of TSV capacitance                  | 3 |

| , | 3.1        | Introduction                                     |   |

|   | 3.2        | TSV parasitic capacitance                        |   |

|   | 3.3        | Integrated capacitance measurement techniques 24 |   |

|   | 3.4        | Electrical characterization                      | 1 |

|   | <i>J</i> , | 3.4.1 Physical implementation                    |   |

|   |            | 3.4.2 Measurement setup                          |   |

|   |            | 3.4.3 Experimental results                       |   |

|   | 3.5        | Summary and conclusions                          |   |

| 4 |            | proximity impact on MOSFET performance 46        |   |

| • | 4.1        | Introduction                                     |   |

|   | 4.2        | TSV-induced thermomechanical stress              |   |

|   | 4.3        | Test structure implementation                    |   |

|   | 13         | 4.3.1 MOSFET arrays 5                            |   |

|   |            | 4.3.2 Digital selection logic 55                 |   |

|   | 4.4        | Experimental measurements 6                      |   |

|   |            | 4.4.1 Data processing methodology 6              | 1 |

|   |            | 4.4.2 Measurement setup 62                       | 2 |

|   |            | 4.4.3 PMOS (long channel) 62                     | 4 |

|   |            | 4.4.4 PMOS (short channel)                       | 1 |

|   | 4.5        | Summary and conclusions                          |   |

| 5 | Eva        | nation of energy-recovery for TSV interconnects  |   |

|   | 5.1        | Introduction                                     |   |

|   | 5.2        | Energy-recovery TSV interconnects                |   |

|   | 5.3        | Analysis                                         |   |

|   | 5 5        | 5.3.1 Adiabatic driver                           |   |

|   |            | 5.3.2 Inductor's parasitic resistance 82         |   |

|   |            | 5.3.3 Switch M1                                  |   |

|   |            | 5.3.4 Timing Constraints                         |   |

|   | 5.4        | Simulations                                      |   |

|   | ٠.         | 5.4.1 Comparison to CMOS                         |   |

|    | 5.5                                | Summary and conclusions               | )1         |

|----|------------------------------------|---------------------------------------|------------|

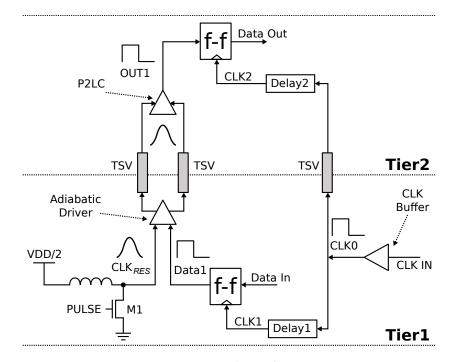

| 6  | Energy-recovery 3D-IC demonstrator |                                       | )2         |

|    | 6.1                                | Introduction                          | )2         |

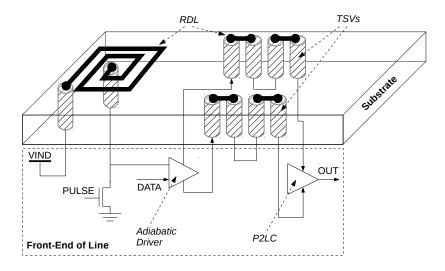

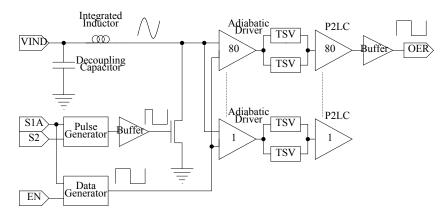

|    | 6.2                                | Physical implementation 9             | )2         |

|    |                                    | 6.2.1 Adiabatic driver                | )4         |

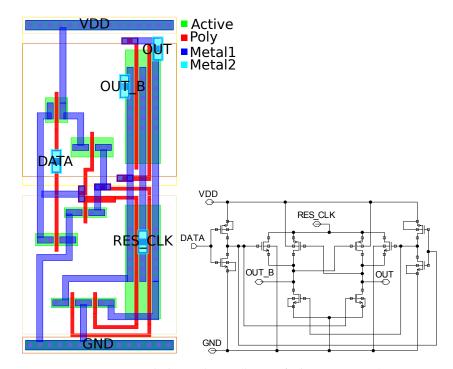

|    |                                    | 6.2.2 Pulse-to-level converter 9      | 95         |

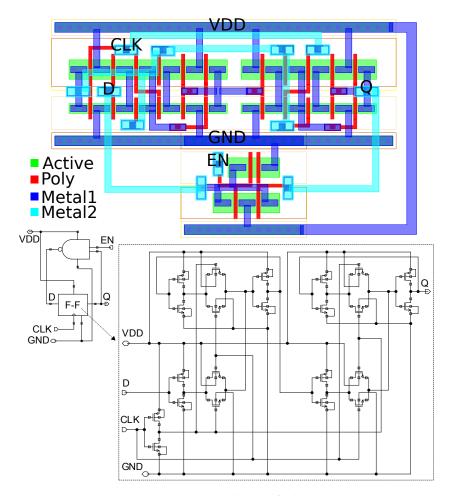

|    |                                    | 6.2.3 Data generator                  | 95         |

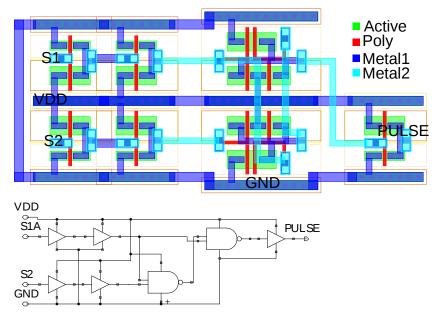

|    |                                    | 6.2.4 Pulse generator                 | 95         |

|    |                                    | 6.2.5 Integrated inductor             | 97         |

|    |                                    | 6.2.6 Top level design                | 8          |

|    |                                    |                                       | 101        |

|    | 6.3                                | Post-layout simulation and comparison | 101        |

|    | 6.4                                | Experimental measurements             | 106        |

|    |                                    | 6.4.1 Measurement setup               | 106        |

|    |                                    | 6.4.2 Results                         | 106        |

|    | 6.5                                | Summary and conclusions               | [11        |

| 7  | Conclusions                        |                                       | 14         |

|    | 7.1                                | Main contributions                    | 115        |

|    | 7.2                                |                                       | 16         |

| A  | App                                | pendix A: Photos                      | 18         |

| В  | App                                | pendix B: Statistics                  | <b>2</b> 0 |

| BI | BLIO                               | GRAPHY 1                              | 22         |

# LIST OF FIGURES

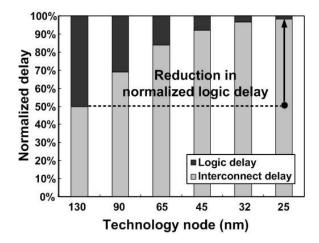

| Figure 1.1  | Scaling trend of logic and interconnect delay [30] |

|-------------|----------------------------------------------------|

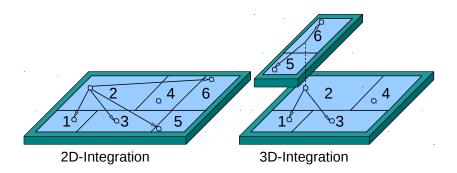

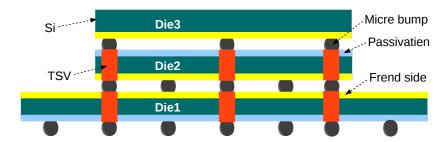

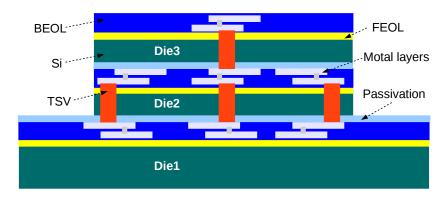

| Figure 2.1  | Comparison of 2D/3D Integration 5                  |

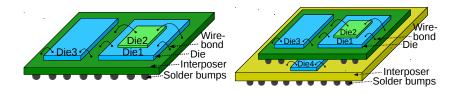

| Figure 2.2  | System-in-a-package                                |

| Figure 2.3  | Package-on-package 6                               |

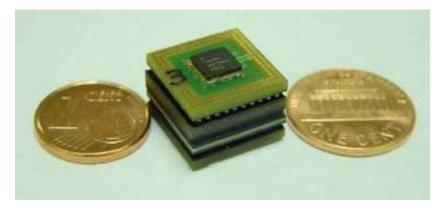

| Figure 2.4  | Imec's 3-D SIP wireless bio-electronic sensor      |

| 118410 2.4  | [67]                                               |

| Figure 2.5  | 3D wafer-level-packaging                           |

| Figure 2.6  | 3D-stacked IC                                      |

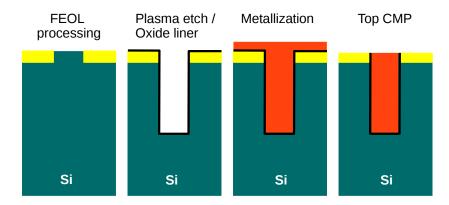

| Figure 2.7  | TSV process steps                                  |

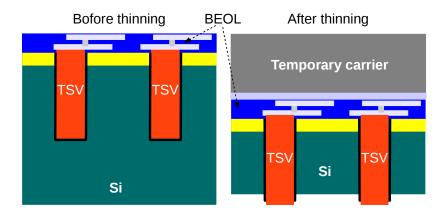

| Figure 2.8  | Before thinning/after thinning 10                  |

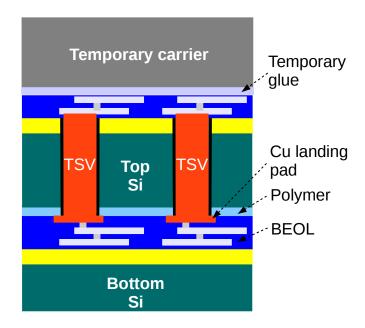

| Figure 2.9  | TSV stacking                                       |

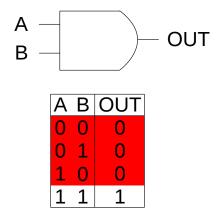

| Figure 2.10 | Conventional AND gate                              |

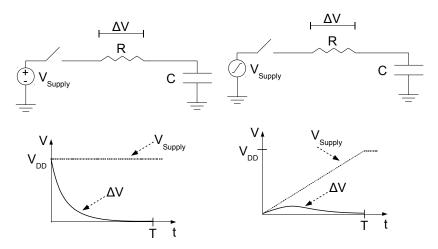

| Figure 2.11 | CMOS switching                                     |

| Figure 2.12 | Adiabatic switching                                |

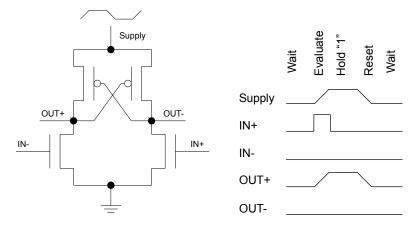

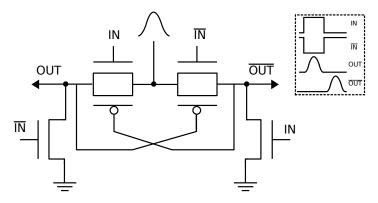

| Figure 2.13 | Basic 2N-2P adiabatic circuit                      |

| Figure 2.14 | 2N-2P timing                                       |

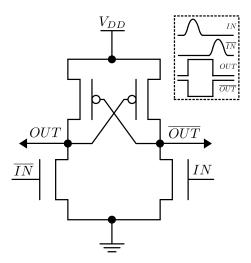

| Figure 2.15 | Adiabatic driver                                   |

| Figure 2.16 | Stepwise charging generator                        |

| Figure 2.17 | 1N power clock generator                           |

| Figure 2.17 | Design flow                                        |

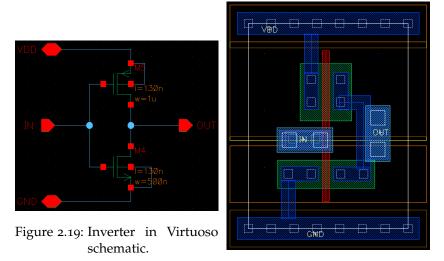

| Figure 2.19 | T                                                  |

| Figure 2.19 | T                                                  |

| O           |                                                    |

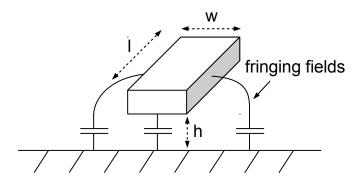

| Figure 3.1  | Isolated 2D wire capacitance                       |

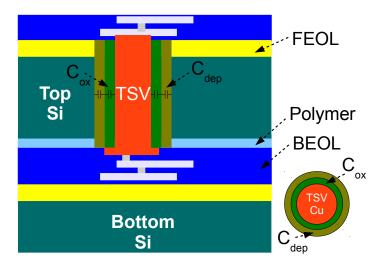

| Figure 3.2  | TSV parasitic capacitance                          |

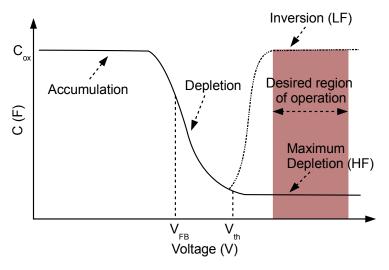

| Figure 3.3  | Capacitance vs. Gate voltage (CV) diagram          |

| Figure 3.4  | of a MOS Capacitor                                 |

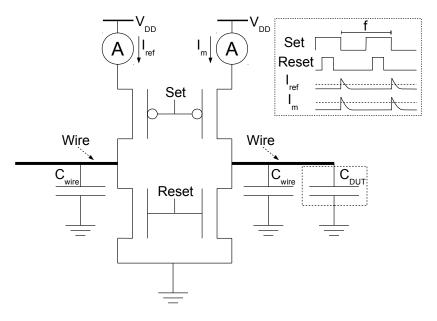

| 0 .         | CBCM pseudo-inverters                              |

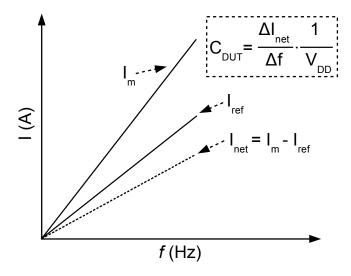

| Figure 3.5  | Current as a function of frequency in CBCM. 28     |

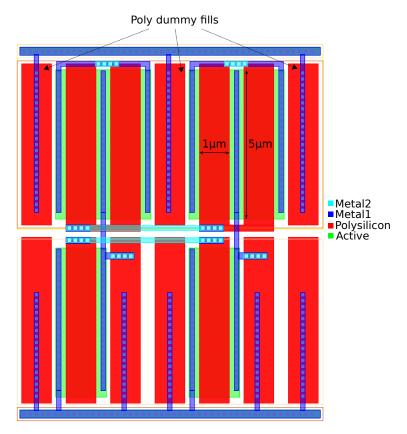

| Figure 3.6  | CBCM pseudo-inverter pair in layout 29             |

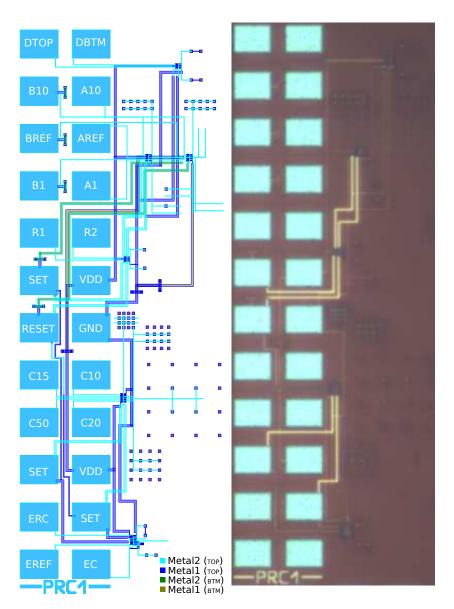

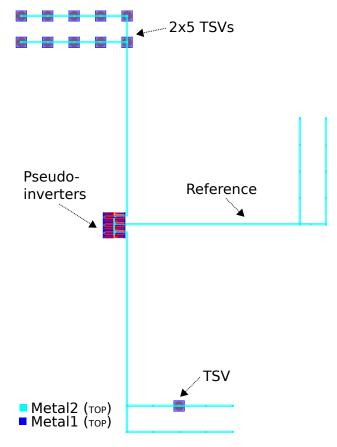

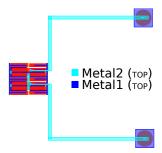

| Figure 3.7  | PRC1 test pad module (layout) 30                   |

| Figure 3.8  | PRC1 test pad module (micrograph) 30               |

| Figure 3.9  | Structure 'A' - Single TSV capacitance (TOP        |

| г.          | die)                                               |

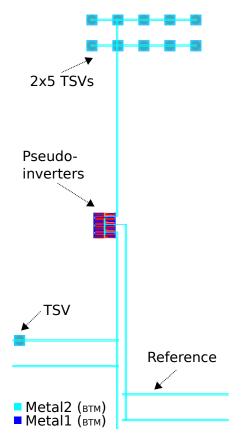

| Figure 3.10 | Structure 'B' - Single TSV capacitance (BOT-       |

| 771         | TOM die)                                           |

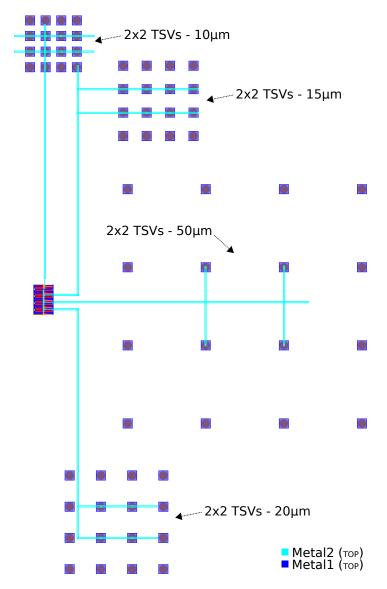

| Figure 3.11 | Structure 'C' - Variable pitch TSV capacitance.34  |

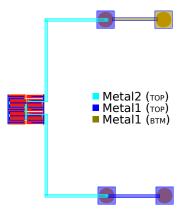

| Figure 3.12 | Structure 'D' - TSV capacitance measure-           |

|             | ment with interconnection on TOP or BOT-           |

|             | TOM die                                            |

| Figure 3.13 | Structure 'R' - Evaluation of TSV capacit-         |

|             | ance measurement accuracy 35                       |

| Figure 3.14 | Structure 'E' - TSV capacitance effect on       |

|-------------|-------------------------------------------------|

|             | signal propagation delay (layout) 35            |

| Figure 3.15 | Structure 'E' - TSV capacitance effect on       |

|             | signal propagation delay (schematic) 36         |

| Figure 3.16 | Measurement setup                               |

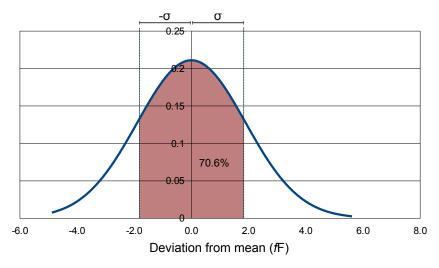

| Figure 3.17 | TSV capacitance D2D variability on wafer        |

|             | 'D11' - Probability density function 39         |

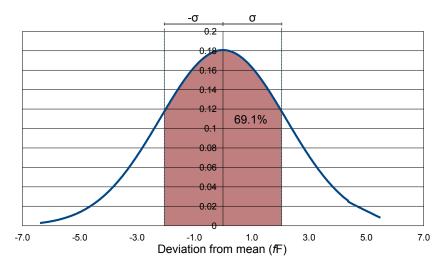

| Figure 3.18 | TSV capacitance D2D variability on wafer        |

|             | 'D18' - Probability density function 40         |

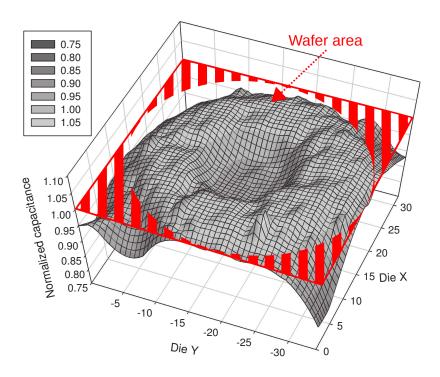

| Figure 3.19 | TSV capacitance measurement results on          |

|             | wafer D11                                       |

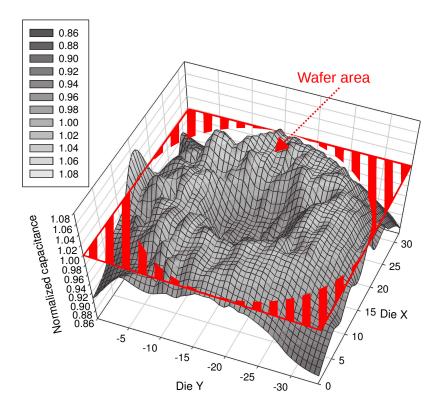

| Figure 3.20 | TSV capacitance measurement results on          |

|             | wafer D18 41                                    |

| Figure 3.21 | Simulated oxide liner thickness variation 42    |

| Figure 3.22 | TSV capacitance W2W variability - Probab-       |

|             | ility density functions 42                      |

| Figure 3.23 | Variable pitch TSV capacitance experimental     |

|             | data from wafer 'D18' - Probability density     |

|             | function                                        |

| Figure 3.24 | LCR experimental data from wafer 'D18' -        |

|             | Probability density function 44                 |

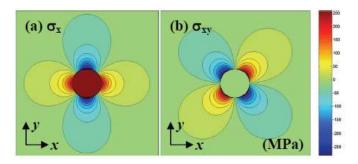

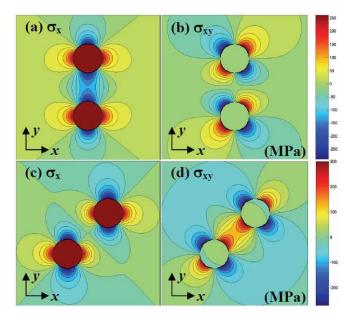

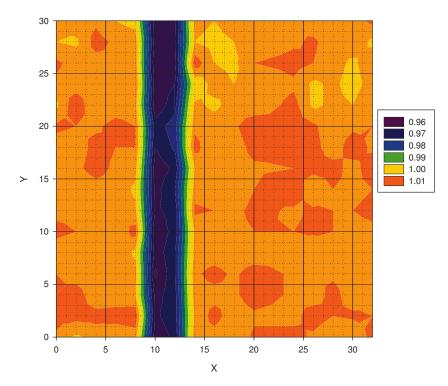

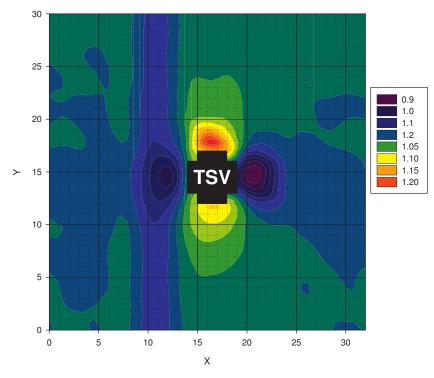

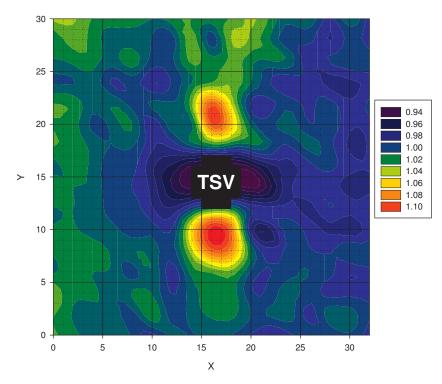

| Figure 4.1  | TSV thermomechanical stress simulation [40]. 47 |

| Figure 4.2  | TSV thermomechanical stress interaction         |

|             | between two TSVs [40] 48                        |

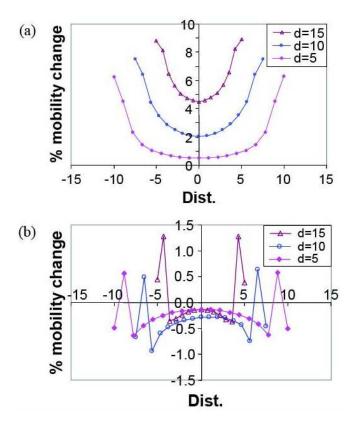

| Figure 4.3  | Estimated mobility shift on PMOS (a) and        |

|             | NMOS (b) transistors in between two TSVs        |

|             | separated by distance d [65] 49                 |

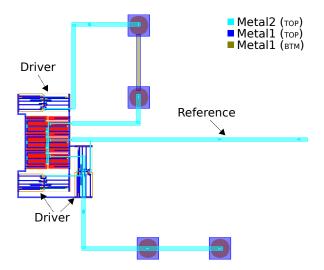

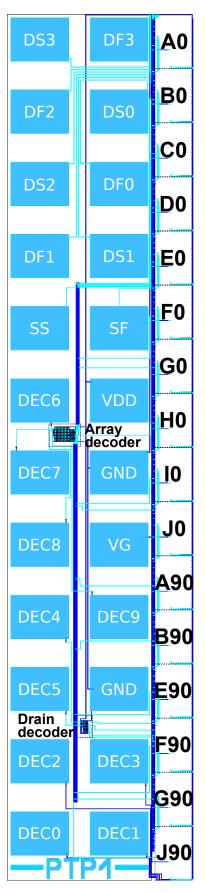

| Figure 4.4  | PTP1 test pad module (layout) 50                |

| Figure 4.5  | PTP1 test pad module (micrograph) 50            |

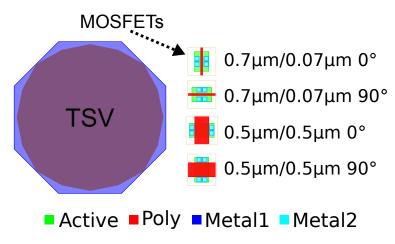

| Figure 4.6  | MOSFET dimensions and rotations 51              |

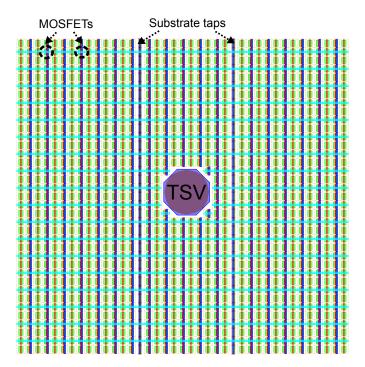

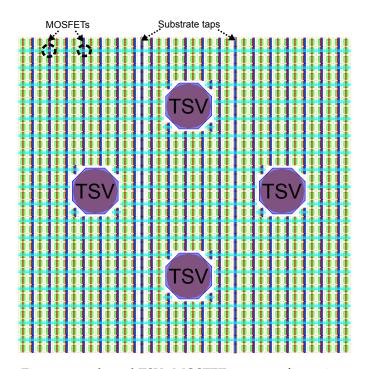

| Figure 4.7  | 1 TSV MOSFET array configuration 52             |

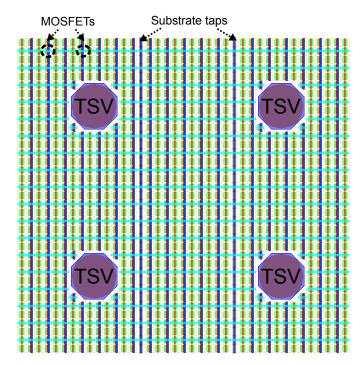

| Figure 4.8  | 4 diagonal TSVs MOSFET array configuration.52   |

| Figure 4.9  | 4 lateral TSVs MOSFET array configuration. 53   |

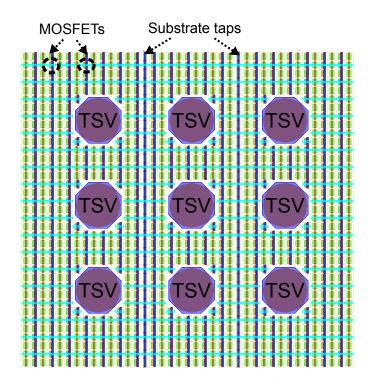

| Figure 4.10 | 9 TSVs MOSFET array configuration 53            |

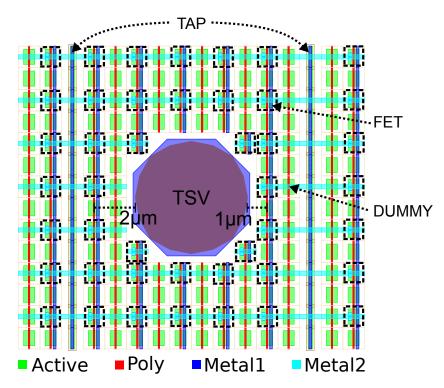

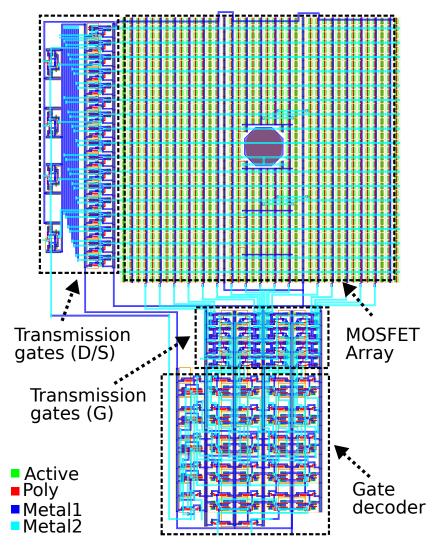

| Figure 4.11 | MOSFET array detail 55                          |

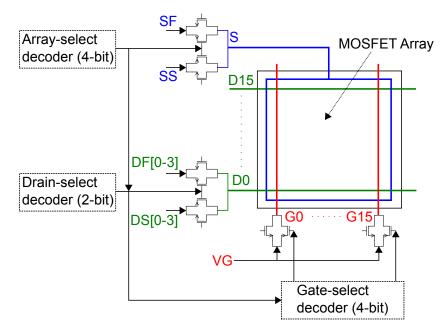

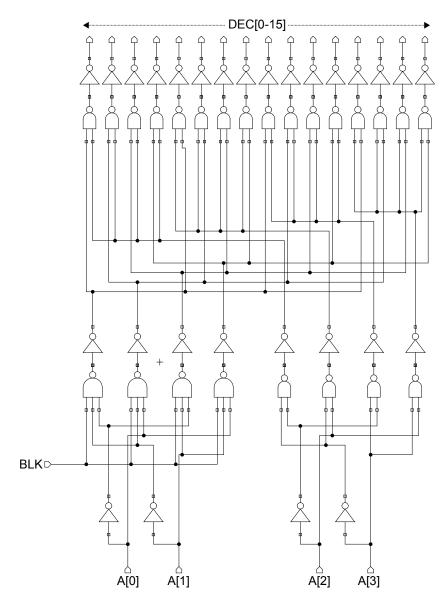

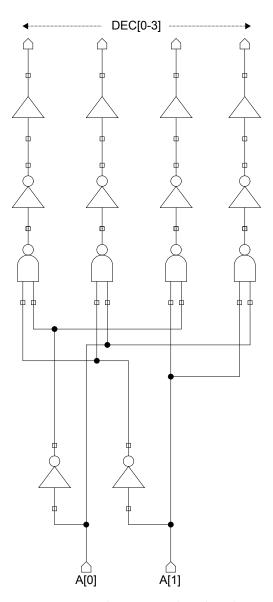

| Figure 4.12 | Digital selection logic                         |

| Figure 4.13 | MOSFET array with digital selection logic 57    |

| Figure 4.14 | 4-bit Gate-enable/Array-enable decoder 58       |

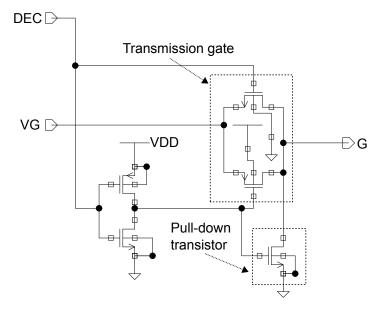

| Figure 4.15 | Transmission gate for MOSFET Gate terminals.59  |

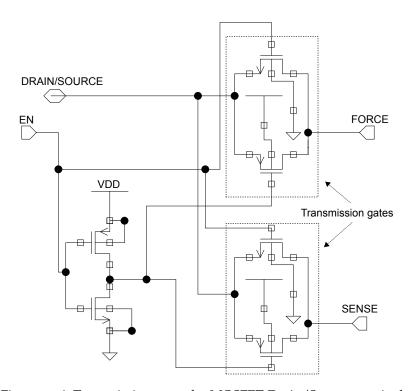

| Figure 4.16 | Transmission gates for MOSFET Drain/-           |

| E.          | Source terminals 59                             |

| Figure 4.17 | 2-bit Drain-select decoder 60                   |

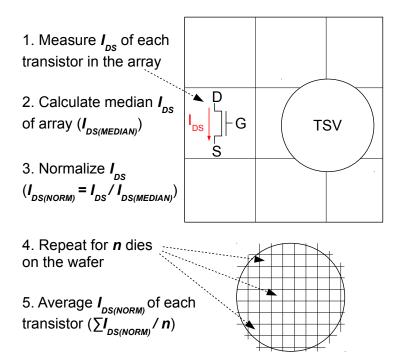

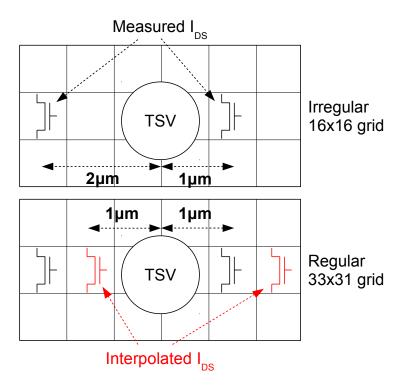

| Figure 4.18 | Processing of measurement results 62            |

| Figure 4.19 | Interpolation of measurement results 63         |

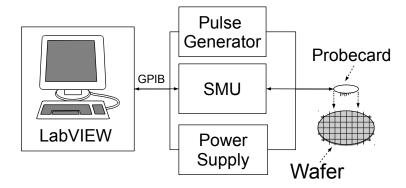

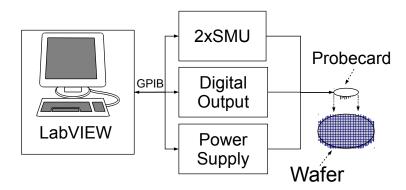

| Figure 4.20 | Measurement setup                               |

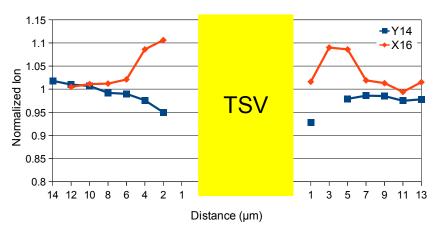

| Figure 4.21 | Normalised on-current for PMOS structure        |

|             | "Fo" (Do8)                                      |

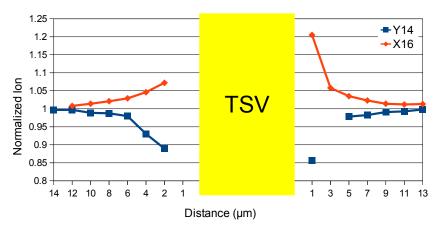

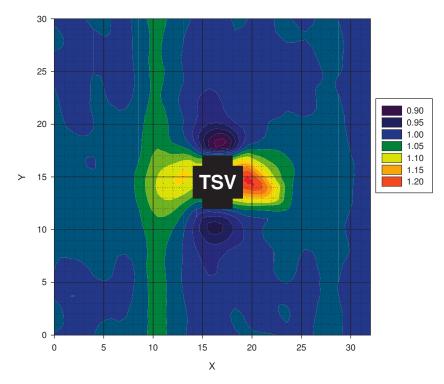

| Figure 4.22 | Normalised on-current for PMOS structure                      |

|-------------|---------------------------------------------------------------|

| T.          | "Go" (Do8)                                                    |

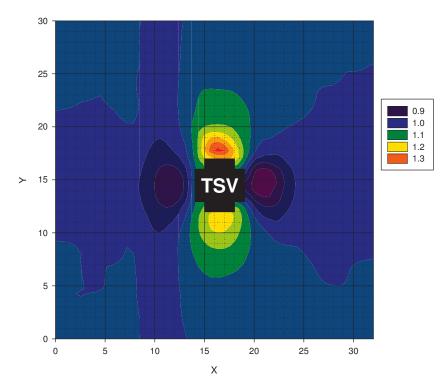

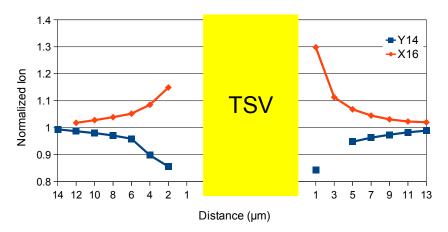

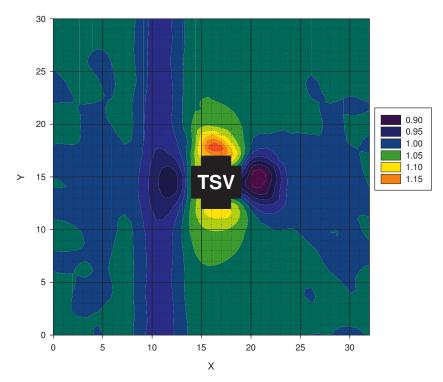

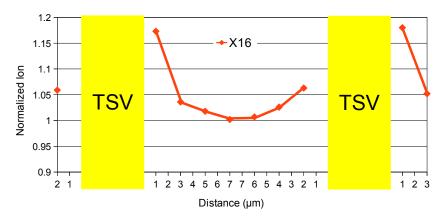

| Figure 4.23 | Normalised on-current for PMOS structure "Go" (Do8,Y=14,X=16) |

| Figure 4.24 | Normalised on-current for PMOS structure                      |

| 118410 4.24 | "Go" (D20)                                                    |

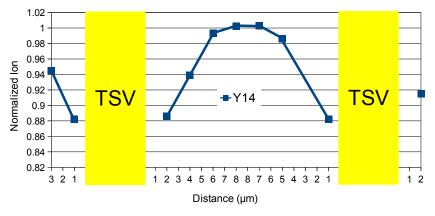

| Figure 4.25 | Normalised on-current for PMOS structure                      |

|             | "Go" (D20,Y=14,X=16) 67                                       |

| Figure 4.26 | Normalised on-current for PMOS structure                      |

|             | "Go" (Do8, 60°C)                                              |

| Figure 4.27 | Normalised on-current for PMOS structure                      |

|             | "Go" (Do8, Y=14, X=16, 60°C) 69                               |

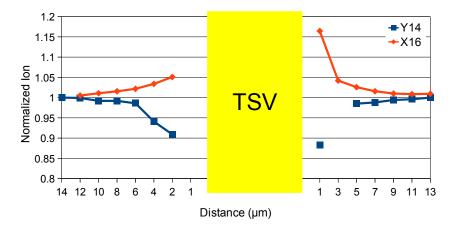

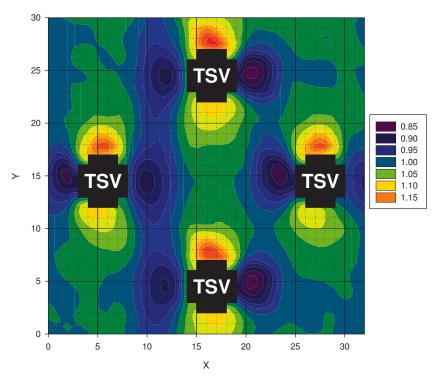

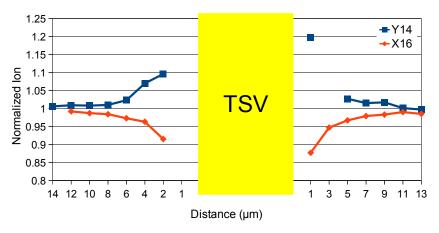

| Figure 4.28 | Normalised on-current for PMOS structure                      |

| ,           | "Io" (Do8)                                                    |

| Figure 4.29 | Normalised on-current for PMOS structure                      |

| 0 , ,       | "Io" (Do8, X=16)                                              |

| Figure 4.30 | Normalised on-current for PMOS structure                      |

| 0 13        | "Io" (Do8, Y=14)                                              |

| Figure 4.31 | Normalised on-current for PMOS structure                      |

| 0 13        | "G90" (Do8)                                                   |

| Figure 4.32 | Normalised on-current for PMOS structure                      |

| 0 13        | "G90" (Do8, Y=14, X=16)                                       |

| Figure 4.33 | Normalised on-current for PMOS structure                      |

| 0 133       | "Bo" (Do8)                                                    |

| Figure 4.34 | Normalised on-current for PMOS structure                      |

| 0 131       | "Bo" (Do8, Y=14, X=16)                                        |

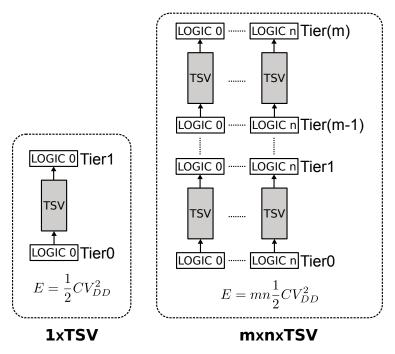

| Figure 5.1  | TSV energy dissipation per cycle increase                     |

| O J         | with 3D integration density                                   |

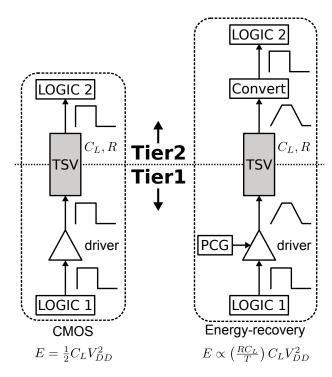

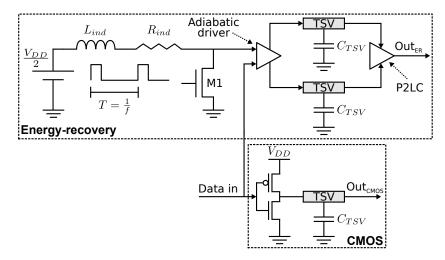

| Figure 5.2  | Comparison of a typical CMOS TSV driver                       |

| O J         | to the proposed energy-recovery                               |

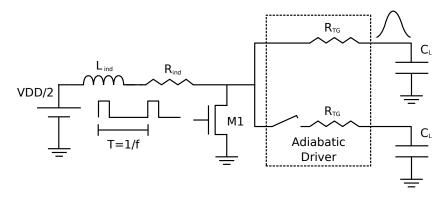

| Figure 5.3  | Adiabatic driver                                              |

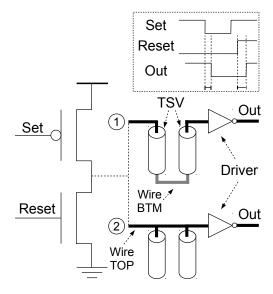

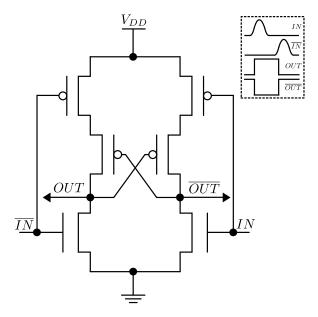

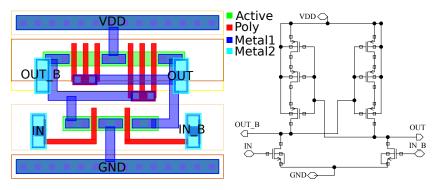

| Figure 5.4  | A simple pulse-to-level converter (P2LC) 78                   |

| Figure 5.5  | Resonant pulse generator with dual-rail data                  |

| 0 00        | encoding                                                      |

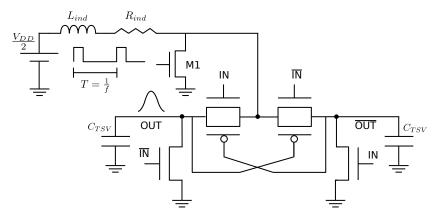

| Figure 5.6  | Energy-recovery scheme for TSV interconnects.79               |

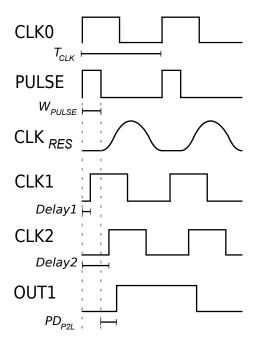

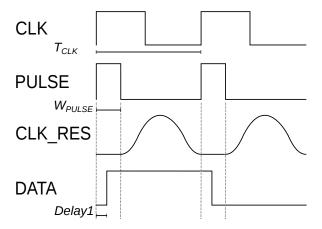

| Figure 5.7  | Energy-recovery timing constraints 83                         |

| Figure 5.8  | Test case for the evaluation of the theoret-                  |

| 0 3         | ical model                                                    |

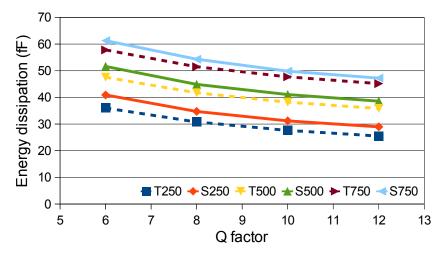

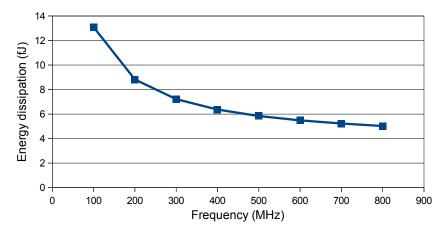

| Figure 5.9  | Energy dissipation results (fJ/cycle), the-                   |

| 0 37        | oretical model (T) versus SPICE simulator                     |

|             | (S)                                                           |

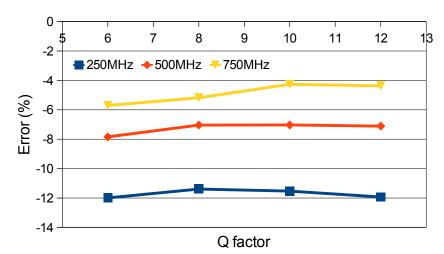

| Figure 5.10 | Energy dissipation estimation error of the                    |

| 0 0         | theoretical model compared to the SPICE                       |

|             | simulator                                                     |

| Figure 5.11 | Test case for comparison of energy-recovery                   |

|             | to CMOS                                                       |

| Figure 5.12 | Improved P2LC design 87                                       |

|             | - · · · · · · · · · · · · · · · · · · ·                       |

| Figure 5.13 | Simulated energy dissipation of improved P2LC design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 87 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

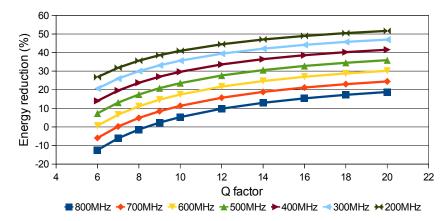

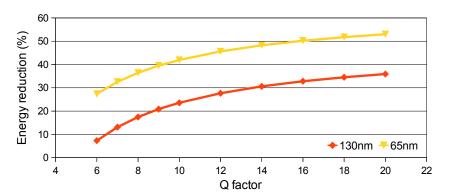

| Figure 5.14 | Energy dissipation reduction achieved by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 07 |

|             | the energy-recovery circuit compared to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

| T.          | CMOS for variable Q factor ( $C = 80 fF$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 88 |

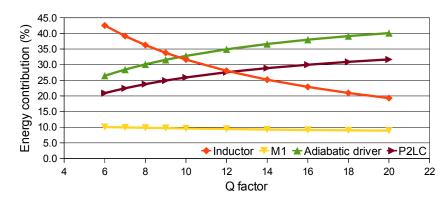

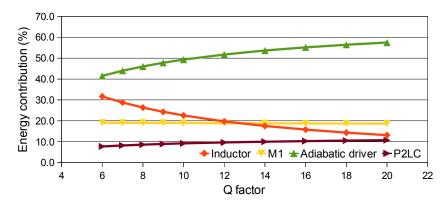

| Figure 5.15 | Energy contribution of energy-recovery cir-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0.0  |

| F: (        | cuit components at $200MHz$ ( $C = 80fF$ ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 88 |

| Figure 5.16 | Energy contribution of energy-recovery cir-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0    |

| т.          | cuit components at $800MHz$ ( $C = 80fF$ ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 89 |

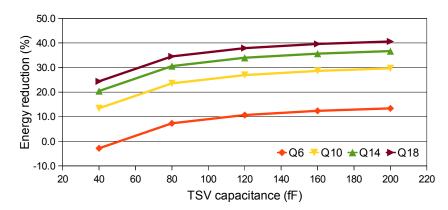

| Figure 5.17 | Energy dissipation reduction achieved by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

|             | the energy-recovery circuit compared to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

|             | CMOS with variable TSV capacitance ( $C = \frac{1}{2} \frac{1}$ | 00   |

| Cioumo = 40 | 80fF, $f = 500MHz$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 89 |

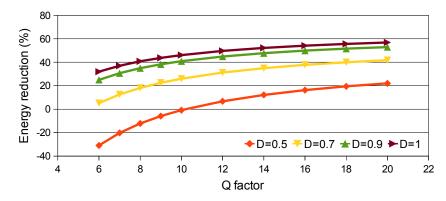

| Figure 5.18 | Energy dissipation reduction achieved by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

|             | the energy-recovery circuit compared to $CMOS(C - 80 fT, f - 200 MHz)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.0  |

| Figure 5 10 | CMOS ( $C = 80 fF$ , $f = 200 MHz$ ) Energy dissipation reduction achieved by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 90 |

| Figure 5.19 | the energy-recovery circuit compared to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

|             | CMOS for variable technology ( $C = 80 fF$ ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

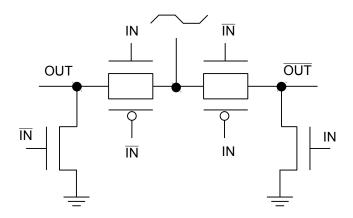

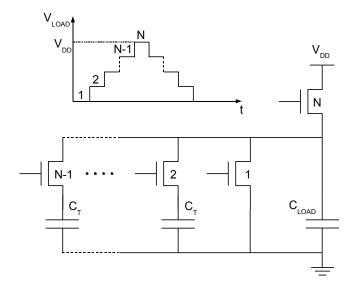

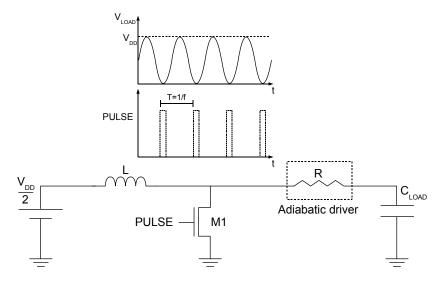

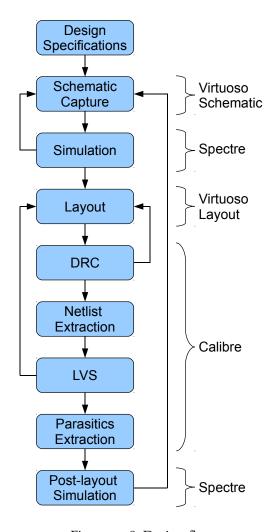

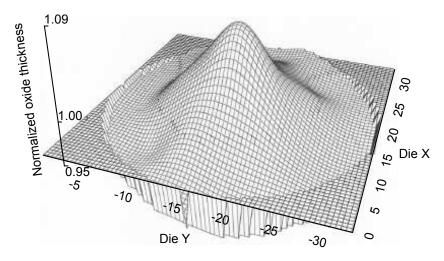

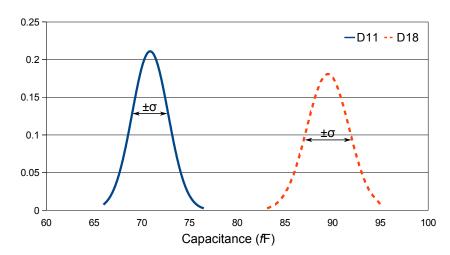

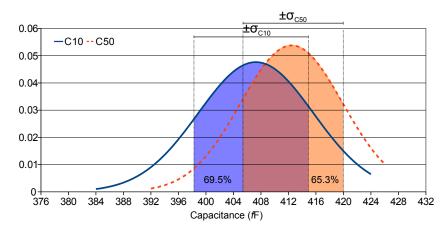

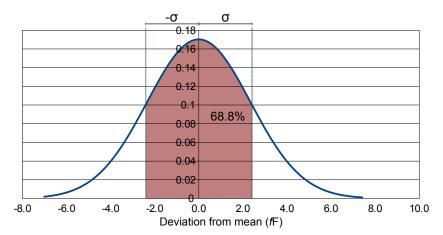

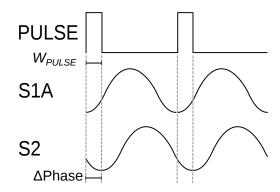

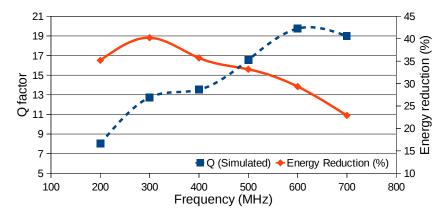

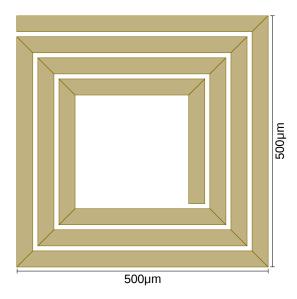

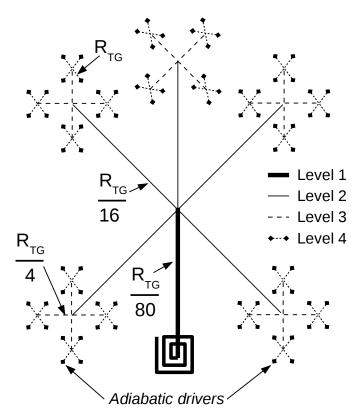

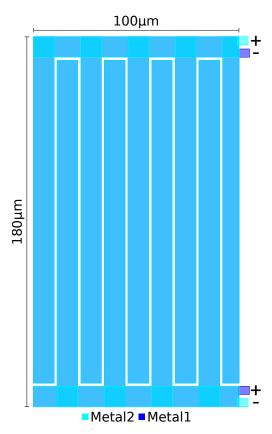

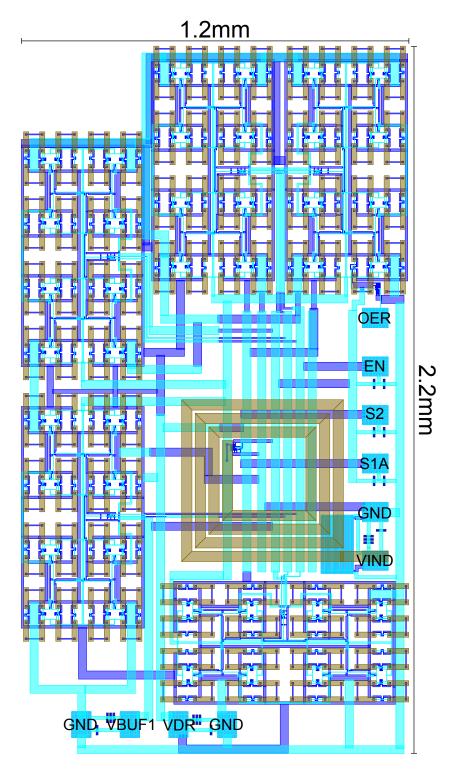

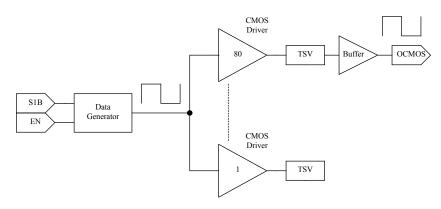

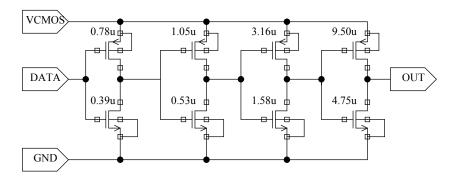

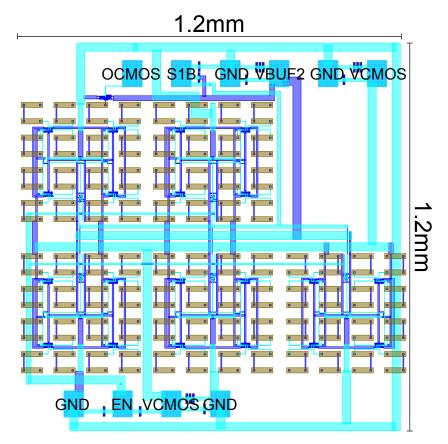

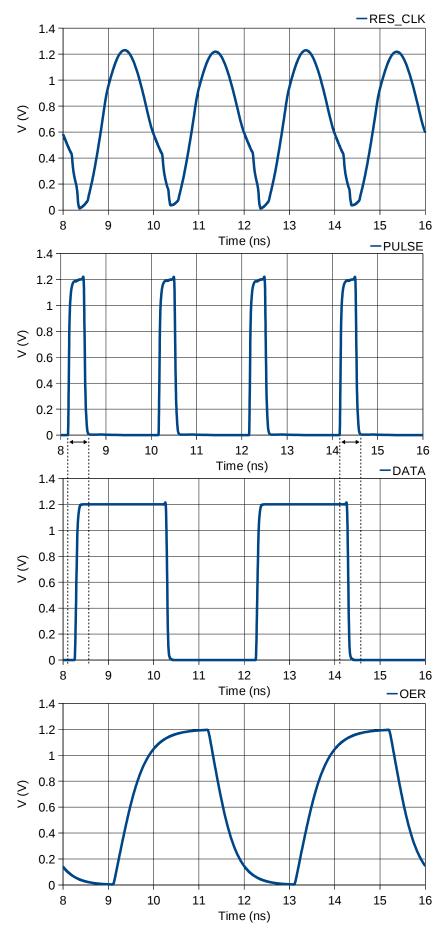

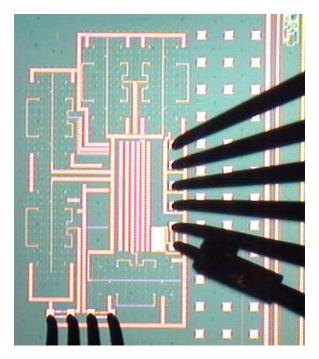

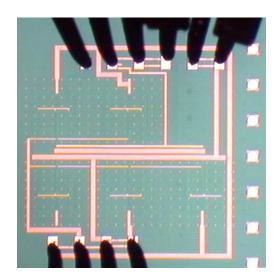

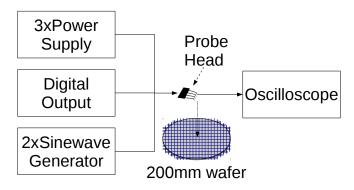

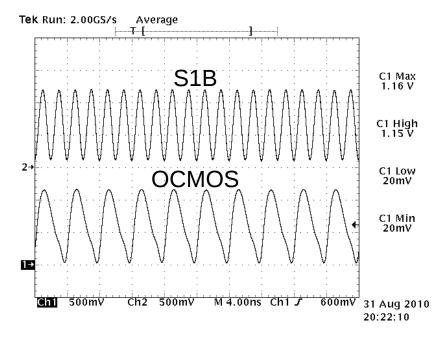

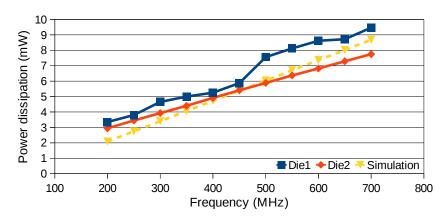

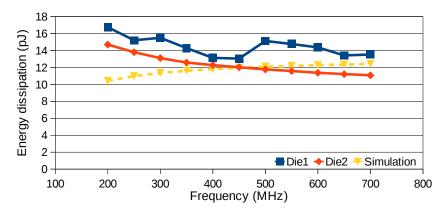

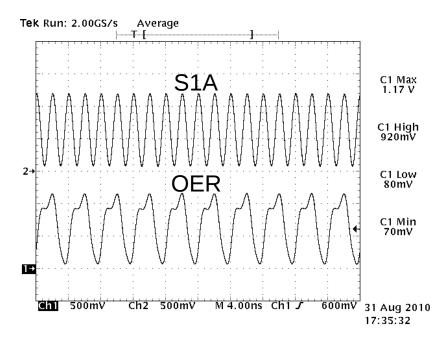

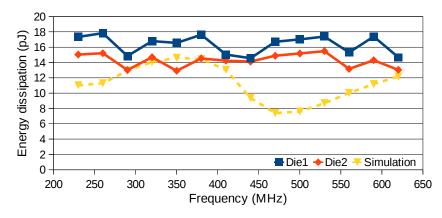

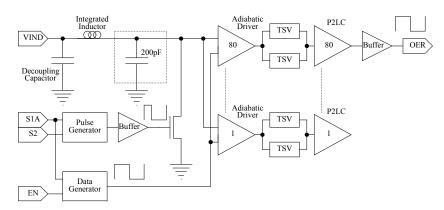

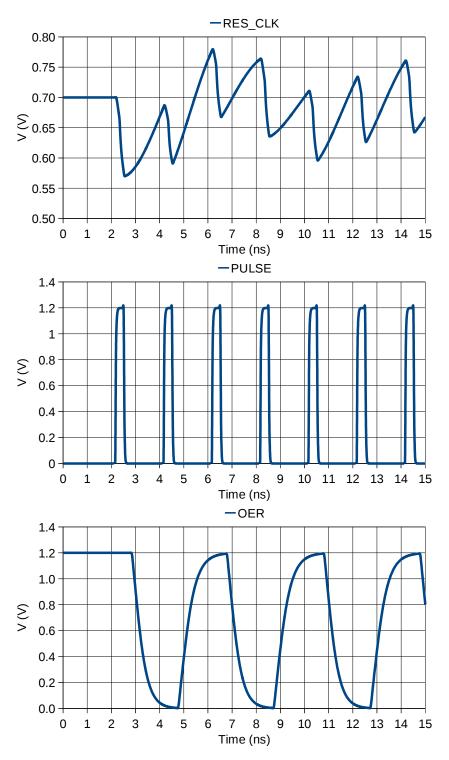

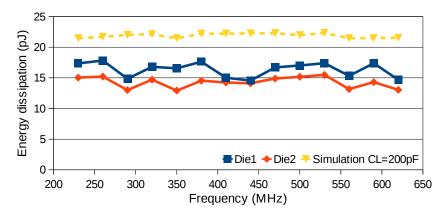

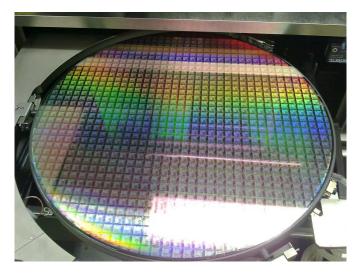

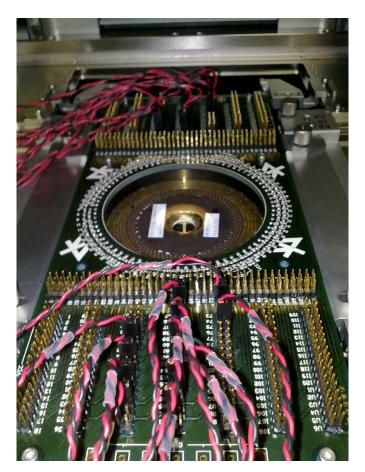

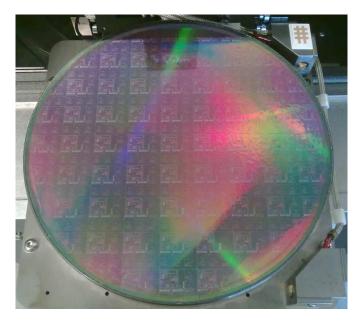

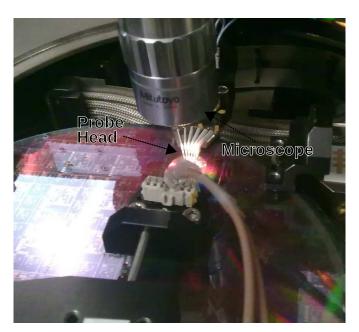

|             | f = 500MHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 00   |