### School of Electrical, Electronic & Computer Engineering

# Mixed Radix Design Flow for Security Applications

A.Rafiev

**Technical Report Series**

NCL-EECE-MSD-TR-2011-175

September 2011

| Contact: |  |  |

|----------|--|--|

|          |  |  |

ashur.rafiev@ncl.ac.uk

Supported by EPSRC grant GR/F016786/1

NCL-EECE-MSD-TR-2011-175

Copyright © 2011 Newcastle University

School of Electrical, Electronic & Computer Engineering,

Merz Court,

Newcastle University,

Newcastle upon Tyne, NE1 7RU, UK

http://async.org.uk/

#### **Abstract**

The purpose of secure devices, such as smartcards, is to protect sensitive information against software and hardware attacks. Implementation of the appropriate protection techniques often implies non-standard methods that are not supported by the conventional design tools. In the recent decade the designers of secure devices have been working hard on customising the workflow. The presented research aims at collecting the up-to-date experiences in this area and create a generic approach to the secure design flow that can be used as guidance by engineers.

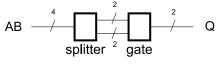

Well-known countermeasures to hardware attacks imply the use of specific signal encodings. Therefore, multi-valued logic has been considered as a primary aspect of the secure design. The choice of radix is crucial for multi-valued logic synthesis. Practical examples reveal that it is not always possible to find the optimal radix when taking into account actual physical parameters of multi-valued operations. In other words, each radix has its advantages and disadvantages. Our proposal is to synthesise logic in different radices, so it could benefit from their combination.

With respect to the design opportunities of the existing tools and the possibilities of developing new tools that would fill the gaps in the flow, two distinct design approaches have been formed: conversion driven design and pre-synthesis.

The conversion driven design approach takes the outputs of mature and timeproven electronic design automation (EDA) synthesis tools to generate mixed radix datapath circuits in an endeavour to investigate the added relative advantages or disadvantages. An algorithm underpinning the approach is presented and formally described together with secure gate-level implementations. The obtained results are reported showing an increase in power consumption, thus giving further motivation for the second approach.

The pre-synthesis approach is aimed at improving the efficiency by using multivalued logic synthesis techniques to produce an abstract component-level circuit before mapping it into technology libary. Reed-Muller expansions over Galois field arithmetic have been chosen as a theoretical foundation for this approach. In order to enable the combination of radices at the mathematical level, the multi-valued Reed-Muller expansions have been developed into mixed radix Reed-Muller expansions. The goals of the work is to estimate the potential of the new approach and to analyse its impact on circuit parameters down to the level of physical gates. The benchmark results show the approach extends the search space for optimisation and provides information on how the implemented functions are related to different radices.

The theory of two-level radix models and corresponding computation methods are the primary theoretical contribution. It has been implemented in RMMixed tool and interfaced to the standard EDA tools to form a complete security-aware design flow.

## Acknowledgements

First of all, I would like to thank my mother, Nina, for her love and patience. Even from far away she has been supporting me every day.

I am very grateful to my supervisors, Alex Yakovlev and Albert Koelmans. I would have never been able to succeed in my research without their help and guidance.

Also many thanks to my friends and colleagues – Andrey Mokhov, Arseniy Alekseyev, Julian Murphy, Frank Burns, Danil Sokolov, Stanislavs Golubcovs, and Ivan Poliakov – for many useful and inspiring ideas, criticism, support, and for just being very nice.

I kindly thank Michael Keller and Anne Harrow for the spiritual support and encouragement they have been giving me throughout these years.

This research was supported by the EPSRC grant GR/F016786/1 (SURE) and the ORS Awards Scheme.

## **Contents**

| A۱ | bstrac | ct      |                                      | 1  |

|----|--------|---------|--------------------------------------|----|

| A  | cknov  | wledge  | ments                                | 2  |

| Li | st of  | Figures |                                      | 6  |

| Li | st of  | Tables  |                                      | 8  |

| Li | st of  | Publica | ations                               | 10 |

| 1  | Intr   | oductio | on                                   | 1  |

|    | 1.1    | Motiv   | ration                               | 3  |

|    | 1.2    | Contr   | ibution                              | 7  |

|    | 1.3    | Orgar   | nisation of the thesis               | 9  |

| 2  | Bac    | kgroun  | d                                    | 12 |

|    | 2.1    | Hardy   | ware Attacks and Countermeasures     | 12 |

|    |        | 2.1.1   | Types of attacks and countermeasures | 12 |

|    |        | 2.1.2   | Power balancing using m-of-n codes   | 15 |

|    | 2.2    | Galois  | s Fields and Reed-Muller Expansions  | 23 |

|    |        | 2.2.1   | Galois Fields                        | 23 |

|    |        | 2.2.2   | Multi-valued Reed-Muller expansions  | 32 |

|    |        | 2.2.3   | Green's direct method                | 33 |

|    | 2.3    | Sumn    | nary                                 | 39 |

| 3 | Base | eline R | esearch                                                                                                    | 41  |

|---|------|---------|------------------------------------------------------------------------------------------------------------|-----|

|   | 3.1  | Secure  | e Design Flow                                                                                              | 41  |

|   |      | 3.1.1   | Data path synthesis                                                                                        | 42  |

|   |      | 3.1.2   | Control path synthesis                                                                                     | 45  |

|   |      | 3.1.3   | Physical design                                                                                            | 48  |

|   | 3.2  | Conve   | ersion Driven Mixed Radix Design                                                                           | 49  |

|   |      | 3.2.1   | Conversion basics                                                                                          | 49  |

|   |      | 3.2.2   | Types of gate grouping                                                                                     | 51  |

|   |      | 3.2.3   | Grouping based on bitwise regularity                                                                       | 54  |

|   |      | 3.2.4   | Grouping based on binary trees                                                                             | 58  |

|   |      | 3.2.5   | Component implementation                                                                                   | 61  |

|   |      | 3.2.6   | Benchmark results                                                                                          | 64  |

|   | 3.3  | Summ    | nary                                                                                                       | 66  |

| 4 | Mix  | ed Rad  | ix Reed-Muller Expansions                                                                                  | 69  |

|   | 4.1  | Two-le  | evel mixed radix model                                                                                     | 69  |

|   | 4.2  | Radix   | reduction: $\mathfrak{p}^t \to \mathfrak{p}^u$ , $t > u$ Reed-Muller expansions                            | 72  |

|   | 4.3  | Radix   | extension: $\mathfrak{p} \to \mathfrak{p}^t$ Reed-Muller expansions $\ \ \ldots \ \ \ldots \ \ \ldots$     | 79  |

|   | 4.4  | Mixed   | l radix domain: $\left\{\mathfrak{p},\mathfrak{p}^{t}\right\} \to \mathfrak{p}^{t}$ Reed-Muller expansions | 85  |

|   | 4.5  | Binary  | y-to-q-nary Reed-Muller Expansions                                                                         | 90  |

|   | 4.6  | Summ    | nary                                                                                                       | 96  |

| 5 | Use  | Case a  | nd Experimental Results                                                                                    | 98  |

|   | 5.1  | Comp    | onent implementations                                                                                      | 99  |

|   |      | 5.1.1   | Implementation using RTL                                                                                   | 99  |

|   |      | 5.1.2   | Dynamic logic implementation                                                                               | 104 |

|   |      | 5.1.3   | Estimating component physical parameters                                                                   | 105 |

|   | 5.2  | Mapp    | ing specifications from one radix to another                                                               | 108 |

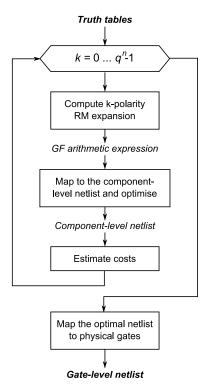

|   | 5.3  | Synth   | esis tool and optimisations                                                                                | 110 |

|   | 5.4  | Synth   | esis results                                                                                               | 113 |

|   |      |         |                                                                                                            |     |

### A.Rafiev: Mixed Radix Design Flow for Security Applications

|    | 5.5   | Summary                            | 124 |

|----|-------|------------------------------------|-----|

| 6  | Con   | clusion                            | 126 |

|    | 6.1   | Future work                        | 128 |

| A  | RM    | Mixed User Manual                  | 130 |

|    | A.1   | Tool features overview             | 130 |

|    | A.2   | Command line tool: rmmixed-cmd     | 131 |

|    | A.3   | Galois field expression calculator | 133 |

|    | A.4   | List of Tcl commands               | 135 |

|    | A.5   | Workflow example                   | 155 |

| Bi | hling | raphy                              | 158 |

## **List of Figures**

| 1.1  | Understanding the difference between general purpose MVL and                |    |

|------|-----------------------------------------------------------------------------|----|

|      | application-driven MVL synthesis flows                                      | 5  |

| 1.2  | Thesis flowchart                                                            | 10 |

| 2.1  | Types of cryptanalysis                                                      | 13 |

| 2.2  | Switching activity in CMOS inverter                                         | 16 |

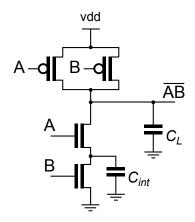

| 2.3  | CMOS NAND gate                                                              | 17 |

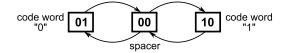

| 2.4  | Dual-rail (1-of-2) protocol                                                 | 18 |

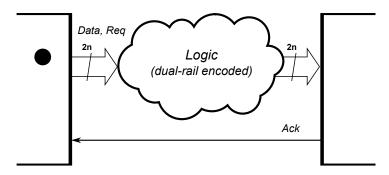

| 2.5  | 4-phase handshake                                                           | 19 |

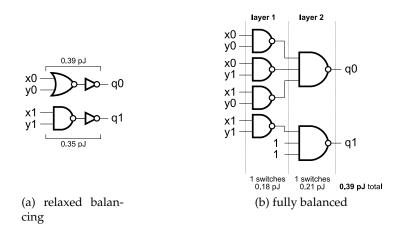

| 2.6  | RTL implementions of dual-rail encoded AND gate showing different           |    |

|      | levels of power balancing                                                   | 20 |

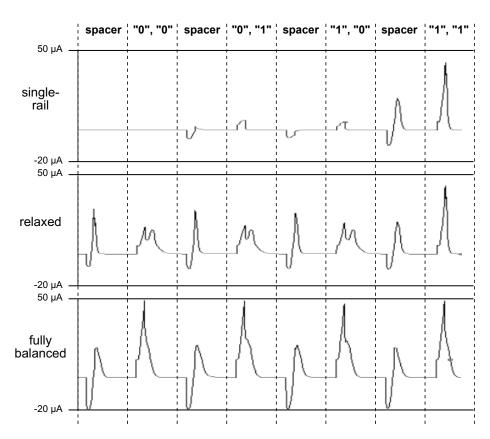

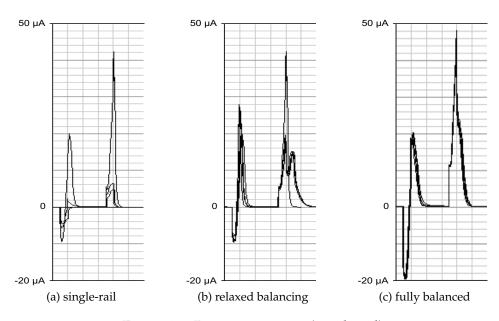

| 2.7  | Power signatures for different data transitions illustrating the imbalance. | 21 |

| 2.8  | Power signatures (overlayed)                                                | 21 |

| 2.9  | Addition and multiplication of $\{[0], [1], [x], [x+1]\}$                   | 28 |

| 2.10 | Addition and multiplication over some finite fields                         | 30 |

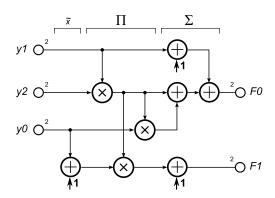

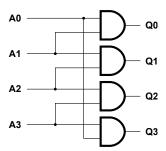

| 2.11 | Binary RM expansion, component-level schematic                              | 38 |

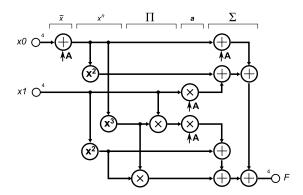

| 2.12 | Component-level schematic for uniform radix (quaternary) RM expansion.      | 40 |

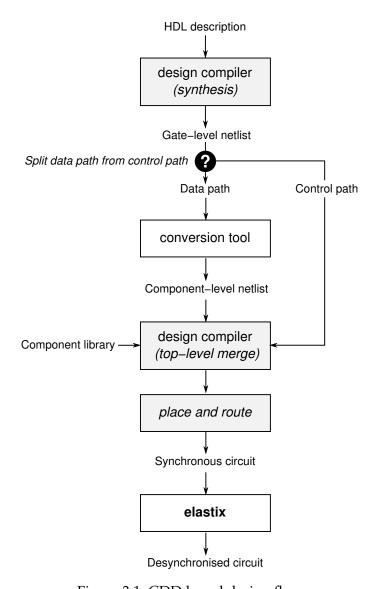

| 3.1  | CDD-based design flow                                                       | 44 |

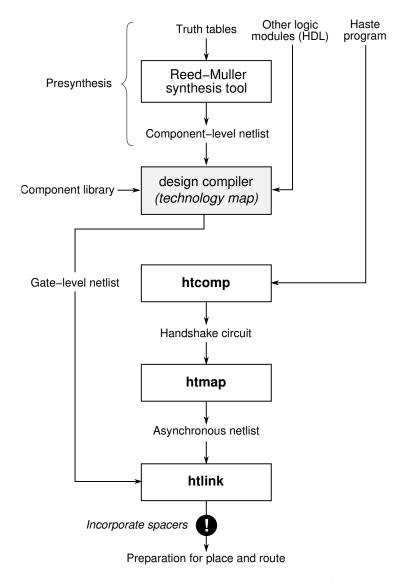

| 3.2  | Reed-Muller + Haste synthesis flow                                          | 46 |

| 3.3  | Example of a binary circuit that cannot be efficiently converted into a     |    |

|      | higher radix circuit                                                        | 50 |

| 3.4  | Mixed radix circuit as a result of binary-to-q-nary conversion                                                                         | 51  |

|------|----------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.5  | Types of gate groupings (considering the same original circuit)                                                                        | 52  |

| 3.6  | Understanding Q/B gates                                                                                                                | 53  |

| 3.7  | Mixed radix circuit using Q/B gates                                                                                                    | 53  |

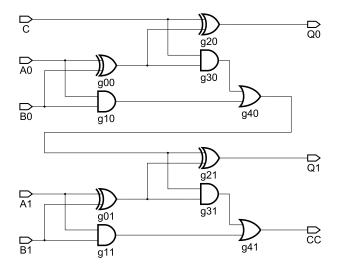

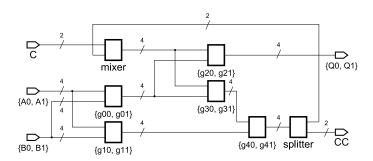

| 3.8  | Example original single-rail circuit: 2-bit adder.                                                                                     | 57  |

| 3.9  | 2-bit adder converted using bitwise regularity approach; gates are                                                                     |     |

|      | shown as "black boxes"                                                                                                                 | 57  |

| 3.10 | 2-bit adder converted using binary trees approach; gates are shown as                                                                  |     |

|      | "black boxes"                                                                                                                          | 61  |

| 3.11 | SPICE simulation results for AES S-box showing supply current, mA                                                                      | 67  |

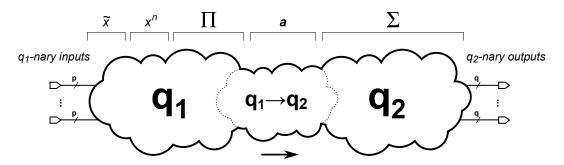

| 4.1  | Mixed radix circuit based on $q_1 \to q_2$ two-level radix model                                                                       | 72  |

| 4.2  | $r_{2}\left(x\right)+r_{2}\left(y\right)$ component specification for quaternary-to-binary case $% \left(x\right)+r_{2}\left(y\right)$ | 77  |

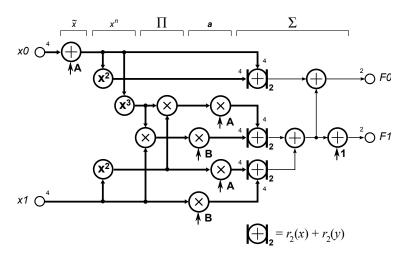

| 4.3  | Component-level schematic for quaternary-to-binary RM expansion                                                                        | 78  |

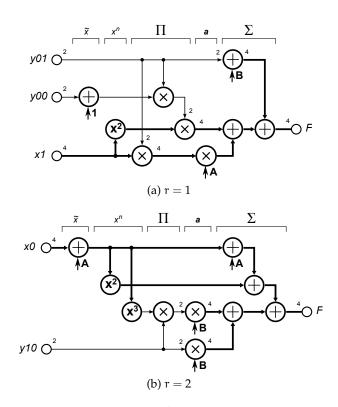

| 4.4  | Component-level schematic for mixed radix binary-to-quaternary RM                                                                      |     |

|      | expansion                                                                                                                              | 85  |

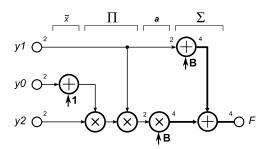

| 4.5  | Component-level schematic for mixed-to-quaternary RM expansions                                                                        | 90  |

| 4.6  | Component-level schematic for binary-to-ternary RM expansion                                                                           | 96  |

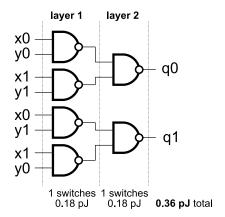

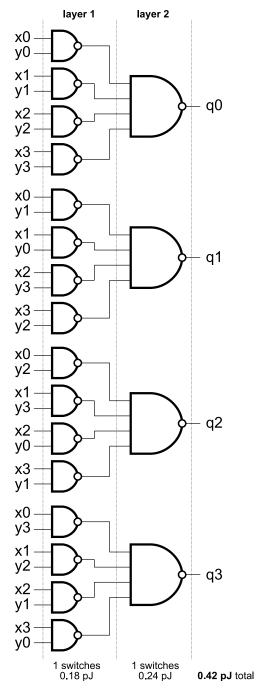

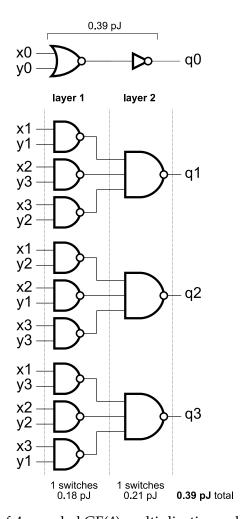

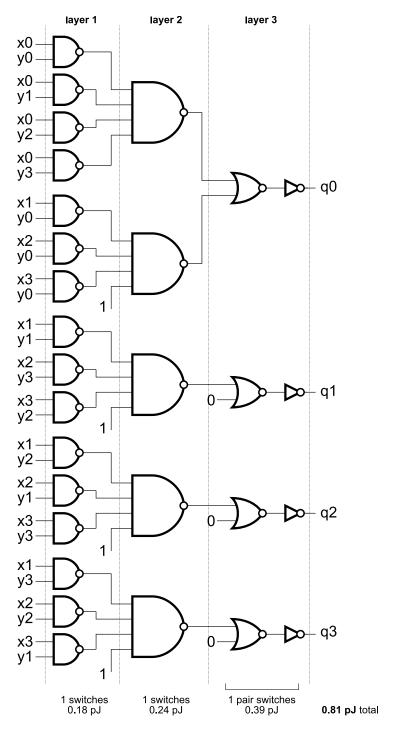

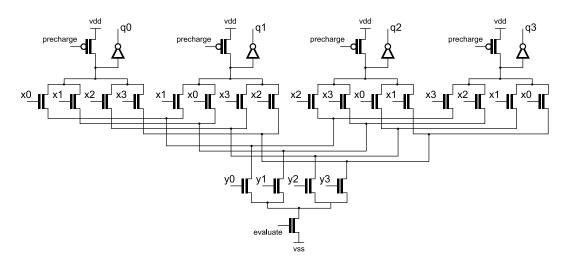

| 5.1  | Dual-rail encoded GF(2) addition                                                                                                       | 100 |

| 5.2  | 1-of-4 encoded GF(4) addition                                                                                                          | 101 |

| 5.3  | 1-of-4 encoded GF(4) multiplication, relaxed balancing                                                                                 | 102 |

| 5.4  | 1-of-4 encoded GF(4) multiplication, fully balanced                                                                                    | 103 |

| 5.5  | Dynamic logic implementation of 1-of-4 encoded GF(4) addition                                                                          | 104 |

| 5.6  | "Wire crossing" operations in 1-of-4: their implementations do not                                                                     |     |

|      | involve any logic                                                                                                                      | 107 |

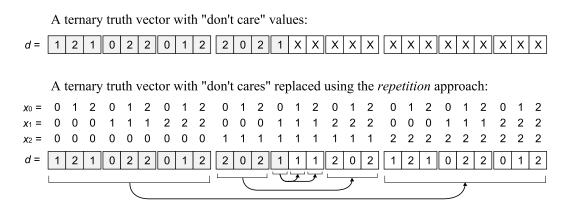

| 5.7  | An example of using the <i>repetition</i> heuristics to handle "don't care" values.                                                    | 109 |

| 5.8  | Reed-Muller based synthesis flow                                                                                                       | 111 |

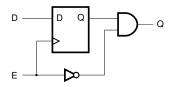

| A.1  | Simple spacer injecting register                                                                                                       | 156 |

## **List of Tables**

| 2.1  | Encoded binary, ternary and quaternary signals                            | 19  |

|------|---------------------------------------------------------------------------|-----|

| 2.2  | Dual-rail AND gate truth table and its single-rail equivalence            | 20  |

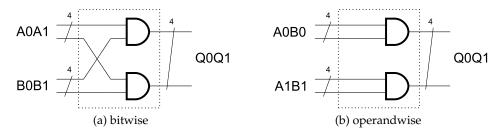

| 3.1  | Bitwise and operandwise quaternary operations example                     | 53  |

| 3.2  | Inversion in 1-of-4                                                       | 64  |

| 3.3  | Single rail circuits converted to dual-rail                               | 65  |

| 3.4  | Mixed radix conversion results                                            | 66  |

| 5.1  | GF component implementations                                              | 100 |

| 5.2  | Physical characteristics of GF components                                 | 106 |

| 5.3  | Estimated physical characteristics of the examples using Faraday 90nm     |     |

|      | library (relaxed balancing)                                               | 107 |

| 5.4  | Mixed domain results for different radix numbers; $r^*$ is the best radix |     |

|      | number found                                                              | 113 |

| 5.5  | Component level synthesis results                                         | 117 |

| 5.6  | Component level synthesis results (continued)                             | 118 |

| 5.7  | Component level synthesis results (continued)                             | 119 |

| 5.8  | Technology level synthesis results                                        | 120 |

| 5.9  | Technology level synthesis results (continued)                            | 121 |

| 5.10 | Technology level synthesis results (continued)                            | 122 |

| 5.11 | Comparison between conversion and synthesis results                       | 123 |

|     |                  | esign Flow for Security Applications |     |

|-----|------------------|--------------------------------------|-----|

| A.1 | gfexpr operators |                                      | 134 |

|     |                  |                                      |     |

|     |                  |                                      |     |

|     |                  |                                      |     |

|     |                  |                                      |     |

|     |                  |                                      |     |

|     |                  |                                      |     |

|     |                  |                                      |     |

|     |                  |                                      |     |

|     |                  |                                      |     |

|     |                  |                                      |     |

|     |                  |                                      |     |

|     |                  |                                      |     |

|     |                  |                                      |     |

|     |                  |                                      |     |

|     |                  |                                      |     |

## List of Publications

#### **Journal Papers**

· A. Rafiev, A. Mokhov, F. P. Burns, J. P. Murphy, A. Koelmans, and A. Yakovlev, "Mixed radix Reed-Muller expansions," *IEEE Transactions on Computers*, 2011. Accepted for publication.

#### Refereed conference papers

- · A. Rafiev, J. Murphy, D. Sokolov, and A. Yakovlev, "Conversion driven design of binary to mixed radix circuits," in *Proc. to ICCD*, 2008.

- · A. Rafiev, J. P. Murphy, and A. Yakovlev, "Quaternary Reed-Muller expansions of mixed radix arguments in cryptographic circuits," in *Proc. to 39th International Symposium on Multi-Valued Logic, ISMVL 2009*, 2009.

- · A. Rafiev, J. Murphy, and A. Yakovlev, "Secure design flow for asynchronous multivalued logic circuits," in *Proc. to 40th International Symposium on Multi-Valued Logic, ISMVL 2010*, May 2010.

#### Other conferences

- · A. Rafiev, J. Murphy, D. Sokolov, and A. Yakovlev, "Bitwise gate grouping algorithm for mixed radix conversion," in 20th UK Asynchronous Forum, 2008.

- · A. Rafiev, J. P. Murphy, A. Yakovlev. "Higher Radix and Mixed Radix Logic in Secure Devices From the Design Automation Perspective". in *Proc. to e-Smart*

Conference, SmartEvent '09, September 2009

#### **Technical reports and tools**

- · A. Rafiev, J. Murphy, D. Sokolov, and A. Yakovlev, "Investigating gate grouping algorithms for mixed radix conversion," tech. rep., Newcastle University, May 2008.

- · A. Rafiev, J. Murphy, and A. Yakovlev, "RTL implementations of GF(2) and GF(4) arithmetic components," tech. rep., Newcastle University, 2008.

- · RMMixed MVL synthesis tool. http://async.org.uk/sure/rmmixed.

## Chapter 1

### Introduction

In the modern world, digital devices take an important part in every aspect of our every day lives, including such sensitive areas as healthcare and finance. Large amount of personal and confidential information is stored online, and must be securely transferred between the client and the server. Financial operations are done "by wire", and every bank transaction is performed by some kind of electronic equipment. No doubt, all these aspects imply a great deal of trust in the devices involved. Ideally, we desire a system where the confidential information cannot be retrieved by an unauthorised person. In reality, this requires a huge effort to maintain the acceptable level of protection. Secure technologies have to continuously move forward chased by the constantly evolving techniques of the hackers.

Security solutions in the past were predominantly at the software level. The classic approach to cryptanalysis requires knowledge of ciphertext and, if available, plaintext. Cryptographic algorithms developed accordingly, minimising the possibility of getting the secret key by comparing the ciphertext to the plaintext (differential cryptanalysis [32]). With increasing complexity of the new encryption algorithms, more interest has been shown towards implementing cryptographic functions in hardware [60]. Circuit-level security, appraised for higher performance, has been also considered to be more secure. However, this has raised new problems as well.

Working entirely at the mathematical level, the traditional cryptography does not

take into account possible flaws of the actual implementations. Running on the real hardware, a cryptosystem dissipates different kind of information that may indirectly disclose the data being processed. For example, certain bits of a message may take a slightly longer time to compute or cause variations in the device's power consumption. The type of attacks that rely on this data is called side-channel attacks.

The major concern about side-channel attacks starts in 1998 with the discovery of the power analysis [39]. The idea of simple power analysis (SPA) is to examine device's power curve during the normal operation w.r.t. the cryptographic algorithm and the data being processed. For example, the operation of multiplication normally consumes more power than addition, hence the RSA algorithm [61, 63] can expose the private key while branching between these operations. The differential power analysis (DPA) uses power samples from multiple runs and performs statistical analysis in order to find the correlation and reveal the key. DPA allows breaking the commonly used algorithms in relatively short time. For instance, at the mathematical level, DES is perfectly resistant to differential cryptanalysis and takes exponential time to crack, while DPA requires only 1000 power samples [40]. The alarming efficiency of this attack drew the attention of both smartcard vendors and the cryptographic community, and even featured in an article in the New York Times [74]. The new standard on secure devices has been altered accordingly [5].

More details on DPA and countermeasures are given in Chapter 2. Among the number of described countermeasures, the presented work has been focused on power balancing and asynchronous system design only. The idea of power balancing is to encode and process the data signal in such a way that the operation over it will produce data independent power consumption due to the uniform switching of gates. Balanced encodings also imply more than 2 states of the signal, which leads to the multi-valued logic synthesis approach. In asynchronous designs the clock is replaced with handshake signals. Fuzzy circuit timing characteristics makes it difficult to sample power curves required for DPA.

The conventional industrial electronic design automation (EDA) tools, such as

Synopsys [7], Cadence [4], Magma [6] are very powerful, but they are targetted towards the general purpose devices and commonly used technologies. These tools are focusing on the primary issues of the market in order to deliver high quality solutions to the most of their customers. As a result, this approach often excludes many other aspects, such as multi-valued logic synthesis and asynchronous design. Industrial tools can be compared to an assembly line that can produce thousands of typical items with a push of a button. However, it's probably not the best choice if one needs something *special*.

Consequently, the development of secure devices requires much more design effort and should employ the methodologies beyond the "casual" electronic design. Some research has been made in an attempt to adjust the design flow [70, 11], but simple 'tweaks' do not give the best efficiency. In order to be ahead of the hackers in their technological pursuit, the designers need a very good tool support. The research presented in this thesis aims at formulating the unified design flow, filling in the gaps in the conventional design automation with the aid of the existing tools and development of the new ones.

#### 1.1 Motivation

Design flows used in industry are generally based on binary logic with a single bit of data represented as a single wire. This representation of data is called "single-rail" encoding. Multi-valued logic (MVL) synthesis tools also exist, e.g. MVSIS [27], and they are typically used to efficiently produce logic from higher-radix specifications, while the technology is still single-rail and processed using the standard flow and tools. The work described in the thesis, however, deals with the application areas where a simple binary encoding of data is either not applicable or gives poor results in terms of the delivered properties of the implementation.

Important features of certain encodings are exposed when used in connection with appropriate protocols. For example, single-rail is used with bundled data protocol [68] for asynchronous system design. From the application perspective, it is convenient

to consideer an encoding-protocol combination as a whole in order to explore their properties and possibilities.

Thus, m-of-n encoding combined with a spacer protocol is beneficial for security [17, 76], but for the price of increased area and power consumption. Chapter 2 outlines the problem; however, the discussion on the efficiency of certain countermeasures against the side-channel attacks is out of scope of this thesis. We are mostly interested in the fact that m-of-n codes imply MVL, which is problematic to design using the standard techniques.

It is also important that this particular type of encoding is not the only possible application area of MVL, and therefore the presented research. Possible use cases may include current-mode [13] or phase encoding [20], or any other protocol displaying the properties that single-rail does not have. On-chip interconnects [14] and low-power [33] devices are well-established applications for MVL that use special data representation at the physical level. The application of MVL may even go beyond microelectronics and, possibly, enter such areas as biocomputing [10].

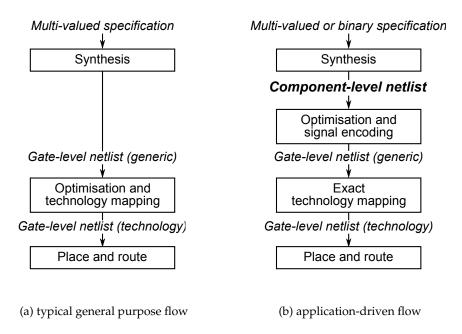

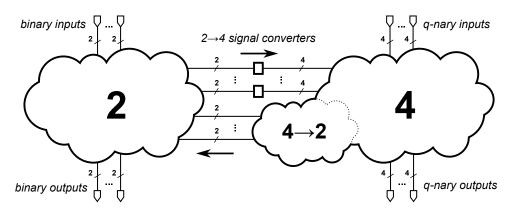

When the problem of using an encoding arises, the designers struggle to use the existing methodologies, while in fact a brand new design flow is warranted. This implies the need for an "application-driven" design flow. Figure 1.1 illustrates the difference between the approaches, crucial for understanding the motivation behind our research.

Typically, in a general purpose flow, the intermediate structure of MVL does not matter, because it produces the gate-level (binary) netlist that can be henceforth fed to a standard design compiler, where it is compacted and mapped into the certain technology. In contrast, an application-driven design flow explicitly defines an intermediate synthesis state known as the component-level netlist – a netlist of abstract arithmetic operations. The component-level netlist is an important link that carries along the radix information, which is essential for correct optimisation and data encoding. The consequent technology mapping does not alter the structure of the circuit; therefore, even if the final circuit is mapped into binary logic gates, compliance with the protocols

Figure 1.1: Understanding the difference between general purpose MVL and application-driven MVL synthesis flows

is preserved.

The physical implementation of arithmetic components directly depends on the encoding, thus the radix of signals, and has a strong impact on the characteristics of the circuit. Therefore the right choice of the radix is highly important; however, it is not always possible to find the globally optimal solution. Lower order radices require less logic to compute, and higher radices reduce the number of interconnects [45]. Our examples also show that this logic/interconnect trade-off is not evenly distributed among the arithmetic operations. Certain operations, if implemented with respect to the application requirements, have better physical characteristics in the lower radix logic, while other operations are more efficient in the higher radices. Consequently, when all the operations are combined, a single optimal radix cannot be worked out.

Hence, a methodology to partition the synthesised circuit into areas of different radices, whilst preserving the integrity and the properties of the original function, would be of great advantage. The ability to accommodate arithmetic components of different radices within a single circuit may provide the opportunity to incorporate the

benefit from each, and also provide another dimension in the logic/interconnect tradeoff. This describes a design philosophy where the radix is not a single fundamental idea but just a "tool" for computation, so the designer can use different "tools" together in order to achieve the best results.

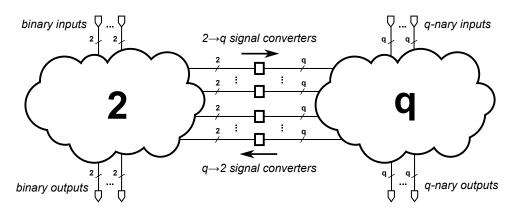

A straightforward solution to mix radices within a single circuit is to use signal conversion, as described in Chapter 3. For example, signal conversion logic can split quaternary signals into pairs of binary signals where appropriate, and vice versa. Conversion can be performed in a rather sophisticated way [71]. The main interest in the conversion approach is the possibility to apply it on top of the existing designs with a minimum computational cost. A major drawback, however, is that the structure of the circuit previously optimised for a certain radix becomes less efficient when converted to a different radix.

The problem can be avoided if mixed radices are applied directly at the logic synthesis stage. The proposal is to develop a mathematical theory for mixing radices in such a way that the radix conversion is done "by construction". Reed-Muller expansions over Galois fields can be chosen as a foundation for the approach. Since most cryptographic algorithms are based on Galois field arithmetic, we expect these functions to be efficiently mapped into Reed-Muller expansions.

Among a number of MVL synthesis techniques, Reed-Muller expansions over the Galois field of radix 4 are of great interest and have been developed for a number of years. The history of multi-valued Reed-Muller expansions started with evolving functional binary decision diagrams into the theory of Galois switching functions by applying finite field algebra [29, 52]. Later on, this approach has been developed into fixed and mixed polarity quaternary Reed-Muller expansions [28] – acknowledged by MVL research community due to their efficiency and testability. However, the high computational cost has prevented this approach from wide-spread and practical use. Thus, the later research has been focused mostly on optimising the computational algorithms [24, 59, 36, 25] and logic minimisation [34]. An attempt to implement multivalued Reed-Muller expansions in CMOS has been made as well [81].

Conveniently for the application-driven flow, a Reed-Muller expansion is produced in the form of an arithmetic expression that can be interpreted as a component-level netlist. The expansion itself is a two level function (sum of products), hence the idea to apply different radices to different levels gives the opportunity to develop a variety of two-radix combinations at the higher level of abstraction.

Green's method [28] has been chosen as an appropriate computation technique. The method is described in Chapter 2. Although it is known for its high computational complexity, it is straightforward and very flexible. At this stage of the research we are interested in the clarity rather than faster runtime. Optimisations can be applied after the entire mixed radix approach is proved valuable.

Given the motivation described in this section, the goal of the research can be defined as follows:

- · Implement mixed radix synthesis and conversion approaches as a set of tools.

- · Interface these new tools to the existing EDA tools, so together they form a complete design flow for secure devices.

- · Explore radix combinations and analyse their efficiency with respect to the circuit parameters and security properties.

#### 1.2 Contribution

Analysis of the existing EDA tools with respect to the security system design has been done prior to the main part of the research. The design flow structure has been proposed for conversion and synthesis approaches. Chapter 3 presents the proposed flows and discusses possible bottlenecks while interfacing between tools. The lack of tool support for encoded MVL synthesis and conversion confirmed the necessity of developing the new tools for these purposes.

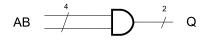

Conversion driven design approach has been elaborated and implemented for binary to mixed radix circuit conversion. The basic idea behind the conversion design is in the grouping of binary gates. Two types of gate grouping have been established: bitwise and operandwise. Corresponding gate grouping algorithms have been developed and implemented in a tool. The tool supports netlist to netlist conversion; structural Verilog has been chosen as the input and output format.

For synthesis approach, the theory of multi-valued Reed-Muller expansions over Galois field arithmetic has been extended to mixed radix Reed-Muller expansions. The notion of a radix model has been introduced. The developed two-level radix models, presented in Chapter 4, enable computation of the following mixed radix functions:

- · radix  $p^{u}$  functions of radix  $p^{t}$  arguments, where p is prime and  $t > u \ge 1$ ;

- · radix  $p^t$  functions of radix p arguments, where p is prime and t > 1;

- · radix  $p^t$  functions of combined radix p and radix  $p^t$  arguments, where p is prime and t>1;

- · radix q functions of binary arguments, where q is any valid Galois field order.

The theory of two-level radix models and corresponding computation methods are the primary theoretical contribution of the thesis.

In order to apply the new synthesis theory, the libraries of Galois field arithmetic components have been implemented in compliance with the security requirements and covering the radices 2, 3 and 4. The implementation has been made using runtime library cells and using custom design cells.

Reed-Muller based synthesis has been implemented in RMMixed tool [1]. The tool's features include:

- · computation of uniform radix and mixed radix Reed-Muller expansions in the form of a coefficient vector;

- · basic logic minimisation and mapping into component level netlists;

- · mapping from the component level to the gate level using provided library of components; the produced output is structural Verilog.

In addition, the tool can assist in calculating miscellaneous expressions in Galois field arithmetic. It can perform basic operations, matrix operations (including inversion), and operations on polynomials (including division). The tool is implemented in two versions: command line tool and TCL console.

The technique has been applied to a real life security related benchmarks in order to provide further motivation for its practical use. Proposed design flow has been tested down to the level of flat technology mapped netlist. Our theory allowed us to compare the efficiency of implemented component libraries in terms of energy consumption, area and delay in a range of radices and radix combinations. We have taken into account that, since the proposed theory is new, it lacks proper optimisation algorithms in comparison with well-developed binary synthesis system. Hence, the benchmark results have been analysed from the perspective of further improvement of the theory.

#### 1.3 Organisation of the thesis

The thesis is organised as follows.

**Chapter 1 (Introduction)** outlines the motivation and application background of the presented research.

#### **Chapter 2 (Background):**

- provides technical background for the hardware attacks and countermeasures,

outlines the prerequisites for secure design;

- · gives the necessary background theory on Galois fields and Reed-Muller expansions over Galois fields. The understanding of this theoretical part is essential for reading Chapter 4.

**Chapter 3 (Baseline Research)** proposes the design flow stucture for conversion and synthesis approaches, gives an overview of the existing tools and outlines the requirements for the new tool. It also presents the conversion driven design

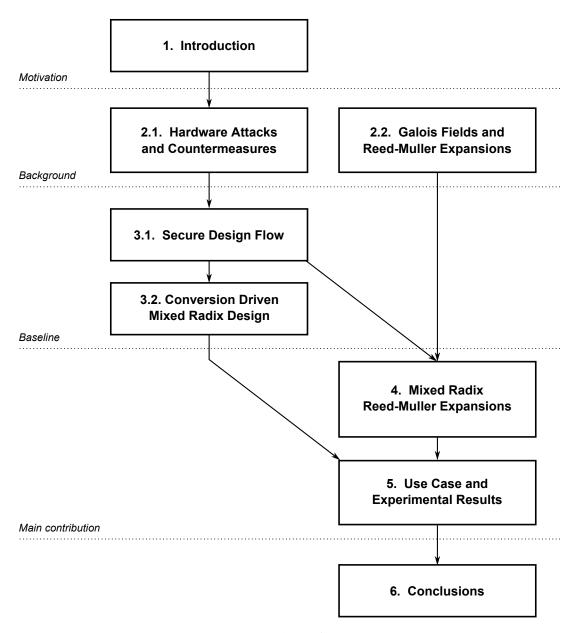

Figure 1.2: Thesis flowchart

approach – theoretical part, algorithms and benchmark results – which provides a baseline and further motivation for the main theoretical part of the thesis.

- **Chapter 4 (Mixed Radix Reed-Muller Expansions)** presents the theory of mixed radix Reed-Muller expansions used for logic synthesis in the proposed secure design flow.

- **Chapter 5 (Use Case and Experimental Results)** describes in details the Reed-Muller synthesis-based secure design flow, implemented tool and component libraries and discusses the benchmark results.

- **Chapter 6 (Conclusion)** concludes the work and outlines the possible future development of the research.

- **Appendix A (RMMixed User Manual)** contains the user manual for Reed-Muller synthesis tool.

Some chapters present independent approaches, so there is a certain concurrency in the structure of the thesis. Figure 1.2 illustrates the flow.

### **Chapter 2**

## **Background**

The presented research connects two independent aspects: hardware level security and the theory of multi-valued Reed-Muller expansions. This chapter covers the background information for both.

#### 2.1 Hardware Attacks and Countermeasures

As has been discussed in Chapter 1, in order to make the device sufficiently protected against the hardware attacks, certain guidelines must be followed. This section describes the possible dangers and gives the basic understanding of the protection at the hardware level using the special type of signal encoding, known as switching balanced codes.

#### 2.1.1 Types of attacks and countermeasures

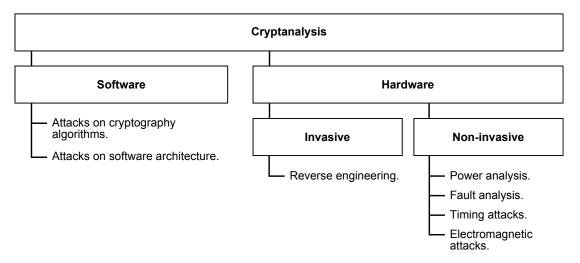

Cryptanalysis is mainly divided into software attacks and hardware attacks. Figure 2.1 shows different types of attacks grouped by the field of action [60].

Software cryptanalysis is targetted directly at the cryptographic algorithms, acting at the mathematical level or the level of programming language. This type of attack is not addressed in thie presented research.

Figure 2.1: Types of cryptanalysis

Hardware attacks behave indirectly, using the imperfections of the actual implementations rather than those of the algorithms. These attacks are divided into two major categories: invasive and non-invasive (side-channel). Based on reverse engineering, invasive attacks require special laboratory equipment and destroy packaging in the process while side-channel attacks do not require in-depth knowledge of the technology and use simple equipment [60]. With respect to the physical parameter used as the source of information, side-channel attacks are known as power analysis, timing analysis, electromagnetic analysis and fault analysis.

During the *power analysis* the hacker monitors data-dependent power consumption of the device during the normal operation [39]. The method relies on the following fundamental hypothesis: there exists an intermediate variable that appears during the computation of the algorithm, such that knowing a few key bits allows the attacker to decide whether two inputs (respectively two outputs) do or do not give the same value for this variable [18]. Consequently, splitting such variables and combining them with random values can protect against power analysis. This method is called *masking*, and its major advantage with respect to this work is that it can be implemented using standard EDA software. However, recent research has discovered a mathematical modification of power analysis that can break the masking approach [48].

Another countermeasure to the power analysis is to make the device's power consumption data-independent, it is called *power balancing*. A number of methods to equalise the power signatures using specific representation of data signals over physical wires, e.g. m-of-n codes, were proposed in [17, 46, 67, 43]. M-of-n codes are an encoding scheme in which data is represented using n wires and where m of them are set to an active level (usually high). A protocol separating data using dummy symbols (spacers) is called a *spacer protocol*. In this configuration, the number of wires that switch during the cycle is constant, so is the power consumption. A particular emphasis has so far only been put on dual-rail (1-of-2) codes for binary radix and 1-of-4 for quaternary logic. As a price for the improved resistance to power attacks the approach results in an overhead with respect to the overall power consumption of the system. More details on power balancing using m-of-n codes is given in Subsection 2.1.2.

*Electromagnetic analysis* is similar to power analysis but uses data-dependent electromagnetic emission instead of power consumption [26]. The method of equalising switching activity of the logic can work in this case as well.

Another way to make the hackers' life harder is to randomise the timing properties of the circuits, so it would become difficult to perform correct sampling of physical parameters during operation. The simplest method is to insert random delays in the clock cycles. The most reliable countermeasure however is an asynchronous logic design (i.e. self-timed circuits) [46]. Asynchronously working device modules cause overlays in power consumption, thus making it practically impossible to distinguish between single operations. This can help against the *timing analysis*, which uses the amount of time required for running non constant cryptographic algorithm to retrieve information about the data processed [41].

*Fault analysis* is an attack which uses abnormal environment conditions, e.g. glitches on power or clock signals, so malfunction of the device can create a window for vulnerabilities [15]. A known countermeasure for this attack is using fault-tolerant protocols. M-of-n codes are fault-tolerant as they imply relatively simple fault detection

logic [14].

Since m-of-n codes and clockless design approach appear to be the most universal countermeasures, the following discussion on the secure design is presented in relation to these ideas.

#### 2.1.2 Power balancing using m-of-n codes

Power balancing is one of the countermeasures to power analysis. It's concept is to create data-independent power consumption using so-called switching balanced codes and power balanced implementations of logic gates.

#### **CMOS** power

Digital circuits consume power whenever they perform computation. Using a constant power supply and input signals to execute, logic cells draw current from the supply and dissipate energy as heat. Power consumption of the circuit is a sum of the power consumption of the individual logic cells.

The overall power dissipation  $P_{total}$  of a static CMOS circuit is composed of three components: switching power  $P_{switch}$ , short-circuit power  $P_{short}$  and leakage power  $P_{leak}$ ;

$$P_{total} = P_{switch} + P_{short} + P_{leak}$$

.

Short-circuit power  $P_{short}$  is dissipating due to the presence of a direct path between supply and ground during logical transitions (0  $\rightarrow$  1 or 1  $\rightarrow$  0). Leakage power dissipation  $P_{leak}$ , known as static power consumption, comes from different sources: sub-threshold voltage, tunneling through gate oxide, and through reverse biased diodes. Although at the submicron level the leakage power becomes a relevant factor, short-circuit power and leakage power are considered relatively small compared to the switching power [47].

Switching power P<sub>switch</sub>, also called dynamic power or dynamic dissipation, is attributed to the charging and discharging of capacitances: gate outputs (load capacit-

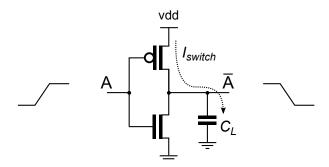

Figure 2.2: Switching activity in CMOS inverter

ances) and transistor-to-transistor connections inside gates (intrinsic capacitances) [38];

$$P_{switch} = P_{load} + P_{internal}$$

.

An inverter, shown in Figure 2.2, does not have intrinsic capacitances, hence the load power is equivalent to the dynamic power. During a  $0 \to 1$  transition, current flows from the supply charging the load capacitance  $C_L$ . Half of the energy is stored in the load capacitor, and the other half is dissipated by the pull-up PMOS network. During a discharging transition  $1 \to 0$  current flows from the load to ground, and the energy stored in the load capacitor is dissipated by the pull-down NMOS network; no energy is drawn from the supply. Each switching cycle takes a fixed amount of energy equal to  $C_L \cdot V_{\rm dd}^2$ . The inverter's average dynamic power consumption over some time period is the integral of the instantaneous power multiplied by switching frequency f of  $0 \to 1$  transitions.

Other CMOS gates and networks of interconnected gates display switching properties other than those of a inverter. Furthermore, they exhibit "lazy switching" characteristics causing a memory effect, where the logical values of outputs are retained from the earlier computation cycles. This memory effect occurs when a gate output computes to the same logical value as the existing output; this naturally happens when more than one set of inputs maps to the same outputs. Similarly, internal nodes exhibit such memory effects and will discharge or charge deterministically. For example, consider the 2-input NAND gate shown in Figure 2.3. It has two parallel

Figure 2.3: CMOS NAND gate

PMOS transistors and two NMOS transistors connected in series forming the internal transistor-to-transistor capacitance  $C_{int}$ . Assume the inputs are either 00 or 01 and  $C_{int}$  is discharged; if in the next cycle 00 or 01 arrives, then the output will retain its existing value and no power will be consumed. If in the next cycle 10 arrives, the output will retain its value, but  $C_{int}$  will charge, meaning it can freely discharge at any point in subsequent cycles.

Estimating the power consumption of complex gates and networks requires taking into account switching statistics. For instance, from the truth table of the NAND gate the probability of  $0 \to 1$  transition is 3/16, the probability of  $1 \to 0$  transition is also 3/16, and the probability that the output will be retained is 10/16. The concept of switching activity is used to determine the probability of the output switching. For N periods of  $0 \to 1$  and  $1 \to 0$  transitions, the switching activity  $\alpha$  determines how many  $0 \to 1$  transitions occur. Thus,

$$P_{load} = \alpha C_L \cdot f \cdot V_{dd}^2,$$

where  $\alpha$  is the switching activity,  $C_L$  is output capacitance, and f is the switching frequency of  $0 \to 1$  transitions. For the inverter,  $\alpha = 1$  and  $P_{load} = C_L \cdot f \cdot V_{dd}^2$ .

$$P_{internal} = \sum_{i=1}^{n} \alpha_i \cdot C_i \cdot f \cdot V_i \cdot V_{dd},$$

Figure 2.4: Dual-rail (1-of-2) protocol

estimated using switching activity  $\alpha_i$ , parasitic capacitance  $C_i$  and internal voltage  $V_i$  for each node i. However, in most cases  $C_L$  is considered to be much bigger than the sum of  $C_i$ , so the internal power consumption is often neglected, and the switching power of a particular cell is determined by its load power  $P_{load}$ .

#### m-of-n codes

Since the main source of power consumption in the CMOS netlist is the switching activity of gates, the method to equalise it is to produce a symmetric switching. This can be achieved using switching balanced codes, for example m-of-n codes.

*m-of-n codes* are an encoding scheme in which data is represented using n wires and where m of them are set to an active level (usually high).

The simplest example is 1-of-2 code, called dual-rail, which uses a pair of wires per bit of information d; one wire  $d_1$  is used for signaling a logic 1 (or true), and another wire  $d_0$  is used for signaling logic 0 (or false). Traditionally this code is employed to represent data in self-timed circuits [21]. Viewed together the  $d_1d_0$  wire pair is a codeword;  $d_1d_0 = 10$  and  $d_1d_0 = 01$  represent "valid data" (logic 0 and logic 1 respectively) and  $d_1d_0 = 00$  represents "no data" ("spacer" or NULL). The codeword  $d_1d_0 = 11$  is not used, and a transition between valid codewords must be done via the spacer, as illustrated in Figure 2.4.

In asynchronous circuits, dual-rail protocol is used to create a 4-phase handshake protocol, which replaces the clock signal. An abstract view of 4-phase handshaking consist of (1) the sender issues a valid codeword, (2) the receiver absorbs the codeword and sets acknowledge high, (3) the sender responds by issuing the empty codeword, and (4) the receiver acknowledges this by taking acknowledge low [68]. Dual-rail handshake circuit is shown in Figure 2.5.

Figure 2.5: 4-phase handshake

Table 2.1: Encoded binary, ternary and quaternary signals.

| radix      | value            | encoded signal |

|------------|------------------|----------------|

| 1-         | of-2 (dual-rail) |                |

|            | 0                | 01             |

| binary     | 1                | 10             |

|            | NULL             | 00             |

|            | 1-of-3           |                |

|            | 0                | 001            |

| ternary    | 1                | 010            |

|            | 2                | 100            |

|            | NULL             | 000            |

|            | 1-of-4           |                |

|            | 0                | 0001           |

|            | 1                | 0010           |

| quaternary | 2 or A           | 0100           |

|            | 3 or B           | 1000           |

|            | NULL             | 0000           |

An important feature of the dual-rail encoding is its balanced power consumption which facilitates circuit resistance to power analysis attacks. In particular, switching from a spacer to any code word consumes the same amount of power due to the symmetry between rails. The same is true for all m-of-n generalised encodings. Apart from dual-rail we use 1-of-4 to represent quaternary signals and 1-of-3 for ternary. Table 2.1 shows how these encodings can be applied.

|   | single-rail |        | dual-rail                                   |                  |                  |

|---|-------------|--------|---------------------------------------------|------------------|------------------|

| χ | y           | q = xy | $\mathbf{x} = (\mathbf{x}_1, \mathbf{x}_0)$ | $y = (y_1, y_0)$ | $q = (q_1, q_0)$ |

| 0 | 0           | 0      | 01                                          | 01               | 01               |

| 0 | 1           | 0      | 01                                          | 10               | 01               |

| 1 | 0           | 0      | 10                                          | 01               | 01               |

| 1 | 1           | 1      | 10                                          | 10               | 10               |

| _ | _           | _      | 00                                          | XX               | 00               |

| _ | _           | _      | XX                                          | 00               | 00               |

Table 2.2: Dual-rail AND gate truth table and its single-rail equivalence

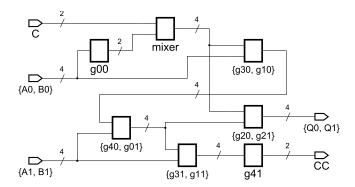

Figure 2.6: RTL implementions of dual-rail encoded AND gate showing different levels of power balancing.

#### Cell implementations for balancing

Since the primary attribute of these codes is balanced switching, the components should also display this feature. Ideally the form and size of the power signature of a component should be symmetrical with respect to switching from spacer to data and vice versa. Usually this is achieved by introducing additional dummy-logic paths. For real life examples an ideal symmetry is impossible, but the components can have certain maximum balancing allowed by the technology capabilities. Such implementations are henceforth called *fully balanced*. In contrast, the notion of *relaxed balancing* is used when the security is slightly compromised for significant power and area gains

To demonstrate the difference between fully balanced components and components

Figure 2.7: Power signatures for different data transitions illustrating the imbalance.

Figure 2.8: Power signatures (overlayed)

with so-called "relaxed" balancing, consider a binary AND gate. Table 2.2 shows its truth table. A straightforward dual-rail implementation is shown in Figure 2.6(a). Switching dual-rail inputs  $[x=(x_1,x_0),y=(y_1,y_0)]$  from the spacer value to ["0","0"], ["1","0"] and ["0","1"] causes the NOR gate to fire. Switching from the spacer to ["1","1"] fires the NAND gate. NAND and NOR gates have different switching energy values thus in this case the component is weakly balanced.

In order to improve the balance we have to add logic paths that make the structure of the component symmetrical with respect to the switching activity of the gates and input signals; this is shown in Figure 2.6(b). In the spacer state all inputs are set to low, thus all the outputs of the 2-input NAND gates in the first layer are set to high, precharging the NAND gates in the second layer. Arrival of a data signal (["0", "0"], ["0", "1"], ["1", "0"], or ["1", "1"]) causes exactly one gate from the first layer to fire. This will produce only one 0 signal to the second layer, switching one of 3-input NANDs. Addition of constant inputs to one of the gates guarantees that all gates in each layer are the same.

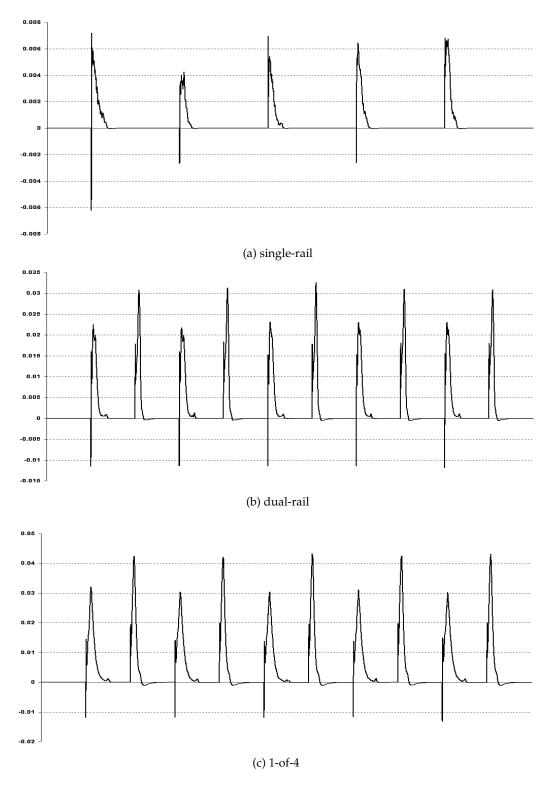

Although there are certain unavoidable aspects of the technology, such as transistor level asymmetry which introduces some imbalance even to this design, any implementation is acceptable if it fits the requirements of the security standard [5]. For the same reason, the structure shown in Figure 2.6(a) might also be sufficient, since the difference in switching energies is not large. Figure 2.7 displays the analogue simulation results for the components shown in Figure 2.6 along with the non-encoded single-rail implementation. As discussed above, fully balanced implementation provides maximum security, while non-encoded circuit is totally unprotected. This is a typical illustration why the standard design flow and tools cannot be directly applied in this area.

A detailed discussion on secure implementations and power balancing can also be found in [31].

#### 2.2 Galois Fields and Reed-Muller Expansions

The section gives a brief yet sufficient background on Galois fields arithmetic, multivalued Reed-Muller expansions over Galois fields and Green's direct method of computation. The understanding of these theoretical aspects is essential for understanding the theory of mixed radix Reed-Muller expansions. All the theorems in this section are given without proofs. The proofs can be found in the referenced literature. For the extended study of the Galois theory, the reader may refer to [30, 62, 66].

#### 2.2.1 Galois Fields

#### Rings

**Definition 2.1.** Let R be a nonempty set on which we have two closed binary operations, denoted by + and  $\cdot$ , i.e.  $a + b \in R$  and  $a \cdot b \in R$  for all  $a, b \in R$ . Then  $(R, +, \cdot)$  is a *ring* if for all  $a, b, c, \in R$  the following conditions are satisfied [30]:

- 1. Commutative law of +: a + b = b + a

- 2. Associative law of +: a + (b + c) = (a + b) + c

- 3. There exists a zero element [66] (also called additive identity [30]), denoted as  $0 \in R$ , such that a + 0 = 0 + a = a for every a in R.

- 4. For each  $a \in R$  there is an element  $b \in R$  with a + b = b + a = 0. This element is called the *additive inverse* of a and usually denoted as -a.

- 5. Associative law of  $\cdot$ :  $a \cdot (b \cdot c) = (a \cdot b) \cdot c$

- 6. Distributive law of  $\cdot$  over +:

$$a \cdot (b + c) = a \cdot b + a \cdot c$$

$$(b+c) \cdot a = b \cdot a + c \cdot a$$

If, in addition,  $a \cdot b = b \cdot a$  for all  $a, b \in R$  then R is called a *commutative ring*.

A *ring with unity* is a ring R containing an element, denoted by 1 and called the *unity* or the *multiplicative identity*, such that for all  $\alpha \in R$

$$1 \cdot a = a \cdot 1 = a$$

**Definition 2.2.** An *integral domain* is a commutative ring with unity R such that the equation  $ab = 0 \in R$  implies that either a = 0 or b = 0 [66].

**Theorem 2.1.** A commutative ring with unity R is an integral domain if and only if it satisfies the cancellation law: if ra = rb and  $r \neq 0$ , then a = b [62].

**Definition 2.3.** Let R be a ring with unity. If  $a \in R$  and there exists  $b \in R$  such that ab = ba = 1, then b is called a *multiplicative inverse* of a (usually denoted as  $a^{-1}$ ) and a is called a *unit* of R. The element b is also a unit of R [30].

**Definition 2.4.** Commutative ring with unity R is called a *field* if every nonzero element of R is a unit [30].

## $\mathbb{Z}_n$ rings

The presented research uses *finite fields*, i.e. fields with finite number of elements. The simpliest example is  $\mathbb{Z}_n$  rings.

For a fixed positive integer n, define the ring  $\mathbb{Z}_n$  of integers modulo n as follows [62]. Its elements are the subsets of  $\mathbb{Z}$

$$[a] = \{m \in \mathbb{Z} : m \equiv a \text{ (mod n)}\}$$

$$= \{m \in \mathbb{Z} : m = a + kn \text{ for some } k \in \mathbb{Z}\}$$

where  $a \in \mathbb{Z}$  ([a] is called the congruence class of a mod n). Addition and multiplication are given by

$$[a] + [b] = [a + b]$$

$$[a][b] = [ab]$$

and [1] is unity. It is routine to check that addition and miltiplication are well defined (that is, if  $a \equiv a' \pmod{n}$  and  $b \equiv b' \pmod{n}$ , then  $a + b \equiv a' + b' \pmod{n}$  and  $ab \equiv a'b' \pmod{n}$ ; i.e, [a] + [b] = [a'] + [b'] and [a] [b] = [a'] [b'], and that  $\mathbb{Z}_n$  is a ring under these operations [62].

It is a common practice, when working with  $\mathbb{Z}_n$ , to eliminate brackets from the notation. In  $\mathbb{Z}_3$ , for example, it is correct to write 2+2=1.

**Theorem 2.2.**  $\mathbb{Z}_n$  *is an integral domain if and only if* n *is prime* [62].

**Theorem 2.3.** If p is a prime, then  $\mathbb{Z}_p$  is a field [62].

# Polynomial rings over fields

**Definition 2.5.** Let R be a ring. The ring of polynomials in the transcendental (indeterminate [30]) variable x, with the coefficients in R, is denoted by R [x] and consists of the set of all formal expressions of the form

$$f(x) = a_n x^n + a_{n-1} x^{n-1} + ... + a_1 x + a_0$$

with each  $a_i \in R$  [66]. The element  $a_t \in R$  is called the coefficient of  $x^t$  in f(x) and two polynomials are considered to be equal if and only if, for each t, their nonzero coefficients of  $x^t$  are equal. The *zero polynomial* has every coefficient equal to zero and is abbreviated to 0.

The *degree* of f(x) is the largest n such that the coefficient of  $x^n$  is nonzero and is denoted by deg (f(x)). Hence deg (0) = 0, deg  $(a_0) = 0$  and deg (ax + b) = 1.

If  $g(x) = b_m x^m + b_{m-1} x^{m-1} + \ldots + b_0$  we define the *sum*, f(x) + g(x), to be the polynomial whose coefficient of  $x^t$  is  $a_t + b_t$ , and we define the *product*, f(x)g(x), to be the polynomial whose coefficient of  $x^t$  is

$$a_t b_0 + a_{t-1} b_1 + \ldots + a_1 b_{t-1} + a_0 b_t$$

# **Corollary 1.** *Let* R[x] *be a polynomial ring.*

- 1. If R is commutative, then R[x] is commutative.

- 2. If R is a ring with unity, then R[x] is a ring with unity.

- 3. R[x] is an integral domain if and only if R is an integral domain [30].

# Irreducible polymonials: finite fields

We now wish to construct finite fields other than those of type  $(\mathbb{Z}_p, +, \cdot)$ , where p is a prime. The construction will use the following special polynomials.

**Definition 2.6.** Let  $f(x) \in F[x]$ , with F a field and deg  $(f(x)) \ge 2$ . We call f(x) reducible (over F) if there exists g(x),  $h(x) \in F[x]$ , where f(x) = g(x)h(x) and each of g(x), h(x) has degree  $\ge 1$ . If f(x) is not reducible it is called *irreducible*, or *prime* [30].

**Theorem 2.4.** Let  $s(x) \in F[x]$ ,  $s(x) \neq 0$ . Define relation  $\Re$  on F[x] by  $f(x) \Re g(x)$  if f(x) - g(x) = f(x) is an equivalence relation on F[x].

When the situation described in Theorem 2.4 occurs, we say that f(x) is *congruent* to g(x) *modulo* s(x) and write  $f(x) \equiv g(x) \pmod{s(x)}$ . The relation  $\mathcal{R}$  is referred as *congruence modulo* s(x).

Let us examine the equivalence classes of one such relation. Let  $s\left(x\right)=x^2+x+1\in$

#### $\mathbb{Z}_2[x]$ . Then

$$[0] = [x^{2} + x + 1] = \{0, x^{2} + x + 1, x (x^{2} + x + 1), (x + 1) (x^{2} + x + 1), \dots\}$$

$$= \{t (x) (x^{2} + x + 1) | t (x) \in \mathbb{Z}_{2} [x] \}$$

$$[1] = \{1, x^{2} + x, x (x^{2} + x + 1) + 1, (x + 1) (x^{2} + x + 1) + 1, \dots\}$$

$$= \{t (x) (x^{2} + x + 1) + 1 | t (x) \in \mathbb{Z}_{2} [x] \}$$

$$[x] = \{x, x^{2} + 1, x (x^{2} + x + 1) + x, (x + 1) (x^{2} + x + 1) + x, \dots\}$$

$$= \{t (x) (x^{2} + x + 1) + x | t (x) \in \mathbb{Z}_{2} [x] \}$$

$$[x + 1] = \{x + 1, x^{2}, x (x^{2} + x + 1) + (x + 1), (x + 1) (x^{2} + x + 1) + (x + 1), \dots\}$$

$$= \{t (x) (x^{2} + x + 1) + (x + 1) | t (x) \in \mathbb{Z}_{2} [x] \}$$

We now place a ring structure on these equivalence classes [30]. Recalling how this was accomplished in Subsection 2.2.1 for  $\mathbb{Z}_n$ , we define addition by [f(x)] + [g(x)] = [f(x) + g(x)]. Since  $\deg(f(x) + g(x)) \leq \max\{\deg(f(x)), \deg(g(x))\}$ , we can always find the equivalence class for [f(x) + g(x)]. Here, for example, [x] + [x + 1] = [x + (x + 1)] = [2x + 1] = [1] because 2 = 0 in  $\mathbb{Z}_2$ .

Defining the multiplication of these equivalence classes is a bit more tricky. For instance, what is [x][x]? If, in general, we define [f(x)][g(x)] = [f(x)g(x)], it is possible that  $\deg(f(x)g(x)) \geqslant \deg(s(x))$ , so we may not readily find [f(x)g(x)] in the list of equivalence classes. However, if  $\deg(f(x)g(x)) \geqslant \deg(s(x))$ , then using the division algorithm, we can write f(x)g(x) = g(x)s(x) + r(x), where r(x) = 0 or  $\deg(r(x)) < \deg(s(x))$ . With f(x)g(x) = g(x)s(x) + r(x) it follows that  $f(x)g(x) \equiv r(x)$  (mod s(x)), and we define [f(x)g(x)] = [r(x)], where r(x) does occur in the list of equivalence classes.

From these observations we construct tables, shown in Figure 2.9, for the addition and multiplication of  $\{[0], [1], [x], [x+1]\}$ . In these tables we write  $\mathfrak a$  for  $[\mathfrak a]$ .

**Theorem 2.5.** Let s(x) be a nonzero polynomial in F[x].

1. The equivalence classes of F[x] for the relation of congruence modulo s(x) form a

| +     | 0   | 1     | χ     | x + 1 |     | 0 | 1     | x     | x + 1 |

|-------|-----|-------|-------|-------|-----|---|-------|-------|-------|

|       |     | 1     |       |       | 0   | 0 | 0     | 0     | 0     |

| 1     | 1   | 0     | x + 1 | χ     | 1   | 0 | 1     | χ     | x + 1 |

| χ     | x   | x + 1 | 0     | 1     | χ   | 0 | χ     | x + 1 | 1     |

| x + 1 | x+1 | χ     | 1     | 0     | x+1 | 0 | x + 1 | 1     | χ     |

Figure 2.9: Addition and multiplication of  $\{[0], [1], [x], [x+1]\}$

commutative ring with unity under the closed binary operations

$$[f(x) + g(x)] = [f(x)] + [g(x)]$$

$$[f(x)][g(x)] = [f(x)g(x)] = [r(x)]$$

where r(x) is the remainder obtained upon dividing f(x) g(x) by s(x). This ring is denoted by F[x]/(s(x)).

- 2. If s(x) is irreducible in F[x], then F[x]/(s(x)) is a field.

- 3. If |F| = q and deg(s(x)) = n, then F[x]/(s(x)) contains  $q^n$  elements [30].

**Definition 2.7.** Let  $(R, +, \cdot)$  be a ring. If there is a least positive integer n such that nr = r + ... + r (ntimes)  $= 0 \in R$  for all  $r \in R$ , then we say that R has *characteristic* n and write char (R) = n. When no such integer exists, R said to have characteristic 0.

**Theorem 2.6.** *Let*  $(F, +, \cdot)$  *be a field. If* char (F) > 0, *then* char (F) *must be prime.*

**Theorem 2.7.** A finite field F has order  $p^t$ , where p is a prime and  $t \in \mathbb{Z}^+$ .

**Theorem 2.8.** (Galois) For every prime p and every positive integer t, there exists a field having exactly  $p^t$  elements [62].

**Corollary 2.** (E.H. Moore) Any two finite fields of order p<sup>t</sup> are isomorphic [62].

These fields were discovered by the French mathematician Evariste Galois (1811–1832) in his work on the nonexistence of formulas for solving general polynomial equations of degree  $\geq 5$  over Q. As a result, a finite field of order p<sup>t</sup> is denoted by GF (p<sup>t</sup>), where the letters GF stand for *Galois field*.

**Definition 2.8.** If E is a field and F is a subset which, under the operations of E, is itself a field then F is called a *subfield* of E and E is an *extension* of F [66]. GF(p) is a subfield of GF( $p^t$ ) for any prime p and t > 1.

**Definition 2.9.** A homomorphism  $\psi : F \to F'$  of fields is a ring map

$$\left(\psi\left(\alpha+b\right)=\psi\left(\alpha\right)+\psi\left(b\right),\psi\left(\alpha b\right)=\psi\left(\alpha\right)\psi\left(b\right)\right)$$

such that  $\psi(1) = 1$ . If  $\psi$  is one-to-one and onto, it is an *isomorphism* (an *automorphism* if F = F'). [66].

If the fields F and F' are homomorphic only with respect to one of the operations, i.e. either  $\psi(a+b) = \psi(a) + \psi(b)$  or  $\psi(ab) = \psi(a) \psi(b)$  is true for  $\psi : F \to F'$ , the field F is called a *subgroup* of F' under the operation of addition (multiplication).

The next subsection summarises the properties of Galois fields used in the definition and the computation of Reed-Muller expansions.

#### Galois field properties overview

For any  $q = p^t$ , where p is a prime number and integer  $t \ge 1$ , a Galois field GF(q) is defined as an algebraic structure consisting of:

- 1. q elements;

- 2. closed binary operations + and  $\cdot$  called addition and multiplication respectively, i.e.  $a+b\in GF(q)$  and  $a\cdot b\in GF(q)$  for all  $a,b\in GF(q)$ ;

- 3. elements 0 and 1 such that a + 0 = a and  $a \cdot 1 = a$  for all  $x \in GF(q)$ .

- 4. Operations of addition and multiplication have the property of commutativity, transitivity, and the operation of multiplication is distributive over addition.

For every  $a \in GF(q)$ , there exists  $-a \in GF(q)$  such that a + (-a) = 0 [52]. Similarly, for every nonzero  $b \in GF(q)$ , there exists  $b^{-1} \in GF(q)$  such that  $b \cdot b^{-1} = 1$ .

Figure 2.10: Addition and multiplication over some finite fields

Another important property of the Galois fields is that for every  $\alpha \in GF(q)$ ,  $\alpha^q = \alpha$  and for  $\alpha \neq 0$ ,  $\alpha^{q-1} = 1$  [52]. Hence the number of possible powers of  $\alpha$  in GF(q) is limited to q.

The elements of prime Galois fields are denoted as integer numbers. In the case of  $GF(p^t)$ , first p elements are denoted as integers, as they are the elements of the prime subfield GF(p), and the rest of the elements assign consequent uppercase latin letters: A, B, . . . . For example the elements of GF(4) are: 0, 1, A, B.

Arithmetic operations for some Galois fields used in the further examples are shown in Figure 2.10.

## Matrix operations over Galois fields

The presented research extensively uses matrix operations over Galois fields. Due to the properties of Galois fields, the matrix operations are defined in the same way as in regular algebra. The elements of matrices are the elements of some field GF(q).

Matrix addition is defined as

$$[X + Y]_{i,j} = X_{i,j} + Y_{i,j},$$

where X, Y are m-by-n matrices,  $1 \le i \le m$ ,  $1 \le j \le n$ .

If X is an m-by-n matrix and Y is n-by-p matrix, then their *matrix product* XY is the m-by-p matrix whose entries are given by dot-product of the corresponding row of X and the corresponding column of Y:

$$[XY]_{i,j} = \sum_{r=1}^{n} X_{i,r} Y_{r,j},$$

where  $1 \le i \le m$  and  $1 \le j \le p$ . Matrix multiplication satisfies the rules (XY) Z = X(YZ) (associativity), and (X + Y) Z = XZ + YZ as well as Z(X + Y) = ZX + ZY (left and right distributivity), whenever the size of the matrices X, Y, Z is such that the various products are defined.

In linear algebra an n-by-n (square) matrix X is called *invertible*, if there exists an n-by-n matrix Y such that

$$XY = YX = I_n$$

where  $I_n$  denotes the n-by-n identity matrix and the multiplication used is ordinary matrix multiplication. If this is the case, then the matrix Y is uniquely determined by X and is called the *inverse* of X, denoted by  $X^{-1}$ . Non-square matrices (m-by-n matrices for which  $m \neq n$ ) do not have an inverse.

**Definition 2.10.** If X is an m-by-n matrix and Y is a p-by-q matrix, then the *Kronecker product* [23] is the mp-by-nq block matrix

$$X \otimes Y = \begin{bmatrix} x_{1,1}Y & \cdots & x_{1,n}Y \\ \vdots & \ddots & \vdots \\ x_{m,1}Y & \cdots & x_{m,n}Y \end{bmatrix}$$

Kronecker product is not commutative, but it is associative:  $(X \otimes Y) \otimes Z = X \otimes (Y \otimes Z)$  for matrices X, Y, Z. One of the properties of Kronecker product used in the presented theory is that for any invertible matrices X and Y,  $(X \otimes Y)^{-1} = X^{-1} \otimes Y^{-1}$ ;  $(X \otimes Y)$  is invertible only if X and Y are invertible.

# 2.2.2 Multi-valued Reed-Muller expansions

Binary and multi-valued functions can be represented using XOR sum of products. One particular case is Reed-Muller (RM) expansions. In the multi-valued case, Reed-Muller expansions have the form of sum of products computed over GF(q).

The following simplified definition of literal is used in this thesis; it is sufficient for understanding the theory at the required level. For classic definition of literal and literal form of Reed-Muller expansions, refer to [35, 34].

**Definition 2.11.** *Literal*  $\tilde{x}$  of the q-valued variable x is one of q possible polarity forms (x + c); c is an element of GF(q) denoting the literal.

**Definition 2.12.** For an n-variable q-valued function *polarity number* k is defined as an integer representation of a q-nary tuple  $\langle k_n \dots k_1 \rangle_q = k$  where  $k_i \in GF(q)$  denotes the polarity of literal  $\widetilde{x}_i$ ,  $i=1\dots n$ . For example, the polarity number  $k=2=\langle 0A \rangle_q$  for 2-variable quaternary function means that  $\widetilde{x}_2=x_2$  and  $\widetilde{x}_1=x_1+A$ .

**Definition 2.13.** A *general canonical Reed-Muller (RM) expansion* for an n-variable q-valued function in polarity k is defined as follows:

$$f(\widetilde{x}_1, \dots, \widetilde{x}_n) = \sum_{i=0}^{q^n - 1} a_i \left[ \prod_{j=1}^n \widetilde{x}_j^{i_j} \right] \quad \text{over } GF(q)$$

(2.1)

where  $\mathfrak{i}_j$  is a single digit of a q-nary tuple  $\langle \mathfrak{i}_n \dots \mathfrak{i}_1 \rangle_q = \mathfrak{i}$ . Vector  $\mathfrak{a} = \begin{bmatrix} \mathfrak{a}_0 & \dots & \mathfrak{a}_{q^n-1} \end{bmatrix}^t$  is a *coefficient vector*. In a *fixed polarity* RM expansion each variable must be represented by the same literal throughout the expansion.

Following from Definition 2.10 of the Kronecker product, (2.1) can be rewritten in matrix form. Let  $\widetilde{X}_j = \begin{bmatrix} 1 & \widetilde{x}_j & \dots & \widetilde{x}_j^{q-1} \end{bmatrix}$  is the vector of all possible powers of the literal  $\widetilde{x}_j$ , then

$$f(\widetilde{x}_1, \dots, \widetilde{x}_n) = \left(\widetilde{X}_n \otimes \dots \otimes \widetilde{X}_1\right) \cdot \alpha \quad \text{over GF}(q) \tag{2.2}$$

where a is a coefficient vector as in Definition 2.13. Equation (2.2), as well as (2.1), represents the sum of all possible products of all possible powers of the input variables

multiplied by coefficients from a.

Reed-Muller expansion of zero polarity for a quaternary function of one variable takes the form:

$$f(x) = a_0 + a_1 x + a_2 x^2 + a_3 x^3$$

over GF(4) (2.3)

As an example, a 2-variable quaternary function of the polarity  $k=2=\langle 0A\rangle_4$  gives the following RM form:

$$\begin{array}{ll} f\left(x_{1},x_{2}\right) & = & a_{0}+a_{1}\ddot{x}_{1}+a_{2}\ddot{x}_{1}^{2}+a_{3}\ddot{x}_{1}^{3}+\\ & a_{4}x_{2}+a_{5}\ddot{x}_{1}x_{2}+a_{6}\ddot{x}_{1}^{2}x_{2}+a_{7}\ddot{x}_{1}^{3}x_{2}+\\ & a_{8}x_{2}^{2}+a_{9}\ddot{x}_{1}x_{2}^{2}+a_{10}\ddot{x}_{1}^{2}x_{2}^{2}+a_{11}\ddot{x}_{1}^{3}x_{2}^{2}+\\ & a_{12}x_{2}^{3}+a_{13}\ddot{x}_{1}x_{2}^{3}+a_{14}\ddot{x}_{1}^{2}x_{2}^{3}+a_{15}\ddot{x}_{1}^{3}x_{2}^{3} \end{array}$$

computed over GF(4);  $\ddot{x}_1 = x_1 + A$ .

### 2.2.3 Green's direct method

The computation of an RM expansion corresponds directly to the computation of the coefficient vector a. The following method of computation has been proposed in [28] for quaternary RM expansions and is known as *Green's direct method*.

Let  $d = \begin{bmatrix} d_0 & \dots & d_3 \end{bmatrix}^t$ ,  $d_0 \dots d_3 \in GF(4)$  be the truth vector of the zero polarity quaternary function f(x) shown in (2.3). Then,

$$\begin{array}{llll} d_0 & = & f(0) & = & a_0 \\ \\ d_1 & = & f(1) & = & a_0 + a_1 + a_2 + a_3 \\ \\ d_2 & = & f(A) & = & a_0 + Aa_1 + Ba_2 + a_3 \\ \\ d_3 & = & f(B) & = & a_0 + Ba_1 + Aa_2 + a_3 \end{array} \tag{2.4}$$

This set of linear equations can be solved in matrix form:

$$d = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 1 & 1 & 1 & 1 \\ 1 & A & B & 1 \\ 1 & B & A & 1 \end{bmatrix} \cdot a = S_0 a \quad \text{over GF}(4)$$

(2.5)

$$a = S_0^{-1}d = W_0d \quad \text{over GF}(4)$$

$$W_0 = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & B & A \\ 0 & 1 & A & B \\ 1 & 1 & 1 & 1 \end{bmatrix}$$

(2.6)

Hence a coefficient vector  $\mathfrak{a}$  can be derived from the truth vector of a function. For non-zero polarity forms (k = 1...3) of a 1-variable quaternary function the same approach can be applied, and corresponding matrices  $W_1$ ,  $W_2$ ,  $W_3$  can be found:

$$S_{1} = \begin{bmatrix} 1 & 1 & 1 & 1 \\ 1 & 0 & 0 & 0 \\ 1 & B & A & 1 \\ 1 & A & B & 1 \end{bmatrix}, \quad W_{1} = S_{1}^{-1} = \begin{bmatrix} 0 & 1 & 0 & 0 \\ 1 & 0 & A & B \\ 1 & 0 & B & A \\ 1 & 1 & 1 & 1 \end{bmatrix};$$

$$S_{2} = \begin{bmatrix} 1 & A & B & 1 \\ 1 & B & A & 1 \\ 1 & 0 & 0 & 0 \\ 1 & 1 & 1 & 1 \end{bmatrix}, \quad W_{2} = S_{2}^{-1} = \begin{bmatrix} 0 & 0 & 1 & 0 \\ B & A & 0 & 1 \\ A & B & 0 & 1 \\ 1 & 1 & 1 & 1 \end{bmatrix};$$

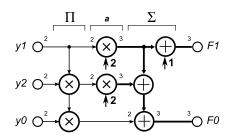

$$S_{3} = \begin{bmatrix} 1 & B & A & 1 \\ 1 & A & B & 1 \\ 1 & 1 & 1 & 1 \\ 1 & 0 & 0 & 0 \end{bmatrix}, \quad W_{3} = S_{3}^{-1} = \begin{bmatrix} 0 & 0 & 0 & 1 \\ A & B & 1 & 0 \\ B & A & 1 & 0 \\ 1 & 1 & 1 & 1 \end{bmatrix}.$$