School of Electrical, Electronic & Computer Engineering

# Multi-resource Approach to Asynchronous SoC: Design and Tool Support

Stanislavs Golubcovs

**Technical Report Series**

NCL-EECE-MSD-TR-2011-176

December 2011

Stanislavs.Golubcovs@ncl.ac.uk

Supported by EPSRC grant EP/E044662/1

NCL-EECE-MSD-TR-2011-176

Copyright © 2011 University of Newcastle upon Tyne

School of Electrical, Electronic & Computer Engineering,

Merz Court,

University of Newcastle upon Tyne,

Newcastle upon Tyne, NE1 7RU, UK

http://async.org.uk/

# University of Newcastle upon Tyne School of Electrical, Electronic and Computer Engineering

# Multi-resource Approach to Asynchronous SoC: Design and Tool Support

by

Stanislavs Golubcovs

PhD Thesis

December 2011

# **Abstract**

As silicon cost reduces, the demands for higher performance and lower power consumption are ever increasing. The ability to dynamically control the number of resources employed can help balance and optimise a system in terms of its throughput, power consumption, and resilience to errors. The management of multiple resources requires building more advanced resource allocation logic than traditional 1-of-*N* arbiters posing the need for the efficient design flow supporting both the design and verification of such systems.

Networks-on-Chip provide a good application example of distributed arbitration, in which the processor cores needing to transmit data are the clients; and the point-to-point links are the resources managed by routers. Building fast and smart arbiters can greatly benefit such systems in providing efficient and reliable communication service.

In this thesis, a multi-resource arbiter was developed based on the Signal Transition Graph (STG) development flow. The arbiter distributes multiple active interchangeable resources that initiate requests when they are ready to be used. It supports concurrent resource utilization, which benefits creating asynchronous Multiple-Input-Multiple-Output (MIMO) queues.

In order to deal with designs of higher complexity, an arbiter-oriented design flow is proposed. The flow is based on digital circuit components that are represented internally as STGs. This allows designing circuits without directly working with STGs but allowing their use for synthesis and formal verification. The interfaces for modelling, simulation, and visual model representation of the flow were implemented based on the existing modelling framework. As a result, the verification phase of the flow has helped to find hazards in existing Priority arbiter implementations.

Finally, based on the logic-gate flow, the structure of a low-latency general purpose arbiter was developed. This design supports a wide variety of arbitration problems including the multi-resource management, which can benefit building NoCs employing complex and adaptive routing techniques.

# **Contents**

| List of Figures |         |                                 |    |  |

|-----------------|---------|---------------------------------|----|--|

| Li              | st of ' | f Tables                        | 12 |  |

| A               | cknov   | owledgements                    | 13 |  |

| 1               | Intr    | troduction                      | 1  |  |

|                 | 1.1     | Motivation                      | 1  |  |

|                 | 1.2     | Main Contributions              | 4  |  |

|                 | 1.3     | Organisation of Thesis          | 5  |  |

|                 | 1.4     | Bibliography                    |    |  |

| 2               | Bacl    | ckground                        | 8  |  |

|                 | 2.1     | Asynchronous Circuits           | 8  |  |

|                 | 2.2     | Digital Circuits                | 10 |  |

|                 | 2.3     | Petri Nets                      | 12 |  |

|                 |         | 2.3.1 Pre-set and Post-set      | 13 |  |

|                 |         | 2.3.2 Enabling and Firing       | 13 |  |

|                 |         | 2.3.3 Other PN Properties       | 14 |  |

|                 |         | 2.3.4 Signal Transition Graphs  | 14 |  |

|                 | 2.4     | Asynchronous Circuit Primitives | 16 |  |

|                 |         | 2.4.1 C-element                 | 16 |  |

|                 |         | 2.4.2 Toggle Component          | 17 |  |

|                 |         | 2.4.3 Decision Wait Element     | 17 |  |

|   | 2.5 | Async  | chronous Signalling                  | 18 |

|---|-----|--------|--------------------------------------|----|

|   |     | 2.5.1  | Handshake Protocols                  | 18 |

|   |     | 2.5.2  | Channel Types                        | 19 |

|   |     | 2.5.3  | Delay-insensitive Encoding           | 20 |

|   |     | 2.5.4  | Dual-rail                            | 20 |

|   |     | 2.5.5  | Bundled data Encoding                | 22 |

|   | 2.6 | Exam   | ple of Logic Synthesis Using Petrify | 22 |

| 3 | Rev | iew on | Asynchronous Arbiters                | 27 |

|   | 3.1 |        | luction                              | 27 |

|   | 3.2 |        | er-specific Properties               | 28 |

|   | 3.3 |        | tability                             | 31 |

|   | 3.4 |        | gue arbiters                         | 32 |

|   |     | 3.4.1  | The MUTEX Element                    | 32 |

|   |     | 3.4.2  | Analogue 1-of-3 arbiter              | 33 |

|   |     | 3.4.3  | Analogue 2-of-3 Arbiter              | 34 |

|   | 3.5 | Two-v  | vay Arbiters                         | 35 |

|   |     | 3.5.1  | 4-phase Arbitration (RG)             | 35 |

|   |     | 3.5.2  | 2-phase Arbitration (RGD)            | 36 |

|   |     | 3.5.3  | "Nacking" Arbiter                    | 37 |

|   | 3.6 | 1-of-N | Multi-way Arbiters                   | 38 |

|   |     | 3.6.1  | Mesh-based Implementation            | 38 |

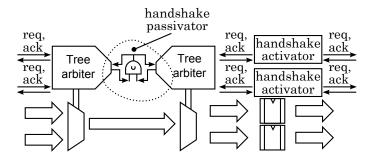

|   |     | 3.6.2  | Cascaded Tree Arbiters               | 40 |

|   |     | 3.6.3  | Token Ring                           | 42 |

|   |     | 3.6.4  | Ordered Arbiters                     | 44 |

|   |     | 3.6.5  | Priority Arbiters                    | 45 |

|   | 3.7 | Multi- | resource Arbiters                    | 47 |

|   |     | 3.7.1  | Multi-token Arbiters                 | 48 |

|   |     | 3.7.2  | Patil's Arbiter                      | 49 |

|   |     | 3.7.3  | Committee arbiter                    | 50 |

|   | 3.8 | Concl        | usions                                                       | 51 |

|---|-----|--------------|--------------------------------------------------------------|----|

| 4 | Con | curren       | t Multi-Resource Arbiter: Design and Applications            | 53 |

|   | 4.1 | Introd       | luction                                                      | 53 |

|   | 4.2 | Desig        | n Method                                                     | 55 |

|   | 4.3 | $2 \times 2$ | Arbiter Design                                               | 56 |

|   |     | 4.3.1        | Functionality                                                | 56 |

|   |     | 4.3.2        | Resolving the Conflict                                       | 59 |

|   |     | 4.3.3        | Implementation                                               | 63 |

|   |     | 4.3.4        | Verification of the Circuit                                  | 66 |

|   |     | 4.3.5        | Latency Estimation                                           | 66 |

|   |     | 4.3.6        | Simulation in Spectre                                        | 68 |

|   |     | 4.3.7        | Cost of the Parallelism                                      | 69 |

|   | 4.4 | Exten        | ding up to $N \times M$ Arbiters                             | 69 |

|   |     | 4.4.1        | Column/row Blocking                                          | 71 |

|   |     | 4.4.2        | Ring-based Blocking                                          | 73 |

|   |     | 4.4.3        | Latency Estimation                                           | 75 |

|   |     | 4.4.4        | Simulation in Spectre                                        | 75 |

|   |     | 4.4.5        | Fairness of the Arbiter                                      | 76 |

|   | 4.5 | Multi-       | resource Arbiter for Passive Resources                       | 76 |

|   |     | 4.5.1        | Task Specification                                           | 76 |

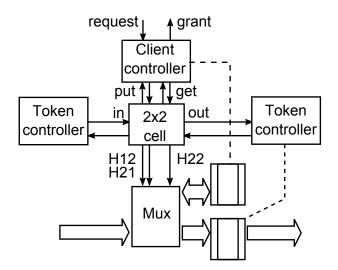

|   |     | 4.5.2        | Implementation of the Ring Cell                              | 78 |

|   |     | 4.5.3        | Implementation of the Client Controller and Token Controller | 80 |

|   |     | 4.5.4        | Latency Estimation                                           | 80 |

|   |     | 4.5.5        | Comparison with Patil's Arbiter                              | 81 |

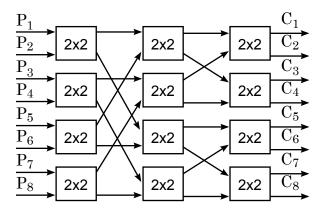

|   | 4.6 | Desig        | ning MIMO Queues                                             | 81 |

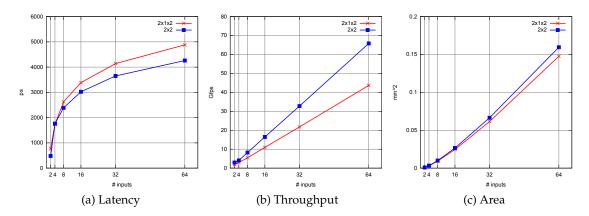

|   |     | 4.6.1        | MIMO Performance Comparison                                  | 83 |

|   | 47  | Concl        | usions                                                       | 83 |

| Gate | e-level                                                            | Design Flow                                                                                                                                                                              | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.1  | Introd                                                             | uction                                                                                                                                                                                   | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5.2  | Featur                                                             | res of the Gate-level Design Flow                                                                                                                                                        | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | 5.2.1                                                              | Basic Plugin Components                                                                                                                                                                  | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | 5.2.2                                                              | Gates of High Complexity                                                                                                                                                                 | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | 5.2.3                                                              | Delay-Insensitive Circuits                                                                                                                                                               | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | 5.2.4                                                              | Circuits with Timing Assumptions                                                                                                                                                         | 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | 5.2.5                                                              | High-level Models                                                                                                                                                                        | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | 5.2.6                                                              | State Space Exploration                                                                                                                                                                  | 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | 5.2.7                                                              | Circuits with MUTEX Elements                                                                                                                                                             | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5.3  | Analy                                                              | sis of Priority Arbiter                                                                                                                                                                  | 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5.4  | Concl                                                              | usions                                                                                                                                                                                   | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Des  | ign of (                                                           | Generalized Arbiter                                                                                                                                                                      | 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6.1  | Introd                                                             | uction                                                                                                                                                                                   | 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6.2  | Arbite                                                             | er Design                                                                                                                                                                                | 103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      | 6.2.1                                                              | Design Method                                                                                                                                                                            | 103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      | 6.2.2                                                              | Basic Structure                                                                                                                                                                          | 104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      | 6.2.3                                                              | Decomposition                                                                                                                                                                            | 108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      | 6.2.4                                                              | High Performance                                                                                                                                                                         | 109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      | 6.2.5                                                              | Avoiding Deadlocks                                                                                                                                                                       | 109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      | 6.2.6                                                              | Circuit Verification                                                                                                                                                                     | 110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6.3  | Possib                                                             | ole Extensions                                                                                                                                                                           | 113                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6.4  | Perfor                                                             | mance Estimations                                                                                                                                                                        | 114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      | 6.4.1                                                              | Priority 2-of-3 Arbitration                                                                                                                                                              | 114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      | 6.4.2                                                              | Pipelined Arbiter Scaling                                                                                                                                                                | 115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6.5  | Concl                                                              |                                                                                                                                                                                          | 116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Con  | chision                                                            | ns                                                                                                                                                                                       | 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      |                                                                    |                                                                                                                                                                                          | 119                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      | 5.1<br>5.2<br>5.3<br>5.4<br><b>Des</b><br>6.1<br>6.2<br>6.3<br>6.4 | 5.1 Introd 5.2 Featur 5.2.1 5.2.2 5.2.3 5.2.4 5.2.5 5.2.6 5.2.7 5.3 Analy 5.4 Conclusion 6.2 Arbite 6.2.1 6.2.2 6.2.3 6.2.4 6.2.5 6.2.6 6.3 Possib 6.4 Perfor 6.4.1 6.4.2 6.5 Conclusion | 5.2 Features of the Gate-level Design Flow 5.2.1 Basic Plugin Components 5.2.2 Gates of High Complexity 5.2.3 Delay-Insensitive Circuits 5.2.4 Circuits with Timing Assumptions 5.2.5 High-level Models 5.2.6 State Space Exploration 5.2.7 Circuits with MUTEX Elements 5.3 Analysis of Priority Arbiter 5.4 Conclusions  Design of Generalized Arbiter 6.1 Introduction 6.2 Arbiter Design 6.2.1 Design Method 6.2.2 Basic Structure 6.2.3 Decomposition 6.2.4 High Performance 6.2.5 Avoiding Deadlocks 6.2.6 Circuit Verification 6.3 Possible Extensions 6.4 Performance Estimations 6.4.1 Priority 2-of-3 Arbitration 6.4.2 Pipelined Arbiter Scaling |

|    | 7.2   | Future Work                            | 119 |

|----|-------|----------------------------------------|-----|

| A  | Sum   | nmary on Asynchronous Arbiters         | 120 |

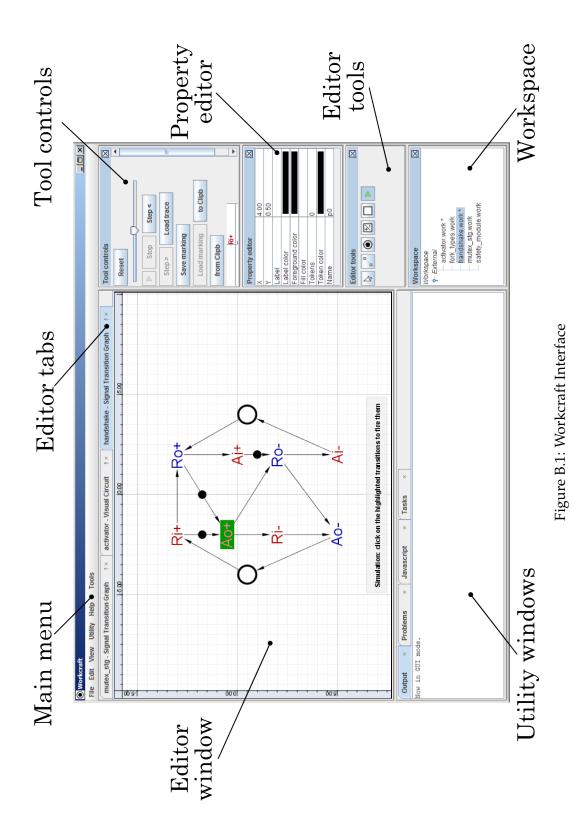

| В  | Wor   | kcraft Interface                       | 123 |

|    | B.1   | Main Window                            | 123 |

|    |       | B.1.1 Basic Mouse Controls             | 124 |

|    | B.2   | Common Operation Modes                 | 124 |

|    | B.3   | STG Plugin Operation Modes             | 124 |

|    | B.4   | Digital Circuit Plugin Operation Modes | 126 |

|    | B.5   | Conversion to the Circuit STG          | 126 |

|    | B.6   | Simulation                             | 126 |

|    | B.7   | Verification                           | 127 |

| Re | ferer | ices                                   | 129 |

# **List of Figures**

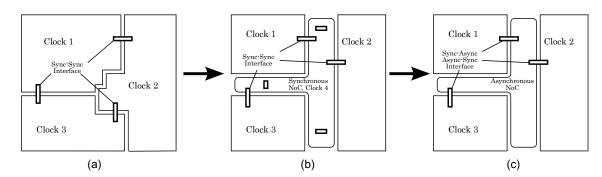

| 1.1  | GALS evolution                                 | 3  |

|------|------------------------------------------------|----|

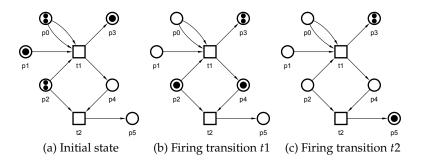

| 2.1  | Petri net firing transition                    | 14 |

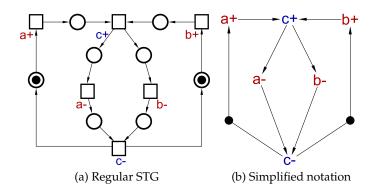

| 2.2  | STG example of a C-element                     | 15 |

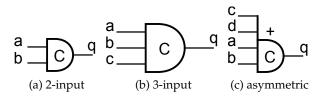

| 2.3  | C-element examples                             | 17 |

| 2.4  | Toggle component                               | 17 |

| 2.5  | Decision-wait element                          | 18 |

| 2.6  | Basic handshake protocols                      | 18 |

| 2.7  | Channel types                                  | 20 |

| 2.8  | Dual-rail encoding                             | 21 |

| 2.9  | Bundled data, 4-phase push channel             | 22 |

| 2.10 | Channel converter structure                    | 23 |

| 2.11 | Control logic STG                              | 24 |

| 3.1  | Naive arbiter implementation and metastability | 32 |

| 3.2  | MUTEX element [47]                             | 33 |

| 3.3  | MUTEX with standard gates [35]                 | 33 |

| 3.4  | Tri-flop arbiter                               | 34 |

| 3.5  | 2-of-3 analogue arbiter                        | 35 |

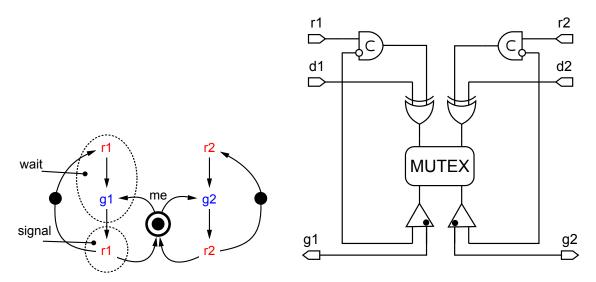

| 3.6  | 4-phase two-way arbiter                        | 36 |

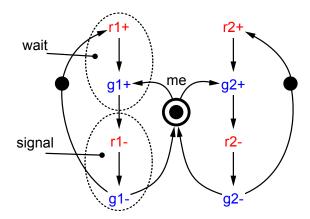

| 3.7  | 2-phase two-way arbiter                        | 37 |

| 3.8  | Nacking arbiter                                | 37 |

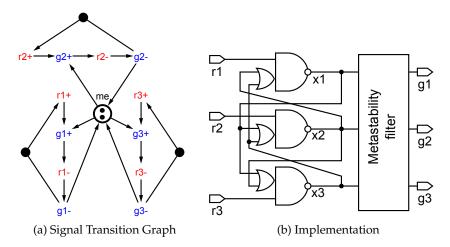

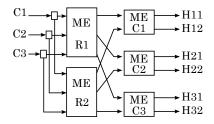

| 3.9  | Multi-input arbiter                            | 39 |

| 3.10 | 1-of-3 mesh                                                                     | 39 |

|------|---------------------------------------------------------------------------------|----|

| 3.11 | Generic mesh structure                                                          | 40 |

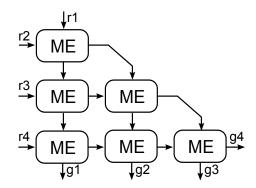

| 3.12 | Tree structure                                                                  | 40 |

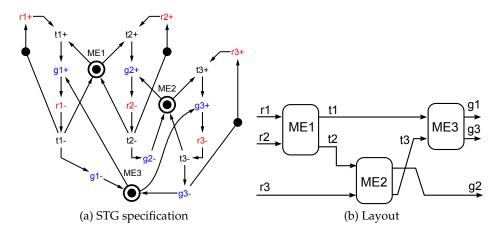

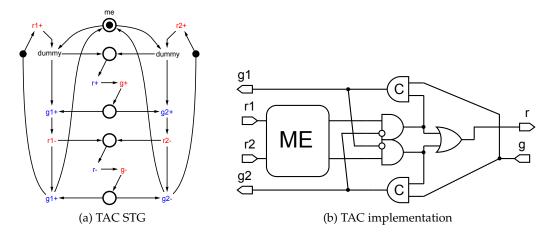

| 3.13 | Cascaded arbiter STG and implementation                                         | 41 |

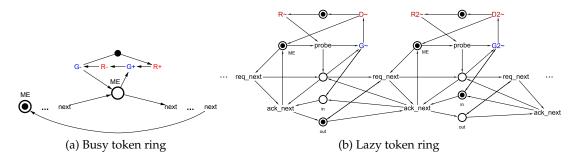

| 3.14 | Token ring high-level models                                                    | 42 |

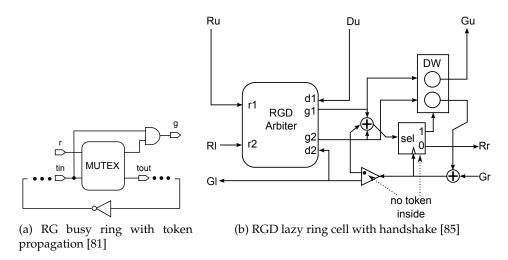

| 3.15 | Ring implementations                                                            | 43 |

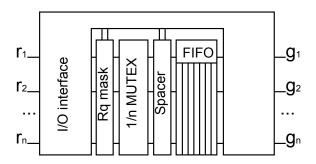

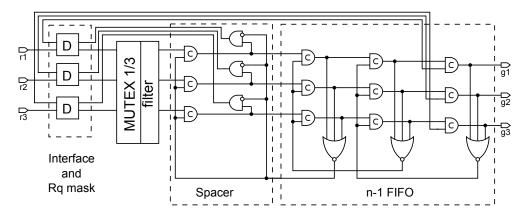

| 3.16 | Ordered FIFO arbiter structure                                                  | 44 |

| 3.17 | Ordered 3-way arbiter implementation                                            | 44 |

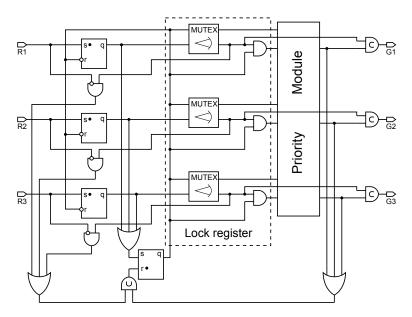

| 3.18 | Three-way static priority arbiter                                               | 46 |

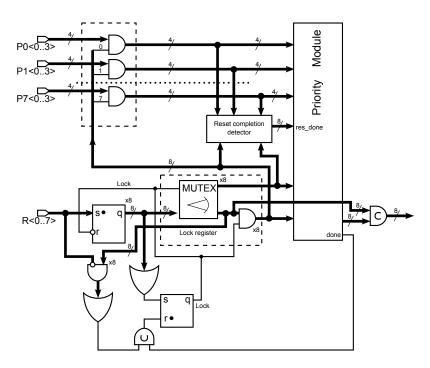

| 3.19 | Eight-ways dynamic priority arbiter                                             | 47 |

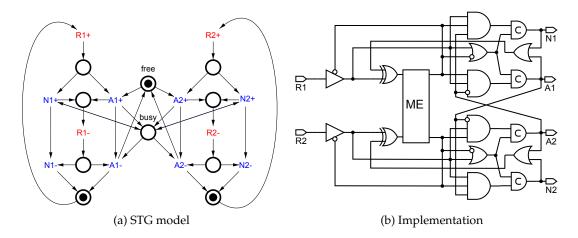

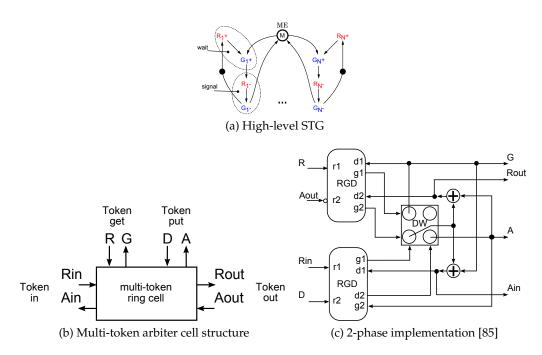

| 3.20 | Multi-token arbiters                                                            | 49 |

| 3.21 | Multi-resource "Forward acting" arbiter                                         | 50 |

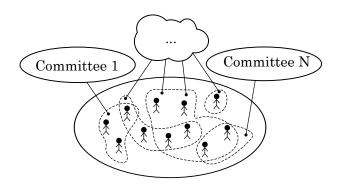

| 3.22 | Committee problem                                                               | 51 |

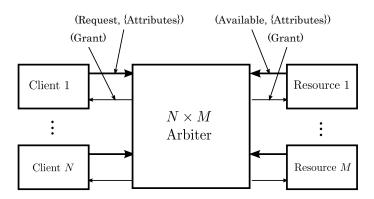

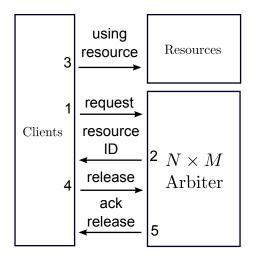

| 4.1  | Synopsis of an arbiter [35]                                                     | 54 |

| 4.2  | Arbiter design flow                                                             | 56 |

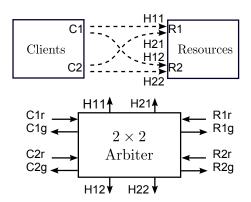

| 4.3  | $2 \times 2$ arbiter interface                                                  | 57 |

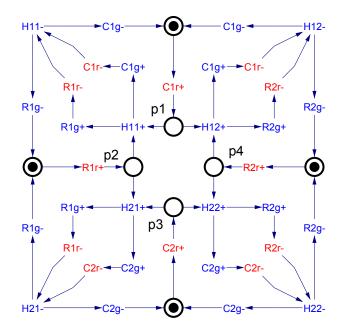

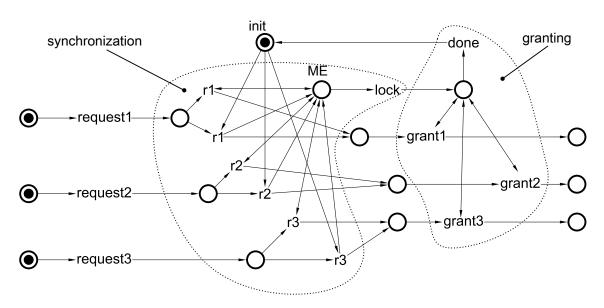

| 4.4  | $2 \times 2$ arbiter STG                                                        | 58 |

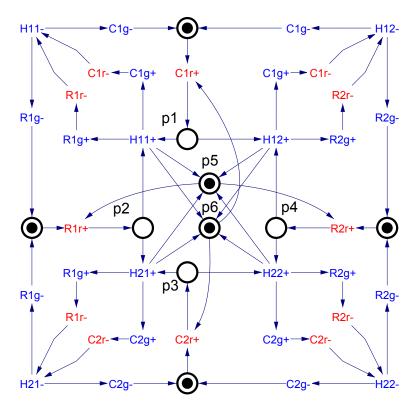

| 4.5  | Additional exclusion places added                                               | 60 |

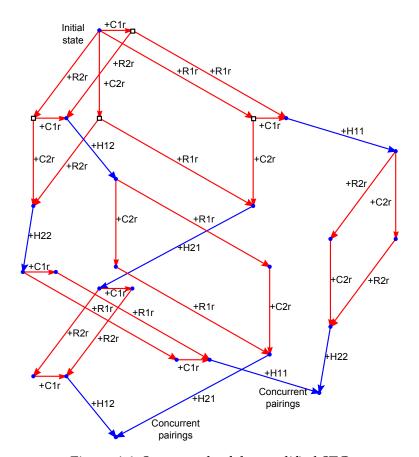

| 4.6  | State graph of the modified STG                                                 | 61 |

| 4.7  | STG with MUTEX elements                                                         | 62 |

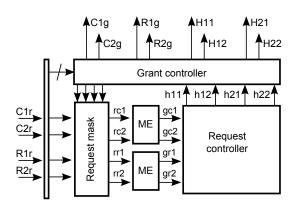

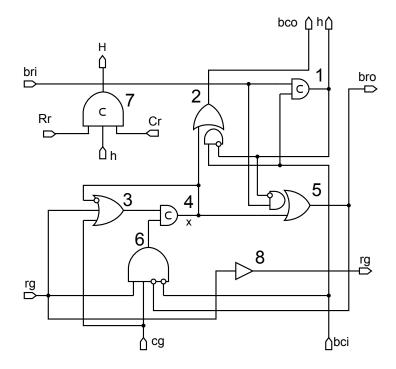

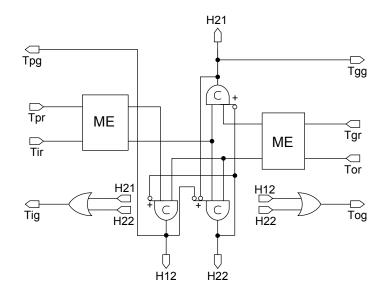

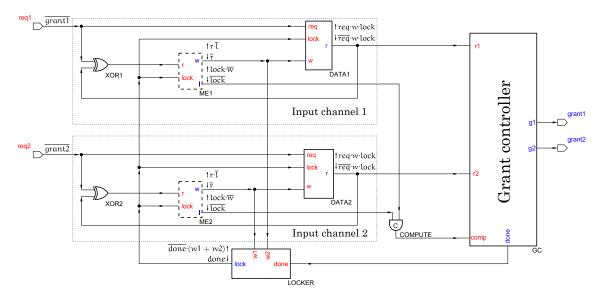

| 4.8  | Arbiter structure                                                               | 64 |

| 4.9  | $2 \times 2$ arbiter implementation                                             | 64 |

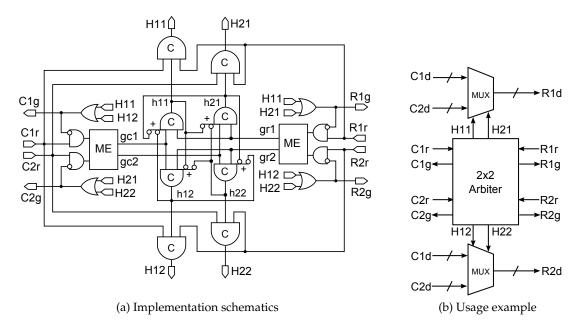

| 4.10 | Timing diagram                                                                  | 67 |

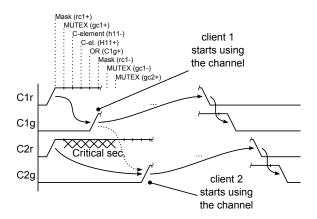

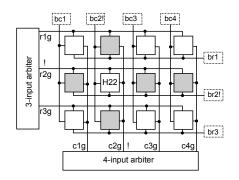

| 4.11 | $4 \times 3$ arbiter implementation (shows active requests on $r2g$ and $c2g$ ) | 70 |

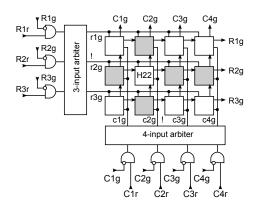

| 4.12 | Arbiter with blocking tiles                                                     | 71 |

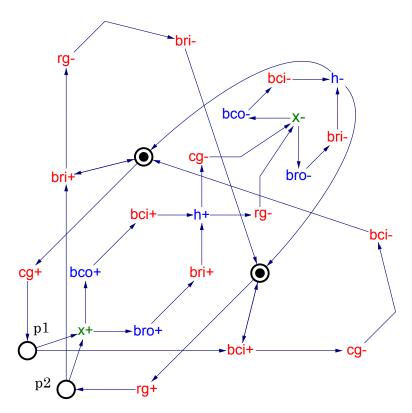

| 4.13 | Column/row block tile STG                                                       | 72 |

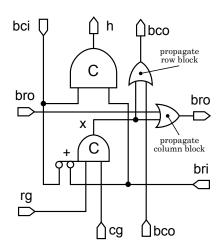

| 4.14 | Tile implementation for the C/R blocks                                          | 73 |

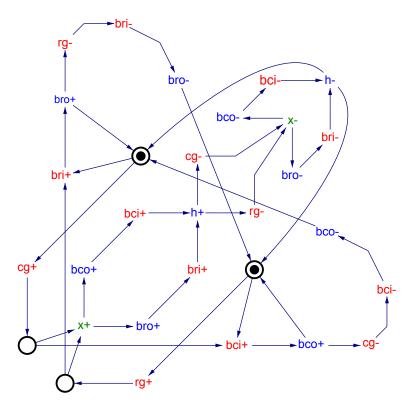

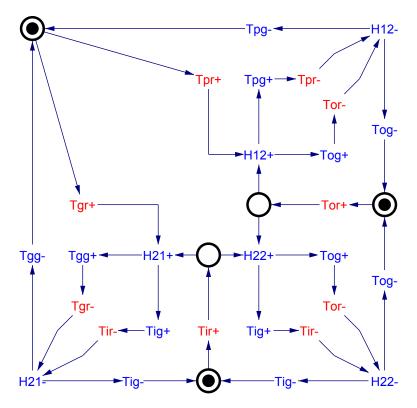

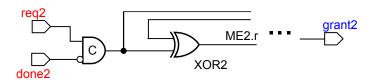

| 4.15 | Ring-based tile STG                                                             | 74 |

| 4 16 | Tile implementing ring-based approach                                           | 7/ |

| 4.17 | Asymmetric multi-resource arbiter structure              | 77  |

|------|----------------------------------------------------------|-----|

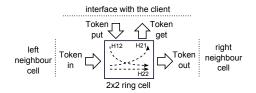

| 4.18 | Busy token ring cell                                     | 78  |

| 4.19 | The STG of a ring cell                                   | 79  |

| 4.20 | Implementation of the ring cell                          | 79  |

| 4.21 | Ring cell structure                                      | 80  |

| 4.22 | Structure of the sequential 2 $\times$ 2 MIMO queue [80] | 82  |

| 4.23 | $8\times 8$ MIMO queue                                   | 82  |

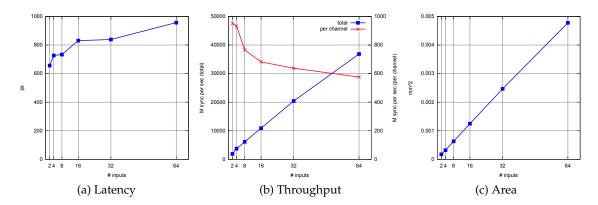

| 4.24 | MIMO performance                                         | 83  |

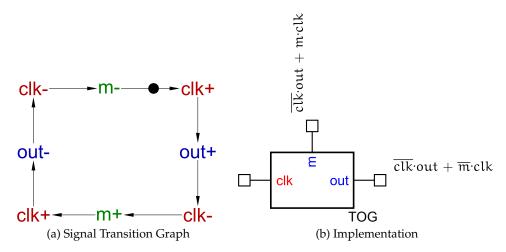

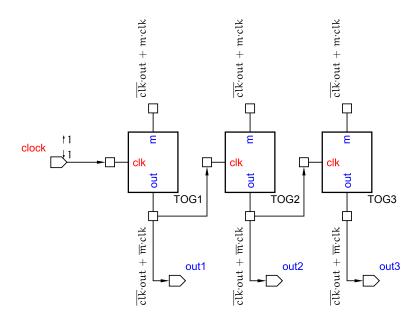

| 5.1  | Toggle component                                         | 88  |

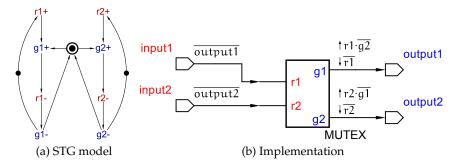

| 5.2  | MUTEX element                                            | 89  |

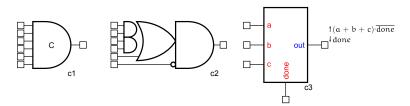

| 5.3  | High complexity gates                                    | 90  |

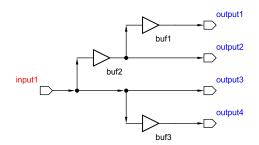

| 5.4  | Modelling asymmetric forks                               | 91  |

| 5.5  | Counter with timing assumptions                          | 92  |

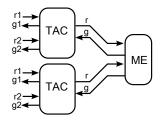

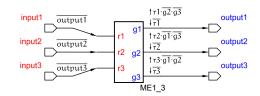

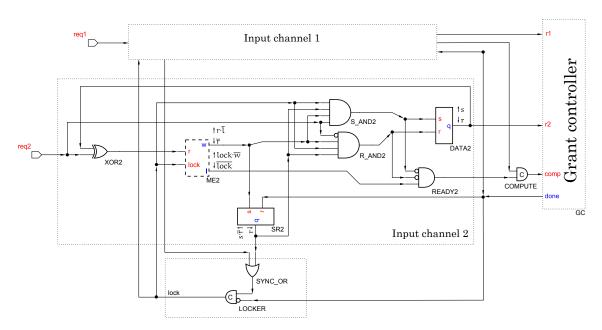

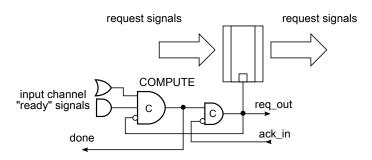

| 5.6  | 3-input arbiter (high level model)                       | 93  |

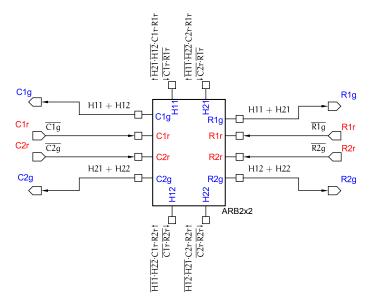

| 5.7  | High-level view on 2 $\times$ 2 arbiter                  | 93  |

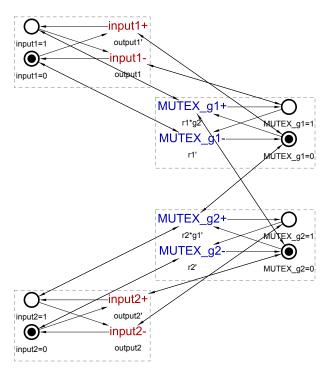

| 5.8  | Generated MUTEX STG                                      | 95  |

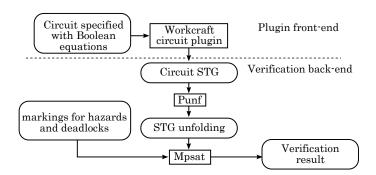

| 5.9  | Mpsat verification flow                                  | 96  |

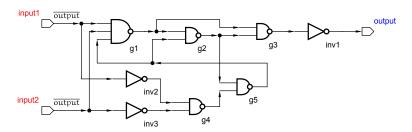

| 5.10 | C-element formed of NAND gates                           | 96  |

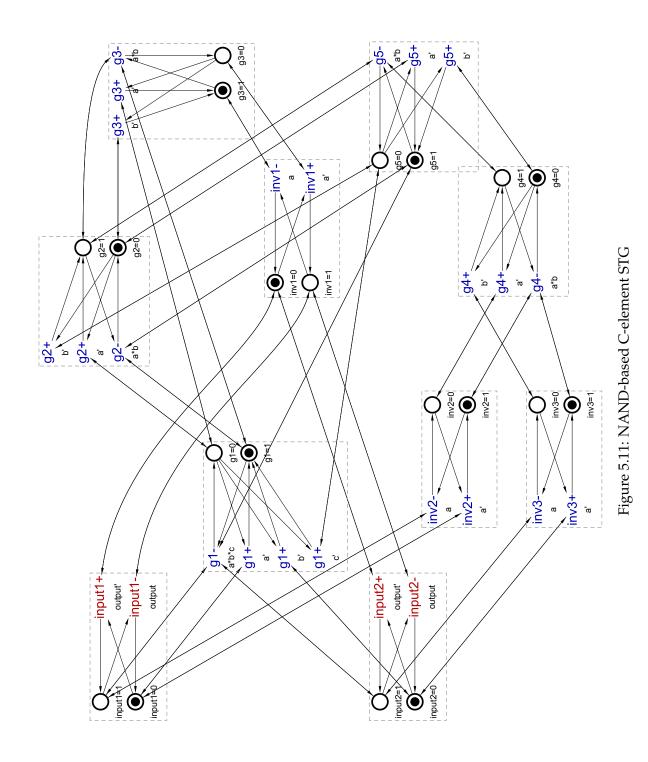

| 5.11 | NAND-based C-element STG                                 | 97  |

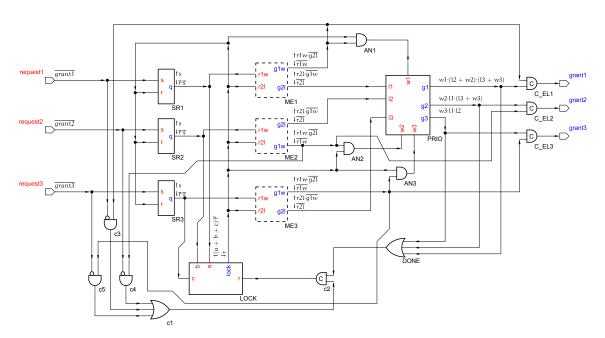

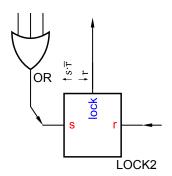

| 5.12 | Modelled priority arbiter                                | 99  |

| 5.13 | LOCK decomposition                                       | 100 |

| 6.1  | Arbitration example in 2D routing grid                   | 103 |

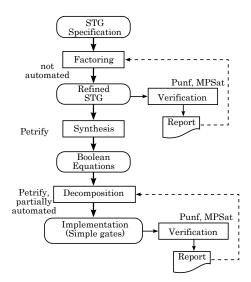

| 6.2  | Arbiter design flow                                      | 104 |

| 6.3  | Generalized arbiter high-level PN                        | 105 |

| 6.4  | High-level circuit structure                             | 105 |

| 6.5  | Decomposition into simple gates                          | 108 |

| 6.6  | SYNC_OR decomposition                                    | 111 |

| 6.7  | Pipelining                                               | 113 |

| 6.8  | Employing RGD interface                      | 114 |

|------|----------------------------------------------|-----|

| 6.9  | Decoupling synchronizer and grant controller | 115 |

| 6.10 | Pipelined arbiter performance                | 116 |

| B.1  | Workcraft Interface                          | 125 |

| B.2  | Opening generated STG                        | 127 |

# **List of Tables**

| 2.1 | Dual rail 4-phase codes                        | 21  |

|-----|------------------------------------------------|-----|

| 4.1 | $2 \times 2$ performance estimation in Spectre | 68  |

| 4.2 | $4 \times 3$ performance estimation in Spectre | 76  |

| 6.1 | Priority 2-of-3 arbitration                    | 114 |

| A.1 | Analogue arbiters                              | 120 |

| A.2 | Two-way arbiters                               | 121 |

| A.3 | 1-of- <i>N</i> arbiters                        | 121 |

| Α 4 | Other arhiters                                 | 122 |

# Acknowledgements

I am grateful to my supervisor, Prof. Alex Yakovlev, for his incredibly wise guidance and motivating talks. I am also grateful to Dr. Alex Bystrov and Dr. Fei Xia for their fruitful discussions on various related topics.

I would like to thank my friends and colleagues Dr. Danil Sokolov, Dr. Andrey Mokhov, Dr. Robin Emery and Mr. Ashur Rafiev for contributing their ideas and making my student life full of fun and excitement. Special thanks to Mr. Arseny Alekseyev and Dr. Ivan Poliakov for their great technical help with the Workcraft source code. In addition, I wish to thank Dr. Victor Khomenko for his advice and work on the tools Punf and Mpsat which where of great help with many complex design decisions.

A very special thanks to my parents Alexander and Antonina for their constant encouragement and moral support.

This work was supported by EPSRC grant GR/E044662/1 (STEP).

# Chapter 1

# Introduction

# 1.1 Motivation

The increasing scale of modern designs is accompanied by the increased risk of failure; as a result large multi-functional designs are more difficult to test and implement. To address the problem, the larger systems are composed of smaller well tested design blocks dedicated to particular tasks and combined into a single System-on-a-Chip (SoC) [66]. The result is a system with processors, memory components, encoders, floating point units, and other blocks (also called the *intellectual property* (IP) cores), whose complexity is constrained allowing combining solutions from independent vendors.

The greater requirements for high-performance systems have led designers to replace large complex cores with multi-core systems composed of simpler cores [49]. The repeated use of the same core effectively creates a pool of resources (or service providers), which allows greater control over balancing between performance and power consumption.

Another question is durability; one or more cores may become temporarily or permanently inactive because of a fault. With the redundant resources, the "healthy" cores could take over the job and prevent the system from failure. Examples of such resource redundancy are *RAID* (Redundant Array of Independent Disks) and *RAIM* (Redundant Array of Independent Memory) data storage architectures. Both technologies improve

resilience and performance of storing information on disk or in memory. In general, such a redundant resource approach can be applied to any type of resource to achieve a trade-off between performance and reliability.

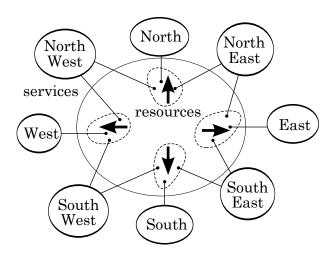

Nowadays the *Network-on-Chip* (NoC) architecture is increasingly popular, where devices communicate through a set of Point-to-Point (P2P) links that form network structures. A network is distributed over multiple link segments in order to allow concurrent communication between multiple devices and to reuse the same links for propagating data to different destinations. Essentially, a NoC provides and manages a distributed set of communication resources. Various topologies, depending on the routing protocol, provide different opportunities on what data propagation paths can be taken. For instance; on a regular 2D NoC mesh there are multiple shortest paths possible for the data travelling between two cores located in the opposite corners of the mesh. Theoretically, such a choice of a particular path can be regarded as a redundant/replaceable resource, which can be used for improving NoC performance, durability, and power consumption.

#### **Asynchronous NoCs**

With the increasing clock skew on smaller transistor sizes, planning multiple unrelated clocks independently driving separate time domains becomes a necessity. The system built on the concept of multiple clocks is called *GALS* (Globally Asynchronous, Locally Synchronous) system, initially proposed by D. M. Chapiro in [15]. It assumes splitting the design into individual modules with independent clock rates, which simplifies the task of timing closure and enables design reuse by allowing multiple designs with independent clock rates on the same chip. The communication latency, however, may have a significant impact on the overall system performance [30].

Essentially, GALS is a compromise between fully synchronous and fully asynchronous systems which may have various degrees of asynchrony in its communication layer. The basic GALS designs communicate via dedicated links (Figure 1.1a) where the communication is built by directly connecting these domains through special synchronous-to-synchronous (sync-sync) interfaces (Figure 1.1).

Figure 1.1: GALS evolution

As the number of independent cores grows, dedicated communication networks are created (Figure 1.1b). At this stage, the network itself may still be clocked; however, since this clock needs to cover the whole NoC area, the design had complications similar to those in systems with a global clock skew. The clock branches with high skew require special *mesochronous synchronizers* [42] that synchronize skewed clock branches belogning to the same clock domain, this may also result in extra latency for the inter-core communication. It was shown that with the smaller transistor size even more synchronization cycles may be needed, leading to the increased latency overhead [8], thus motivating the fully asynchronous networks on chip.

The complete removal of global clock from the NoC environment having fully asynchronous NoC implementation (Figure 1.1c) is the next step of the GALS evolution. Such a network does not have the issue of timing closure and only needs synchronizers to transfer data from asynchronous environment to clocked domains. As a result, the asynchronous NoC designs do not suffer as much the penalty of extra synchronization latency caused by synchronizers.

## **Smart Arbiters**

Because NoC communication resources are reused by multiple clients, additional arbitration circuitry is needed to manage resource utilization. *Arbiters* are designed to prevent multiple client accesses when the resource cannot serve more than one client at a time. Based on some form of communication, the arbiter forbids client accesses when the resource is not ready to be used. Alternatively, by granting a resource, the arbiter guaran-

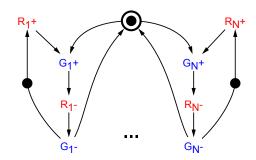

tees that the resource can be used without the risk of being interfered. This simple form of 1-of-N arbitration can be also extended to multiple resources. The M-of-N arbitration featuring N clients and M resources forms a double-sided conflict where multiple clients compete for the acquisition of a resource, and multiple resources also compete to access the clients (supposedly because a client cannot be engaged with more than one resource at a time) [78].

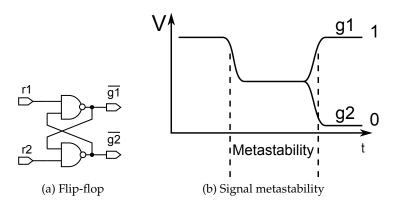

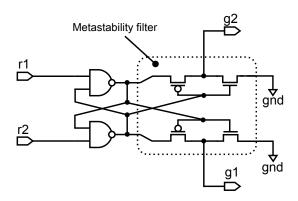

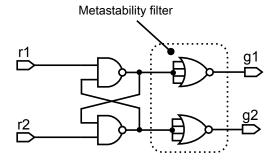

The asynchronous environment is difficult for arbitration because there are no timing expectations about when the requests may arrive, and the only way the arbiter can decide which request to grant is by serving requests based on their relative arrival time. Simple digital logic used in synchronous arbiters is not sufficient in this case because the arriving events may be too close leaving the arbiter in a metastable state [37]. The metastability in asynchronous arbiters has to be contained within known boundaries by using specialized circuitry; as a result, asynchronous arbiters are not so easy to design and scale.

The well known 1-of-N asynchronous arbiters are still being actively studied; however, the more general M-of-N arbiters also need to be considered in order to address the problems of the multi-resource utilization. This is the primary goal of this work.

Currently, there are no integrated design flows supporting asynchronous arbiters. Instead, these designs are often made "by hand" with no guarantees of correct operation in regards to deadlocks and hazards. For reliable solutions, the explicit support for verification is needed.

It is believed that smart asynchronous arbiters can help building the asynchronous routers, which in turn will allow creating sophisticated asynchronous NoCs with optimal utilization of available communication resources.

#### 1.2 Main Contributions

The first contribution of this thesis is a design of a multi-resource arbiter supporting *M*-of-*N* arbitration among active resource components. It directly serves the idea of providing interchangeable resources which improves the overall performance and reliability of a system. As an example, the Multiple-Input-Multiple-Output queue is created, which in

practice can be used for load balancing among a number of processors.

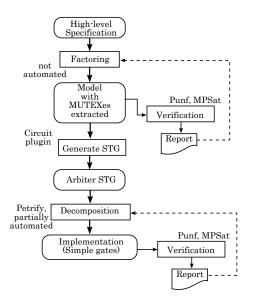

The second contribution is the design of gate-level EDA flow and its implementation as a plugin for the *Workcraft* [64] modelling environment. It supports high-complexity gates, timing assumptions, and non-deterministic components (such as MUTEXes), which is useful in designing small-to-medium sized asynchronous arbiters. The flow supports formal verification for deadlocks and hazards, which helps the design of new and the verification of existing circuits. This flow is evaluated through a complete design, modelling, and verification of the *priority arbiter*.

The third contribution is the design of a generalized arbiter based on the proposed flow. This arbiter can be used to solve a large variety of resource allocation tasks. It is presented at different degrees of abstraction, at high-level and at the level of decomposition. Timing estimations are made for the pipelined version of this arbiter, demonstrating its performance for the increasing number of arbiter clients.

# 1.3 Organisation of Thesis

- **Chapter 1: Introduction** motivates the necessity of the asynchronous multi-resource arbitration and briefly outlines the scope and contribution of the thesis.

- **Chapter 2: Background** describes the asynchronous circuits and their advantages and disadvantages in comparison with the clocked designs. It defines Petri nets, STGs and overviews their roles in specifying digital circuits at various degrees of abstraction.

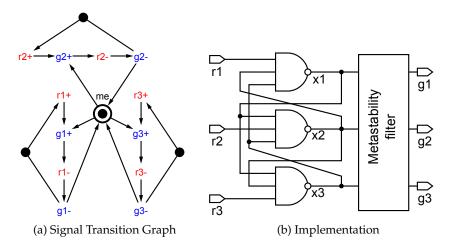

- Chapter 3: Review on Asynchronous Arbiters studies typical features characterising arbitration circuits. It reviews existing arbiter designs both analogue and digital. In this chapter multiple conventional arbiters are presented in order of increasing complexity starting from various 1-of-2 arbiters and advancing into scalable 1-of-*N* and *M*-of-*N* designs.

- **Chapter 4: Concurrent Multi-Resource Arbiter: Design and Applications** presents the initial solution to multi-resource arbitration with active resources. A number of

practical applications are also presented along with performance estimations comparing the design against existing alternative implementations in the area of MIMO queues.

**Chapter 5: Gate-level Design Flow** presents the gate-level EDA flow supporting arbiter models, which was implemented as part of the Workcraft modelling environment in an attempt to ease the STG based design flow. It also demonstrates how existing arbiter circuits can be modelled and verified based on the example of priority arbiter.

Chapter 6: Design of Generalized Arbiter presents the structure of the generalized arbiter developed with the flow proposed in previous chapter. The arbiter is able to tackle a large variety of allocation problems making it an invaluable circuit for designing advanced asynchronous NoC routers ensuring a high degree of link resource utilization.

**Chapter 7: Conclusions** summarises the major results achieved in this work and suggests the areas for future research.

# 1.4 Bibliography

- · Stanislavs Golubcovs, Delong Shang, Fei Xia, Andrey Mokhov, and Alex Yakovlev.

Concurrent Multi-Resource Arbiter: Design and Applications

Accepted for *IEEE Transactions on Computers*

- Stanislavs Golubcovs and Alex Yakovlev. Low Power Networks-on-Chip, chapter 4: Asynchronous Communications for NoCs, pages 71–109.

Springer Verlag, 2010.

- Delong Shang, Fei Xia, Stanislavs Golubcovs, and Alex Yakovlev. The magic rule of tiles: Virtual delay insensitivity.

In *PATMOS*, pages 286–296, 2009.

- Stanislavs Golubcovs, Delong Shang, Fei Xia, Andrey Mokhov, and Alex Yakovlev.

Multi-resource arbiter decomposition.

Technical Report NCL-EECE-MSDTR-2009-143, Newcastle University, February 2009.

- Stanislavs Golubcovs, Delong Shang, Fei Xia, Andrey Mokhov, and Alex Yakovlev.

Modular approach to multi-resource arbiter design.

In Asynchronous Circuits and Systems, 2009. ASYNC '09. 15th IEEE Symposium on, pages 107–116, May 2009.

- · Stanislavs Golubcovs, Andrey Mokhov, and Alex Yakovlev. Multi-resource arbiter design.

Technical report, UK Asynchronous Forum, Manchester, 2008.

# **Chapter 2**

# Background

# 2.1 Asynchronous Circuits

Asynchronous or self-timed circuits operate without a global clock sequentially updating the state of the system. They are formed of multiple control signals causing partial system state updates and operate in the continuous time domain, which provides certain advantages over the synchronous designs.

**Modularity** The asynchronous circuits are composed of modular blocks that intercommunicate through handshakes. It is possible to develop these blocks independently with different techniques and simply compose them together afterwards. Because the communication protocols usually do not have specific timing expectations, modules can work at different speeds without the risk of violating timing constrains. In contrast, clocked systems have to be designed with the specific clock signal in mind and a slight variation on the signal delay may have global implications.

## Variability

The shrinking of the layout feature sizes causes an increase in interconnect delay variability for both traditional die-to-die and emerging intra-die variations [83]. The delay variability also causes clock skew variations. For the  $0.25\mu m$  process the reported variability was already 25% [39]. And finally, the crosstalk capacitance can cause up to  $1.5\times$

delay variation [29]. All these factors require much more sophisticated timing analysis. Safety margins associated with the variability have to be increased at the cost of system performance.

Similar issues occur in self-timed designs. However, the number of timing assumptions is significantly less. The robust *delay-insensitive* designs allow the circuits to operate without explicit timing expectations on the delay of wires or gates, hence, variations in these delays do not prevent correct functionality.

The asynchronous circuits are highly adaptive to power supply variation. With less power, transistors would react slower, but with no strict timing constraints, such a design would still continue to work.

## **Power Consumption**

In synchronous systems, the clock signal needs to be propagated across the whole area of the chip, which makes it a major power consumer. The asynchronous design is based on more or less localized handshake communications. As a result, it often requires much less power to operate.

Another important aspect is event-based power consumption. In a synchronous system, the clock signal drives each clocked element of the circuit irrespective of real data changes. On the contrary, the asynchronous design is driven by the "on demand" philosophy. It dissipates power only when it is activated by the incoming request signal.

Static power consumption is related to the technology used and the area of the circuit. For CMOS technology of 130nm and above, static power consumption is a minor contributor. As it scales down to 90nm and beyond, the static (leakage) power becomes a greater concern. Again, asynchronous techniques allow applying power gating in a more flexible event-based way than in clocked circuits [38].

#### Performance

The rate of computation in synchronous systems is dependent on the *critical path*. It is the longest time, which takes a signal to propagate between two clocked components.

The critical path determines the clock rate at which components can be latched and has to include variations caused by different input data, high temperature, and low voltage supply. As a result, the synchronous circuit is as fast as the slowest path in its worst performance variation.

The asynchronous circuits operate through handshakes, which introduces overhead into the computation process. Each computation transaction has to explicitly end with the acknowledgement signal sent back to the requester, making the asynchronous computation less attractive. On the other hand, the asynchronous handshakes work as fast as the computation lasts. This leads to significant performance advantages, if the worst case delays far exceed the delay of an average computation.

# 2.2 Digital Circuits

Throughout this work, the concept of an asynchronous *digital circuit* is inherited from D. Muller's switching circuits [55]. A digital circuit is a set of binary signals (also called components or gates), where each signal is associated with a binary "current value". The signal is called *active*, when the signal value is "1" or *inactive*, when the signal value is "0". A signal may also have an associated Boolean function  $f(x_1, ..., x_n)$  specifying its "next value" depending on the *inputs of the signal*. For instance, the AND gate can be specified as  $a = b \cdot c$ , where a is the name of the signal, and b and c are the inputs for a. For convenience, the signal a may be written in its set/reset form:

$$a = \begin{cases} \uparrow & b \cdot c \\ \downarrow & \overline{b} + \overline{c} \end{cases}$$

A signal is *excited* when its next value function becomes different from its current value. This may happen when one of its inputs  $x_1, ..., x_n$  has changed. The excited signal may eventually align its value with the value of the associated function making the signal *stable* again. When the signal settles its value from excited to the stable state, it is said that the signal *fires* a transition. The timing it takes for this sort of transition to

complete is called the delay of the signal (or the gate delay), which may be arbitrarily long in the general case.

All signals of a circuit are subdivided into the *input*, *internal*, and *output signals*. The internal and the output signals represent implementation of a circuit, while the input signals represent the environment of the circuit (it is usually a simplification describing the behaviour of an environment on the signals, but not its implementation).

In contrast with the non-digital circuits (called the *analogue circuits*), signal changes from the excited to the stable state are instantaneous and never hold values outside the binary set  $\{0,1\}$ . It is also assumed that these digital signals never produce glitches due to the complexity of their function: for any single change among a signal inputs  $x_1, \ldots, x_n$ , the signal will either remain stable or become excited and eventually change its value (i.e., it will never make more than one transition for each input change).

Under the assumption of non-zero gate delays, it is also possible that the function change happens after the signal was excited already. The signal change from its excited state to the stable state denotes its *non-persistency*. The non-persistency of any of the internal or output signals is considered a *hazard* and wrong circuit operation. The non-persistency of an input signal is not considered a problem because that is outside the scope of circuit responsibility.

#### Classification

Asynchronous digital circuits fall into the following groups [75]:

- · Delay-insensitive circuits (DI) assume that the circuit is expected to work "correctly" regardless of its wire and gate delays. This class of DI circuits is considered the most robust with respect to process and environmental variations. In practice the class of delay-insensitive circuits is rather small [46].

- · Speed-independent circuits (SI) assume that the circuit is expected to work "correctly" regardless of its gate delays. This class of circuits assumes there is no delay in wires and the change of one signal value immediately affects all of the functions in other signals.

- · Quasi-delay-insensitive (QDI) circuits assume the presence of isochronic forks [46], where the wire delay branches are considered to have no difference. If it is assumed that a delay on a wire before its branching is part of the delay of a gate driving the wire, then QDI=SI. This class of circuits may also make assumptions about one-sided fork delays, where one branch of a fork is either the same or a slower branch, which are called the *asymmetric forks* (see Chapter 5 for more details). These forks impose fewer constraints on the design and are easier to enforce.

- · Self-timed circuits (also called circuits with timing assumptions), where the circuit is expected to work "correctly" if certain relative gate delay timing conditions are satisfied. In practice, such circuits are less reliable with respect to timing variations and need special attention during their layout. These circuits are fairly practical and help to greatly simplify the logic, when the *timing assumptions* are reasonable and easy to enforce by layout or additional delay elements.

### 2.3 Petri Nets

The *Petri net* model was introduced by Carl Adam Petri in his PhD thesis in 1962 [62, 56]. It is a mathematical formalism describing concurrent events, causalities between these events (also called transitions), and a dynamic state of a certain system. As opposed to the Finite State Machine (FSM) with a global state, the Petri net is described by a multiple of distributed states, which better corresponds to the nature of the asynchronous circuit events.

**Definition 2.1.** A Petri net is a quadruple, PN = (P, T, F, m) where:

*P* is a finite set of places

*T* is a finite set of transitions:  $(T \cap P = \emptyset)$

$F: (T \times P) \cup (P \times T) \rightarrow \mathbb{N}$  is a flow relation

$m: P \to \mathbb{N}$  is the marking of the net (also called the state of the net)

The definition means there are places and transitions interconnected with each other. A connection is only possible from a transition to a place or from a place to a transition. The marking is used to represent the dynamic state of a system. An example of a Petri net is shown in Figure 2.1a on the following page. Here F(p1,t1) = 1, F(p0,t1) = 2, ..., F(t2,p5) = 1, in the diagram it is shown by the number or directed arcs connecting places and transitions. Marking for places m(p1) = 1, m(p2) = 2, e.t.c., or in other words: p1 has 1 token and p2 has 2 tokens.

#### 2.3.1 Pre-set and Post-set

**Definition 2.2.** The *pre-set* of a transition t, denoted  ${}^{\bullet}t$ , is the set of places  $p \in {}^{\bullet}t \subseteq P$  such that  $p \in {}^{\bullet}t \Rightarrow F(p,t) > 0$ . Similarly, a pre-set of a place p, denoted  ${}^{\bullet}p$ , is the set of transitions  $t \in {}^{\bullet}p \subseteq T$  such that  $t \in {}^{\bullet}p \Rightarrow F(t,p) > 0$ . Symmetrically, a *post-set* of a transition (or a place) a, denoted  $a^{\bullet}$ , is the set of places (or transitions) b, such that  $b \in a^{\bullet} \Rightarrow F(a,b) > 0$ .

In the example on Figure 2.1a:  ${}^{\bullet}t1 = \{p0, p1, p2\}, t1^{\bullet} = \{p3, p4\}, {}^{\bullet}p2 = \emptyset, \text{ and } p2^{\bullet} = \{t1, t2\}.$

# 2.3.2 Enabling and Firing

**Definition 2.3.** A transition  $t \in T$  is *enabled* at a marking  $m_1$  if for any place  $p \in {}^{\bullet}t$ ,  $m_1(p) \ge F(p,t)$ . The enabled transition may *fire* producing a new marking  $m_2$ :

$$\forall p \in P : m_2(p) = m_1(p) - F(p,t) + F(t,p),$$

where each + and - are defined component-wise. In other words, firing t subtracts F(p,t) tokens from  $\bullet t$  for each  $p \in \bullet t$  and adds F(t,p) tokens to  $t^{\bullet}$  for each  $p \in \bullet t$ .

In the example (Figure 2.1a): the transition t1 is enabled because the marking m(p0) = 2, m(p1) = 1, m(p2) = 2 satisfies the flows F(p0, t1) = 2, F(p1, t1) = 1, and F(p2, t1) = 1. The transition t2 is not enabled because m(p4) < F(p4, t2).

Figure 2.1b demonstrates the result of firing transition t1. The tokens from t1 =  $\{p0, p2\}$  have been removed and added to t1 =  $\{p3, p4\}$  according to the flow function t. After this transition, there are tokens in t, t enabling transition t.

Figure 2.1: Petri net firing transition

# 2.3.3 Other PN Properties

#### **Traces**

A *trace* is a sequence of fired transitions in a Petri net; it is used to depict the path from its initial marking to any reachable marking. For instance, the trace from the marking in Figure 2.1a to the marking in Figure 2.1c is depicted with the trace  $t1 \rightarrow t2$ .

**Boundedness** The *K-bounded Petri nets* are the nets that for any reachable marking (any trace from the initial marking) have at most *K* token in any place:  $\forall p \in P : m(p) \leq K$ . Such Petri nets are interesting for the automated analysis tools because their reachable marking set is finite.

Most Petri nets presented in this thesis are 1-safe. A Petri net is called the *1-safe* when it is 1-bounded (for any reachable marking,  $\forall p \in P : m(p) \leq 1$ ).

**Deadlocks** The *deadlock state* is a special PN marking, where none of the transitions is enabled. A Petri net is *deadlock-free*, if there are no reachable markings leading to the deadlock state.

### 2.3.4 Signal Transition Graphs

The idea to describe digital circuits with Petri nets was independently proposed in [17] and in [67], it extends the Petri net model with a function mapping PN transitions to particular circuit signal transitions.

Figure 2.2: STG example of a C-element

**Definition 2.4.** *Signal Transition Graph*(STG) is a pair, STG = (PN, L) where:

PN is a Petri net PN = (P, T, F, m), and

*L* is a labelling function:  $L: T \to (S \in C, op \in \{+, -, \sim\}) \cup dummy$

The labelling function associates events of the Petri net with circuit signal transitions. Transitions denoted with "+" are the raising signal transitions from "0" to "1". Transitions denoted with "-" are the falling signal transitions from "1" to "0". Transitions denoted with " $\sim$ " are the toggle transitions switching signals from "0" to "1" or from "1" to "0" depending on the current value of the related signal.

Transitions that are not associated with any signals are called *dummy transitions*. Such transitions can be useful for shifting the marking of an STG without affecting states of the modelled signals.

### Simplified Notation

Throughout this thesis the simplified notation of the STG models is used. This notation sometimes omits the " $\sim$ " sign for the toggle transitions and the labelled transition boxes are replaced by labels. Finally, places in diagrams are often omitted when  $| ^{\bullet} p | = | p ^{\bullet} | = 1$ , which as a result makes the model more compact and easier to read.

Figures 2.2a and 2.2b present the STG of a 2-input C-element. The model presents two input signals a and b (shown in red), these signals form the environment of the model. The output signal c represents the output of the C-element (shown in blue).

The diagram shows that the output can raise or fall only after both inputs have

transitioned to 1 or to 0 correspondingly. In this example the arcs from c to a and from c to b introduce an assumption that the environment signals, once transitioned, would not change until the output signal has settled.

### **Complete State Coding**

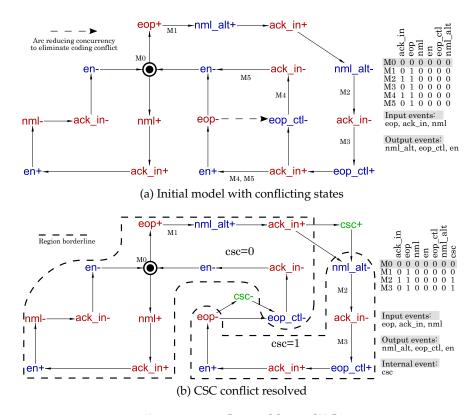

The Complete State Coding property holds when an STG does not have a complete state coding conflict.

The Complete State Coding conflict occurs when an STG has two reachable states in which the values of all the signals coincide but the sets of enabled output and internal transitions are different. In practice it means that these conflict states have ambiguous next state functions and cannot be directly implemented as a digital circuit, hence, the absence of CSC conflict is a necessary condition for a circuit to be synthesized.

Later in this chapter an example of CSC conflict will be considered as well as ways to resolve it.

# 2.4 Asynchronous Circuit Primitives

## 2.4.1 C-element

The *C-element* introduced by Muller [55] is a latched component that changes its value when all of its inputs make a single transition. The element depiction in diagrams is as shown in Figure 2.3. The basic 2-input C-element can be described by the equation  $q = a \cdot b + (a + b) \cdot q$ , or in the set/reset form:

$$q = \begin{cases} \uparrow & a \cdot b \\ \downarrow & \overline{a} \cdot \overline{b} \end{cases}$$

It means that the output of the gate is set when both inputs are active, it is reset when both inputs are inactive, and it stays *unchanged* otherwise. The 3-input C-element is correspondingly defined for three inputs:  $q = a \cdot b \cdot c + (a + b + c) \cdot q$ .

The asymmetric C-element has different sets of inputs for its set and reset functions. An

Figure 2.3: C-element examples

Figure 2.4: Toggle component

asymmetric C-element with all four inputs activating it and only two inputs deactivating it is shown in 2.3c. It is described by: $q = a \cdot b \cdot c \cdot d + (a + b) \cdot q$  or the set/reset notation:

$$q = \begin{cases} \uparrow & a \cdot b \cdot c \cdot d \\ \downarrow & \overline{a} \cdot \overline{b} \end{cases}$$

so it is reset when both a = 0 and b = 0, regardless of the c and d values.

# 2.4.2 Toggle Component

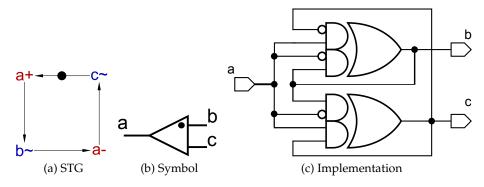

The *toggle component* is a latch that has one input a and two outputs b and c (Figure 2.45.1). It toggles b on every raising transition of a and toggles c on every falling transition of a. The initial state in this element can be either "0" or "1". When not mentioned otherwise, the initial state of all the STGs with toggle transitions " $\sim$ " is initiated with "0".

#### 2.4.3 Decision Wait Element

The decision-wait (DW) element (also known as the JOIN component [32]) is a latch with a number of rows and columns. The outputs are formed for each intersection between

Figure 2.5: Decision-wait element

Figure 2.6: Basic handshake protocols

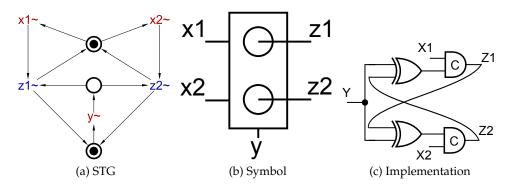

columns and rows. When there is a single change of one column and one row input, the corresponding intersection also toggles its value. An example of DW element with two rows and one column is shown in Figure 2.5.

# 2.5 Asynchronous Signalling

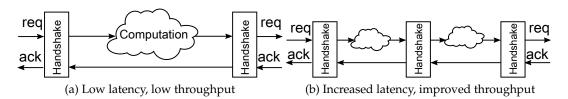

#### 2.5.1 Handshake Protocols

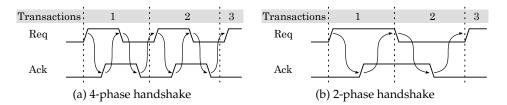

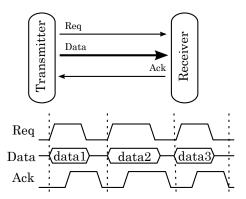

Handshakes provide asynchronous systems flexibility of composing independent modules into communicating systems through well defined interfaces. A handshake is the two-way request-acknowledge communication transaction featuring the active participant initiating the handshake with a request for a service, and the passive side, responding to the initial request with the acknowledgement stating that the work requested has been done [75]. Depending on the signalling scheme used, a handshake can be either the 4-phase (Figure 2.6a) or the 2-phase (Figure 2.6b).

The *4-phase handshake* is related to the level-based signalling. It is also commonly known as a return-to-zero (RTZ) method. It forms the sequence of the following events:

**Phase 1**  $Req \uparrow - A$  request is issued, new communication cycle has started.

**Phase 2**  $Ack \uparrow$  – The request is acknowledged. The requester may proceed with the transaction.

**Phase 3**  $Req \downarrow -$  The requester is resetting to the initial state and waiting for the responder to reset as well.

**Phase 4**  $Ack \downarrow$  – The initial state of the handshake is restored, can process to Phase 1.

The 2-phase handshake can be related to the transition or the pulse based signalling. It has only two phases per handshake:

**Phase 1** Either  $Req \uparrow \text{ or } Req \downarrow - \text{A}$  request is issued and the new communication cycle has been started.

**Phase 2** Either  $Ack \uparrow$  or  $Ack \downarrow$  The request is acknowledged, can proceed to Phase 1.

When both Req and Ack signals are used, the event detection on both sides can use these signals as a reference. If  $Req \neq Ack$  the responder knows that there was an event on the request line. If Req = Ack then the requester knows that the acknowledgement has been sent.

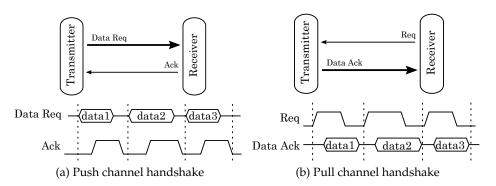

## 2.5.2 Channel Types

The type of the channel differs depending on which side of a handshake is transmitting the data. When the transmitter is making the initial request, it forms the so called *push channel* as data being sent is associated with the request event (Figure 2.7a). In contrast, the *pull channel* transmits data with the acknowledgement phase (Figure 2.7b).

In a more general view, the handshake with no data transition associated is called the *nonput channel*. It does not transport the data, but can still be used to synchronize the communicating modules. Finally, if both the transmitter and receiver attach some information to the request and acknowledge signals, such a communication is called the *biput channel* [75].

Figure 2.7: Channel types

Because of the variety of data transmission directions, it is convenient to call the participants the *active side* (or the master) initiating the request and the *passive side* (or the slave) responding to the initial request with the acknowledgement.

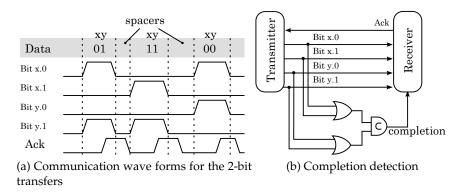

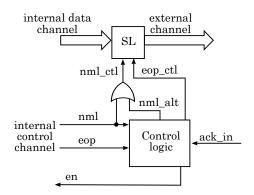

# 2.5.3 Delay-insensitive Encoding