School of Electrical and Electronic Engineering

# Compositional Approach to Design of Digital Circuits

Arseniy Alekseyev

Technical Report Series

NCL-EEE-MICRO-TR-2014-191

Contact:

${\bf rotsor@gmail.com}$

Supported by EPSRC grants  $\mathrm{EP/G037809/1}$  and  $\mathrm{EP/K001698/1}$

NCL-EEE-MICRO-TR-2014-191 Copyright © 2014 University of Newcastle upon Tyne

School of Electrical and Electronic Engineering, Merz Court, University of Newcastle upon Tyne, Newcastle upon Tyne, NE1 7RU, UK

http://async.org.uk/

#### University of Newcastle upon Tyne School of Electrical and Electronic Engineering

# Compositional Approach to Design of Digital Circuits

by Arseniy Alekseyev

PhD Thesis

# Contents

| 1 Introduction |            |         | ion                                                             | 1  |

|----------------|------------|---------|-----------------------------------------------------------------|----|

|                | 1.1        | Contri  | ibutions                                                        | 4  |

|                | 1.2        | Overv   | iew                                                             | 4  |

| <b>2</b>       | Background |         |                                                                 | 8  |

|                | 2.1        | Hands   | shake circuits                                                  | 8  |

|                | 2.2        | Petri i | nets                                                            | 11 |

|                | 2.3        | Condi   | tional Partial Order Graphs                                     | 17 |

|                | 2.4        | Agda    |                                                                 | 19 |

|                |            | 2.4.1   | Function definitions and algebraic data types                   | 20 |

|                |            | 2.4.2   | Inductive types and recursion                                   | 21 |

|                |            | 2.4.3   | Indexed types and propositions                                  | 21 |

| 3              | Imp        | roved   | Parallel Composition                                            | 25 |

|                | 3.1        | Introd  | luction                                                         | 25 |

|                | 3.2        | Impro   | ved parallel composition                                        | 29 |

|                | 3.3        | Discus  | ssion                                                           | 32 |

|                | 3.4        |         |                                                                 | 33 |

|                | 3.5        |         |                                                                 | 34 |

|                | 3.6        | Balsa   | workflow optimisation through STG resynthesis                   | 37 |

|                |            | 3.6.1   | Support of Breeze handshake circuits as interpreted graph model |    |

|                |            |         | in Workcraft                                                    | 40 |

|                |            | 3.6.2   | STG specifications of individual handshake components           | 41 |

|                |            | 3.6.3   | An example: GCD controller                                      | 42 |

|                |            | 3 6 4   | Experimental results                                            | 45 |

|   | 3.7 | Summ                                             | nary                                                    | 46  |  |  |

|---|-----|--------------------------------------------------|---------------------------------------------------------|-----|--|--|

| 4 | The | eory of                                          | Parametrised Graphs                                     | 48  |  |  |

|   | 4.1 | Introd                                           | luction                                                 | 48  |  |  |

|   | 4.2 | Paran                                            | netrised Graphs                                         | 50  |  |  |

|   |     | 4.2.1                                            | Specification and composition of instructions           | 57  |  |  |

|   | 4.3 | Algeb                                            | raic structure of Parametrised Graphs                   | 58  |  |  |

|   | 4.4 | Transitive Parametrised Graphs and their algebra |                                                         |     |  |  |

|   | 4.5 | 4.5 Case study                                   |                                                         |     |  |  |

|   |     | 4.5.1                                            | Phase encoders                                          | 65  |  |  |

|   | 4.6 | Machi                                            | ine-assisted formalisation of Parametrised Graph theory | 67  |  |  |

|   |     | 4.6.1                                            | Graph Algebra                                           | 68  |  |  |

|   |     | 4.6.2                                            | Parametrised Graphs                                     | 70  |  |  |

|   |     | 4.6.3                                            | Parametrised Graph formulae                             | 71  |  |  |

|   |     | 4.6.4                                            | Formula equivalence                                     | 72  |  |  |

|   |     | 4.6.5                                            | Normal form                                             | 73  |  |  |

|   |     | 4.6.6                                            | Normalisation algorithm                                 | 74  |  |  |

|   | 4.7 | Summ                                             | nary                                                    | 77  |  |  |

| 5 | Pro | cessor                                           | instruction set encoding                                | 79  |  |  |

|   | 5.1 | Introd                                           | luction                                                 | 79  |  |  |

|   | 5.2 | Proble                                           | em statement                                            | 82  |  |  |

|   |     | 5.2.1                                            | Overview                                                | 84  |  |  |

|   |     | 5.2.2                                            | Globally optimal encoding                               | 86  |  |  |

|   | 5.3 | SAT f                                            | formulation                                             | 86  |  |  |

|   |     | 5.3.1                                            | Weakly optimal encoding                                 | 87  |  |  |

|   |     | 5.3.2                                            | Globally optimal encoding                               | 88  |  |  |

|   |     | 5.3.3                                            | Support for dynamic variables                           | 91  |  |  |

|   | 5.4 | Proces                                           | ssor design example                                     | 92  |  |  |

|   |     | 5.4.1                                            | Instructions encoding                                   | 98  |  |  |

|   |     | 5.4.2                                            | Microcontroller synthesis                               | 100 |  |  |

|   | 5.5 | Summ                                             | nary                                                    | 102 |  |  |

| 6            | Conclusions |                                    |    | 13 |

|--------------|-------------|------------------------------------|----|----|

|              | 6.1         | Improved parallel composition      | 10 | )3 |

|              | 6.2         | Parametrised Graphs theory         | 10 | )4 |

|              | 6.3         | Processor instruction set encoding | 10 | )5 |

|              | 6.4         | Future work                        | 10 | )5 |

| $\mathbf{A}$ | Fori        | mal proof of PG Algebra properties | 10 | 7  |

# List of Figures

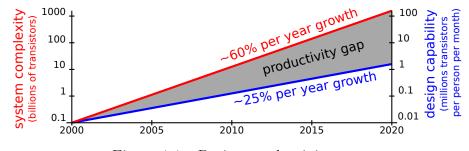

| 1.1  | Design productivity gap                                            | 1  |

|------|--------------------------------------------------------------------|----|

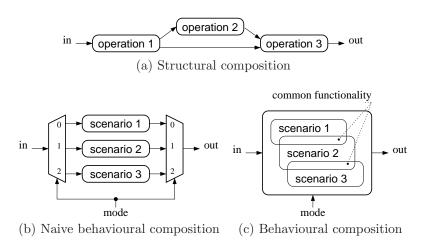

| 1.2  | Composition basics                                                 | 3  |

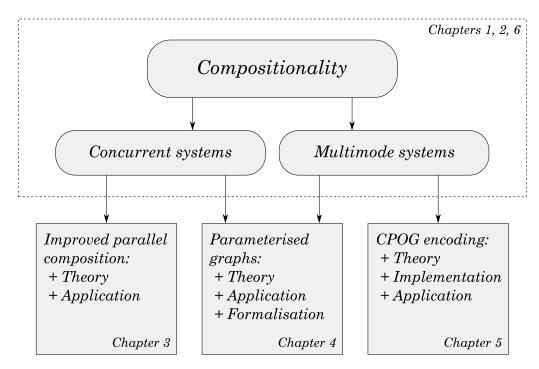

| 1.3  | Thesis structure                                                   | 6  |

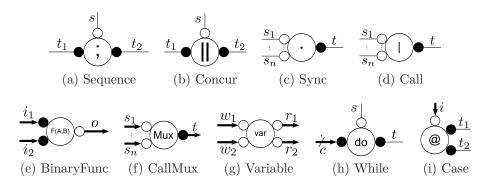

| 2.1  | Handshake components                                               | 11 |

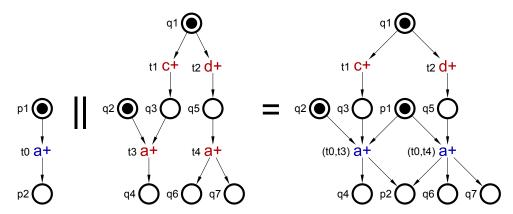

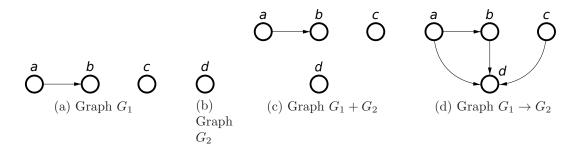

| 2.2  | Parallel composition example                                       | 16 |

| 2.3  | An example of a transition contraction                             | 16 |

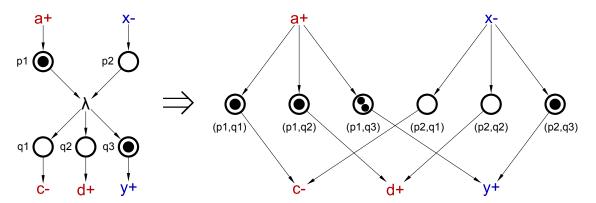

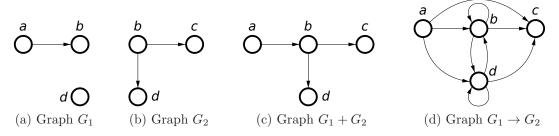

| 2.4  | Graphical representation of CPOGs and their projections            | 18 |

| 3.1  | Example of standard STG composition                                | 26 |

| 3.2  | Improved STG composition                                           | 27 |

| 3.3  | Equivalence preservation by improved parallel composition          | 30 |

| 3.4  | Example of invalid place removal                                   | 31 |

| 3.5  | Example of enforcing injective labelling in an STG                 | 32 |

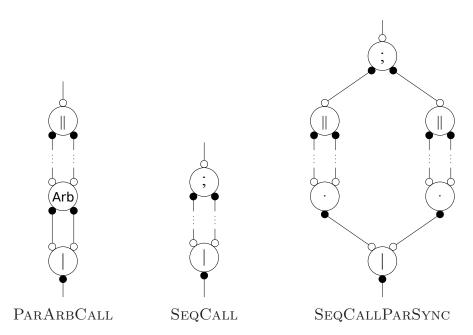

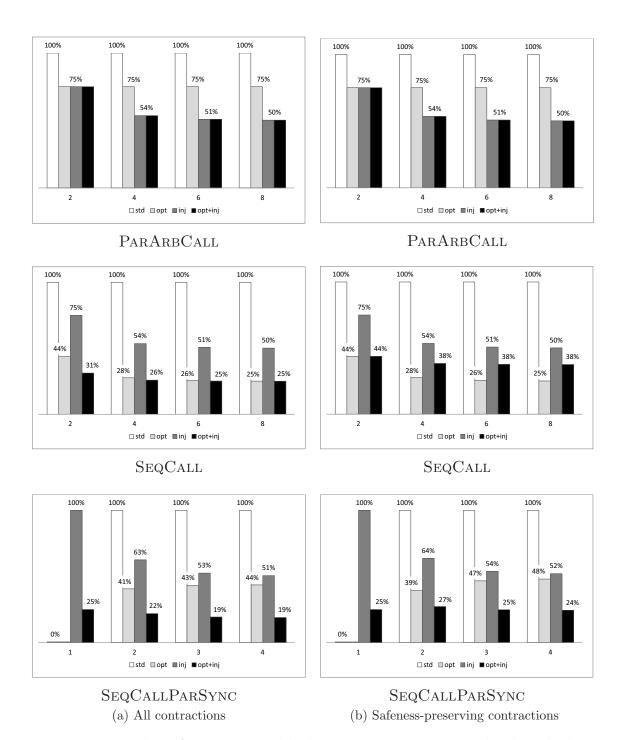

| 3.6  | Scalable Balsa controllers used in experiments                     | 35 |

| 3.7  | Number of non-contractible dummy transitions, normalized to the    |    |

|      | best value achieved                                                | 36 |

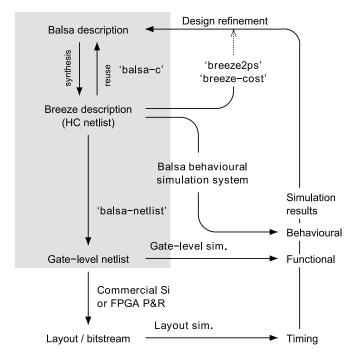

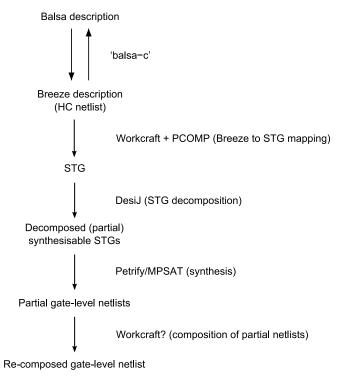

| 3.8  | Balsa design workflow                                              | 38 |

| 3.9  | Modified Balsa workflow                                            | 39 |

| 3.10 | Pure control path handshake components and their respective STGs . | 41 |

| 3.11 | Data path control components and their respective STGs             | 43 |

| 3.12 | Data-control interface components and their respective STGs        | 44 |

| 3.13 | Breeze Handshake Circuit model of a GCD block                      | 45 |

| 4.1  | Overlay and sequence example (no common vertices)                  | 51 |

| 4.2  | Overlay and sequence example (common vertices)                     | 51 |

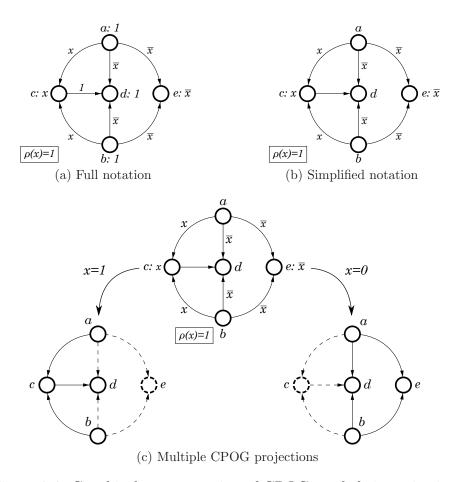

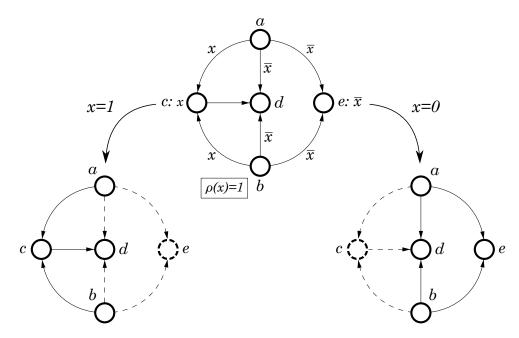

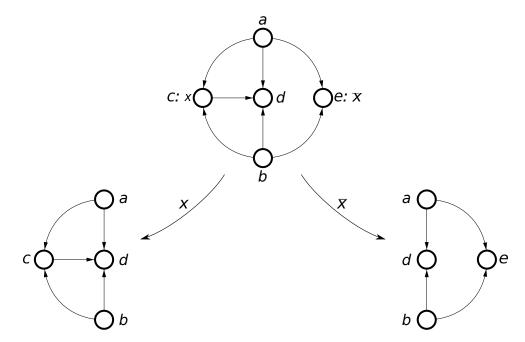

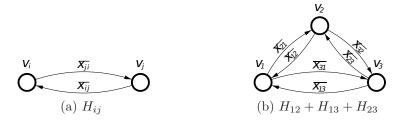

| 4.3 | PG specialisations: $H _x$ and $H _{\overline{x}}$                | 56  |

|-----|-------------------------------------------------------------------|-----|

| 4.4 | Simplifying expression (4.2) using the Closure axiom              | 61  |

| 4.5 | The PG from Fig. 4.3 simplified using the Closure axiom, together |     |

|     | with its specialisations                                          | 65  |

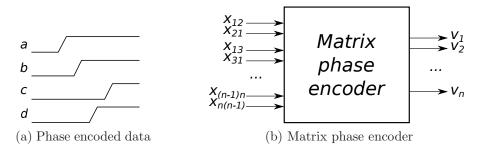

| 4.6 | Multiple rail phase encoding                                      | 66  |

| 4.7 | PGs related to matrix phase encoder specification                 | 67  |

|     |                                                                   |     |

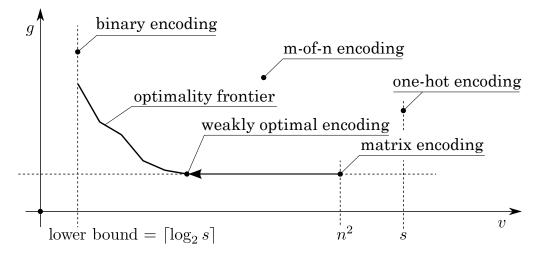

| 5.1 | The optimality frontier                                           | 81  |

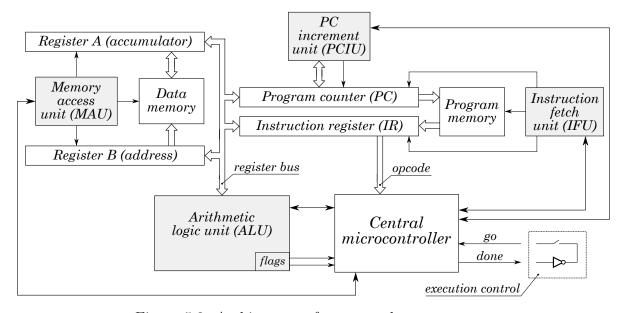

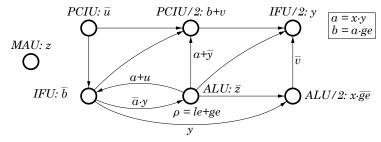

| 5.2 | Architecture of an example processor                              | 94  |

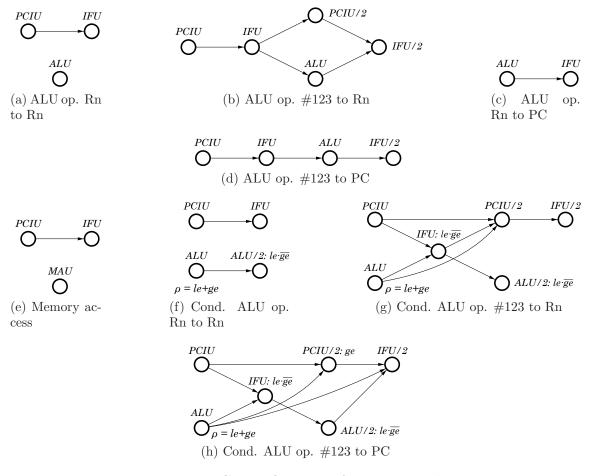

| 5.3 | TPG specifications of instruction classes                         | 94  |

| 5.4 | Optimal 3-bit instruction opcodes and the corresponding TPG spe-  |     |

|     | cification of the microcontroller                                 | 96  |

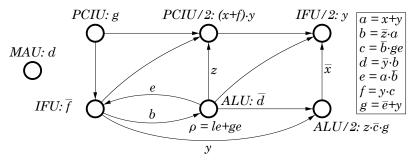

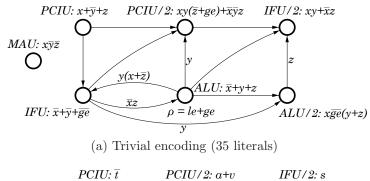

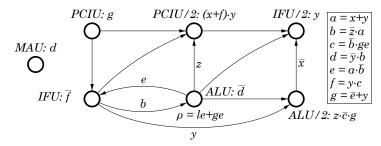

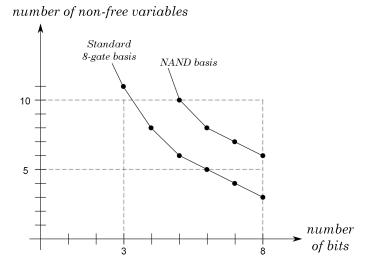

| 5.5 | Synthesised CPOGs                                                 | 99  |

| 5.6 | Comparison of different gate bases                                | 100 |

# List of Tables

| 3.1 | Costs of individual components                                      | 46  |

|-----|---------------------------------------------------------------------|-----|

| 3.2 | Cost of optimally split full GCD circuit                            | 47  |

| 4.1 | Two instructions specified as partial orders                        | 58  |

| 5.1 | Synthesised instruction codes                                       | 98  |

| 5.2 | Encoding of conditions with dynamic variable $ge \dots \dots \dots$ | 101 |

#### List of Abbreviations

- ALU Arithmetic Logic Unit

- CAD Computer Aided Design

- **CNF** Conjunctive Normal Form

- CSC Complete State Coding

- **CSP** Communicating Sequential Processes

- **CPOG** Conditional Partial Order Graph

- CPU Central Processing Unit

- DAG Directed Acyclic Graph

- **EDA** Electronic Design Automation

- GALS Globally Asynchronous Locally Synchronous

- **HOL** Higher Order Logic

- IC Integrated Circuit

- IFU Instruction Fetch Unit

- **IP** Intellectual Property

- **IR** Instruction Register

- ISA Instruction Set Architecture

- $\mathbf{MAU}$  Memory Access Unit

- NP Nondeterministic Polynomial

- **PC** Program Counter

- **PCIU** Program Counter Increment Unit

- **PG** Parameterised Graph

- PN Petri Net

- QBF Quantified Boolean Formula

- SAT Boolean Satisfiability Problem

- SoC System on Chip

- STG Signal Transition Graph

- TPG Transitive Parameterised Graph

- VLSI Very Large-Scale Integration

#### Abstract

In this work we explore compositional methods for design of digital circuits with the aim of improving existing methodoligies for design reuse. We address compositionality techniques looking from both structural and behavioural perspectives.

First we consider the existing method of handshake circuit optimisation via control path resynthesis using Petri nets, an approach using structural composition. In that approach labelled Petri net parallel composition plays an important role and we introduce an improvement to the parallel composition algorithm, reducing the number of redundant places in the resulting Petri net representations. The proposed algorithm applies to labelled Petri nets in general and can be applied outside of the handshake circuit optimisation use case.

Next we look at the conditional partial order graph (CPOG) formalism, an approach that allows for a convenient representation of systems consisting of multiple alternative system behaviours, a phenomenon we call behavioural composition. We generalise the notion of CPOG and identify an algebraic structure on a more general notion of parameterised graph. This allows us to do equivalence-preserving manipulation of graphs in symbolic form, which simplifies specification and reasoning about systems defined in this way, as displayed by two case studies.

As a third contribution we build upon the previous work of CPOG synthesis used to generate binary encoding of microcontroller instruction sets and design the corresponding instruction decoder logic. The proposed CPOG synthesis technique solves the optimisation problem for the general case, reducing it to Boolean satisfiability problem and uses existing SAT solving tools to obtain the result.

### Acknowledgements

I am grateful to everyone who made the completion of this work a reality by sharing their knowledge, assisting directly and supporting me emotionally.

My supervisor, Alex Yakovlev, guided me throughout the research programme and supported me at all times in many ways. I am thankful to Andrey Mokhov, Victor Khomenko, Ivan Poliakov and my other colleagues for their contributions to the work being presented, their participation in discussions and criticism. Special thanks go to Alexei Iliasov and Danil Sokolov for providing immense help in reviewing and restructuring the thesis into its present form. Without them this would not have been possible.

Separate thanks go to the organisations supporting me financially. This work was supported by a studentship from Newcastle University EECE school, EPSRC grant EP/G037809/1 (VERDAD) and EPSRC grant EP/K001698/1 (UNCOVER).

## Chapter 1

### Introduction

One of the major challenges for the future of semiconductor industry is the problem of overcoming the design productivity gap. This gap is caused by the exponential complexity growth of electronic systems [46] while the capability of design tools cannot cope with this pace, see Fig. 1.1. The only way to deal with the increasing complexity of Integrated Circuits (ICs) is to improve the efficiency of the design process, in particular, by heavily reusing system components and by advancing the design automation methods.

It has been predicted by ITRS [2] that in order to address the productivity gap challenge, by 2020 at least 90% of the complex circuits should be built of previously designed components. This rises the need for compositional (or modular) design principles where the timing of individual modules is independent of the rest of the system and therefore requires delay insensitive communication between the modules. This communication discipline is natural for asynchronous circuits where the data transfer is accompanied by request-acknowledgement handshaking between the

Figure 1.1: Design productivity gap

sending and the receiving counterparts. On this pathway the previously designed Intellectual Property (IP) cores will need to be adapted to the new modular architectures. The least intrusive is the Globally Asynchronous Locally Synchronous (GALS) approach [10] where special wrappers [24,47] are built around synchronous modules to convert their communication into asynchronous handshake style. Another alternative is desynchronisation techniques [15] where the global clock is replaced by a distributed control which determines when the computation is complete and the output result is ready to be consumed. This control may take different forms, from a delay line matching the critical path of the module [16] to explicitly introduced completion detection logic [34].

The remaining 10% of the IC components, as well as the interface and control logic to support the interconnect and communication flexibility, will still need to be designed from scratch. One way is to design those components in traditional synchronous way and then apply the previously discussed techniques to comply with the delay insensitive interface requirements. This, however, may result in suboptimal solutions in terms of circuit area, computation speed and energy consumption. Better results can be achieved if the components are designed and implemented with their asynchronous environment in mind [36]. However, the logic synthesis of asynchronous circuits is computationally expensive and not applicable to large modules. This is due to high level of concurrency in truly asynchronous systems which results in a state space explosion. The computation complexity problem has been successfully addressed in the syntax-driven translation [22] approach which is based on direct mapping of a specification into hardware components without going through the state space exploration (it is assumed that there is one-to-one correspondence between the specification language constructs and the library of available components).

The major drawback of the circuits obtained by the syntax-driven translation is the suboptimal performance of their control structures [53]. In order to resolve this issue the control models of all the components need to be composed together and resynthesised exploiting the benefits of their joint optimisation. Existing resynthesis methods are based on parallel composition of component models expressed in form of Petri nets [25]. However, the efficient parallel composition of the component models is still an open question and is one of the primary goals of this thesis.

The composition of circuit components is of structural nature - they are combined

Figure 1.2: Composition basics

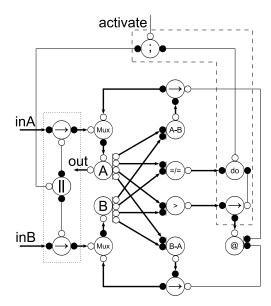

via input-output interfaces according to the casual dependency between the operation they perform, as shown in Fig. 1.2a. Another compositional aspect is a combination of several mutually exclusive behaviours in the same circuit. A naive way to build such a circuit is to implement the different behaviour scenarious in separate modules and structurally compose them with the use of multiplexers and demultiplexers, as shown in Fig. 1.2b. A mode selection code on the (de)multiplexors determines the current scenario. While this is a valid implementation of multi-modal functionality, it ignores the mutually exclusive feature of the implemented behaviours and ignores a possibility of partial hardware reuse for common functionality, as shown in Fig. 1.2c.

A model which naturally captures the structural and behavioural aspects of composition in a single formalism is Conditional Partial Order Graphs (CPOGs) [39]. This graph-based model is capable of expressing the structural composition by means of causality arcs (similar to Petri nets) and the behavioural composition by means of Boolean "visibility" conditions on its vertices. While CPOGs is a convenient tool for reasoning on small benchmarks, it lacks the means for capturing and transformation of large systems. The first goal of this thesis is to generalise the CPOGs model and transition from the acyclic graphs representing partial orders into a universal Parameterised Graphs (PGs). The second goal is to introduce a theory for PG manipulation in algebraic form, which enables equivalence-preserving manipulation of graphs in symbolic form and simplifies specification and reasoning about complex systems.

The Boolean conditions on graph vertices can be expressed in various forms targeting different optimisation criteria. In the context of digital circuit design these conditions are subsequently implemented as the hardware control logic, therefore such optimisation targets as minimising the number of control variables and/or reducing the complexity of logical expressions, is of paramount importance. The ambitious goal of this thesis is to solve the optimisation problem for the general case, to express it in terms of Boolean satisfiability problem and to employ the existing SAT solving tools for obtaining the best result.

#### 1.1 Contributions

The main contributions of the thesis are as follows:

- Improved parallel composition: a novel method for composition of models specified with labelled Petri Nets.

- **PG** theory: CPOG generalisation to Parametrised Graph formalism and mechanised proof of its algebraic properties.

- PG Synthesis: a technique for synthesis of processor instruction decoder using instruction sets specified with Parametrised Graphs.

- CAD tool support: automation for the above, including improved parallel composition and encoding of TPG specifications using Workcraft framework.

#### 1.2 Overview

Handshake circuits [7] are widely applied in the design and synthesis of real-life hardware. One prominent problem is obtaining an efficient implementation from a *structural* compositional specification. Syntax-based synthesis tools such as Balsa [22] are unable to take into account the compositional behaviour of STGs corresponding to handshake circuit components. To address this issue we propose a technique that selectively composes STGs of related components to obtain a smaller and more performant circuit without suffering state space explosion commonly associated with

Petri net based techniques [60]. This transformation, which we refer to as resynthesis [4,11,33,52], is accomplished in three stages. First, we apply a heuristic to identify the most promising candidates for STG-level composition. Second, we perform a parallel composition of the selected component STGs and as a result obtain a new handshake circuit with custom components, functionally equivalent to a combination of elementary components. Finally, a gate-level implementation is obtained from the new handshake circuit via a component-wise synthesis of STGs.

Unfortunately, the standard definition of parallel composition almost always yields a 'messy' Petri net, with many implicit places, causing performance deterioration in techniques that are based on structural methods such as the resynthesis approach. To counter this, we propose an improved algorithm for computing the parallel composition. The algorithm generally produces nets with fewer implicit places that are better suited for subsequent application of structural methods [3].

In addition to purely structural composition of STGs, it is also beneficial to consider a mixture of structural and behavioural composition. Conditional Partial Order Graphs (CPOG) [39] is a graph-based notation supporting compact representation and efficient manipulation of both structural and behavioural composition styles. As one example, when developing complex circuit, it is often necessary to consider several operational modes of a circuit [44,62]. For this, one needs methodologies and tools to exploit similarities between the individual modes and hence lift the level of discourse to behaviour families. This necessitates that behaviours are managed in a compositional way: the specification of the system must be composed from specifications of its blocks. Furthermore, since the approach is intended to be a part of a safety critical toolchain, it is essential that such a specification is amenable to mechanised reasoning and transformation.

In Chapter 4 we propose an extension of the CPOG formalism, called Parameterised Graph (PG). PGs deal with general graphs rather than just partial orders. We introduce an algebra of Parameterised Graphs by specifying the equivalence relation via a set of axioms, which we prove to be sound, minimal and complete [43]. This result allows one to manipulate a PG model as an algebraic expression applying the bi-directional rewrite rules of this algebra. This is in contrast to the CPOG formalism that does not offer a unifying algebraic structure. We demonstrate the usefulness of the developed formalism with two case studies coming from the area of

Figure 1.3: Thesis structure

microelectronics design.

The CPOG formalism can be applied to merge several distinct behaviours into a single compact CPOG [39]. As one example, this has been previously used to synthesise control logic for instruction decoding. In this thesis (Chapter 5) we improve upon this work by offering a powerful technique to automatically discover an optimal encoding and synthesise a matching optimal decoding circuit. From the outset, we consider a larger set of potential solutions which enables us to formulate the global optimality criterion. We use an automated satisfiability solving techniques to find an optimal solution [40].

To summarize the thesis structure,

- Chapter 2 covers the basics of handshake circuits, signal transition graphs and conditional partial order graphs.

- Chapter 3 describes the proposed improved parallel composition algorithm.

The contents of this chapter is based on the results published previously in [3].

- Chapter 4 introduces Parametrised Graph (PG) theory, defining and study-

ing an algebraic structure that generalises Conditional Partial Order Graph formalism. This chapter is based on the results previously published in [43].

- Chapter 5 describes a technique for optimal encoding of processor instruction sets defined using PG formalism. This chapter is based on the results previously published in [40]. An earlier version of this paper has qualified for a Best Paper Award at the ACSD conference.

- Chapter 6 summarises the achieved results and proposes ideas for future research.

- Appendix contains formal proofs in form of Agda source code for the PG Algebra properties discussed in Chapter 4.

The relationship between chapters is illustrated in Figure 1.3.

### Chapter 2

## Background

This chapter introduces a brief overview of the major techniques and models used throughout the thesis. In particular, handshake circuits – a specification formalism for synthesis of self-timed hardware; Petri nets – a graph-based notation for reasoning about concurrent behaviour; conditional partial order graphs (CPOG) – a versatile notation for describing a family of partial orders.

#### 2.1 Handshake circuits

One of the approaches to design of asynchronous circuits is syntax-directed mapping with handshake circuits as an intermediate format. The parse tree of a program source code written in a CSP-style [26] language can be interpreted as a graph of components, connected with communication links called handshake channels. The components can then be individually mapped to gate-level implementations with complete circuit derived by implementing the handshake channels with wires.

This approach has been first used by Philips in their Tangram [29] design tool and later made publicly available when the similar free Balsa [22] system has been released.

This thesis will be working with Balsa handshake components.

A handshake activation h is said to *enclose* a process p if p can only start after h gets a request and h can get an acknowledgement only after p gets finished.

A handshake circuit consists of handshake components which interact by request/ acknowledgment handshaking over communication channels. Each handshake component is specified by a set of ports and a process communicating over those ports. A protocol is assigned to each port, which specifies whether the process initiates the handshakes over an active port or awaits for the other party over a passive port. It also specifies the direction and size of data transferred during the handshakes. Each channel connects two ports of the same data size with one port being active and the other being passive. Active input ports and passive output ports are called pull ports while the pasive input and active output ports are called push ports.

On diagrams used in this thesis we display handshake components with large circles with a process symbol inside and handshake ports with small circles where filled circle stands for active port and hollow circle stands for passive port. Channels are displayed as lines between the corresponding ports with the direction of the arrow corresponding to the direction of data flow.

The defining feature of a handshake component is the process associated with it. In Balsa there are about fifty types of processes with each having its own behaviour.

An important notion used to describe behaviours is channel activation. Activation is a process starting with a request being sent from the active port to the passive port and ending with an acknowledgement being sent back. The behaviour of a channel can be described as activation repeated indefinitely. For data channels activation additionally determines the period of time the values on the data wires remain valid.

Processes, including activations, are subject to a notion of *enclosure* to describe temporal relationship between them. It is said that a process p is enclosed into a process q when the beginning of p comes after the beginning of q while the end of p comes before the end end of q.

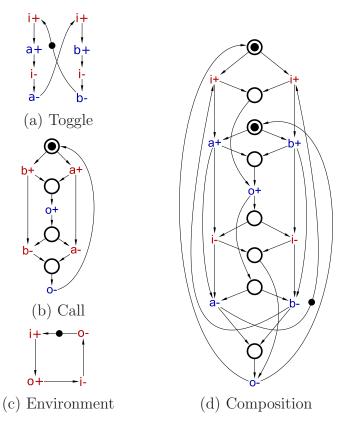

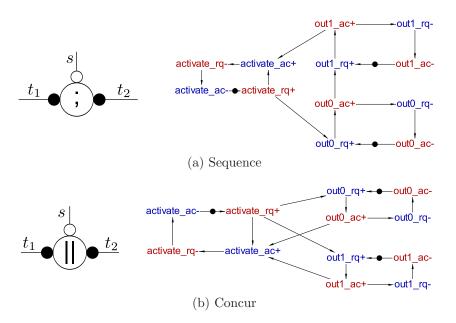

- Sequence (Fig. 2.1a) is a component with three control ports: a passive port s and two active ports  $t_1$  and  $t_2$ . The behaviour of the component is as follows: each activation on s encloses the process consisting of sequential activation on  $t_1$  followed by  $t_2$ .

- Concur (Fig. 2.1b) is a component with a similar external interface: it has a passive port s and two active ports  $t_1$  and  $t_2$ . The behaviour is different though: each activation on s for this component encloses activation of  $t_1$  and  $t_2$  concurrently.

- Sync (Fig. 2.1c) is a component with three control ports: two passive ports  $s_1$  and  $s_2$  and an active port t. This component ensures enclosure of t into both  $s_1$  and  $s_2$  by the means of synchronisation between  $s_1$  and  $s_2$ . This component is dual to Concur in the sense that they form a no-op when their corresponding ports are connected.

- Call (Fig. 2.1d) is another component with three control ports: two passive ports  $s_1$  and  $s_2$  and an active port t. It differs from Sync in that instead of expecting concurrent activation of both  $s_1$  and  $s_2$  it only expects one of them to be activated at a time and encloses t into the one which happens.

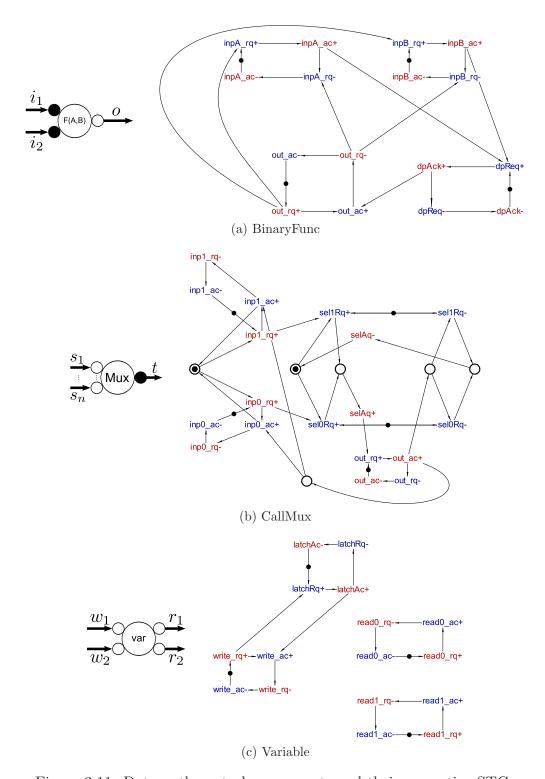

- BinaryFunc (Fig. 2.1e) is a component with three pull data ports: a passive port o and two active ports  $i_1$  and  $i_2$ . It is parametrised on width of those ports and on a function it computes. Control-wise it is similar to Concur: it encloses the concurrent activation of  $i_1$  and  $i_2$  into the activation on o.

- CallMux (Fig. 2.1f) is a component similar to Call with the difference that all of its ports are further extended to w-bit pull ports. Its behaviour is identical from the control point of view, with the additional data being received through t and sent through the activated output port.

- Variable (Fig. 2.1g) is a component with a single input data port w, called the write port and a set of passive output data ports r, called read ports. The component is parameterised on the bit width of the variable w, coinciding with the width of the data ports. It is also parameterised on the number of read ports n. The behaviour of Variable is to remember the data written with the latest activation of w and to output that data on any activation of a read port  $r_i$ . The behaviour is trivial from the control point of view: the only way the ports interact is through the data. However, there is a requirement that the write port activation does not overlap with any of the read port activations.

- While (Fig. 2.1h) is a component with a passive control port s, an active control port t and an active one-bit input data port c. Its behaviour is to enclose into the activation on s the following process: complete a handshake over c to obtain the one-bit data indicating the process activity condition; if this condition holds then activate t and repeat the operations.

Figure 2.1: Handshake components

• Case (Fig. 2.1i) is a component with a passive input data port i and a set of active control ports t. It is parameterised by a number of ports n, the size of the data transferred by i and by a function f mapping  $2^{|c|} \to n$ . The behaviour is to enclose into activation on i with the input code word d an activation of the port  $t_{f(d)}$ .

#### 2.2 Petri nets

A Petri net is a 4-tuple  $N = (P, T, W, M_N)$  where P is a finite set of places and T is a finite set of transitions with  $P \cap T = \emptyset$ ,  $W : P \times T \cup T \times P \to \mathbb{N}_0$  is the weight function, and  $M_N$  is the initial marking, where a marking is a multiset of places, i.e. a function  $P \to \mathbb{N}_0$  which assigns a number of tokens to each place. A Petri net can be considered as a bipartite graph with weighted arcs between places and transitions. If necessary, we write  $P_N$  etc. for the components of N or  $P'(P_i)$  etc. for the net  $N'(N_i)$  etc.

The *preset* of a place or transition x is denoted as  ${}^{\bullet}x$  and defined by  ${}^{\bullet}x \stackrel{\text{df}}{=} \{y \in P \cup T \mid W(y,x) > 0\}$ , the *postset* of x is denoted as  $x^{\bullet}$  and defined by  $x^{\bullet} \stackrel{\text{df}}{=} \{y \in P \cup T \mid W(x,y) > 0\}$ . These notions are extended to sets as usual. We say that there is an *arc* from each  $y \in {}^{\bullet}x$  to x.

A transition t is enabled under a marking M if  $\forall p \in {}^{\bullet}t : M(p) \geqslant W(p,t)$ , which is denoted by M[t]. An enabled transition t can fire yielding a new marking M', written as M[t]M', where M'(p) = M(p) - W(p,t) + W(t,p), for all  $p \in P$ . A transition sequence  $\sigma = t_1 \dots t_n$  is enabled under a marking M (yielding M') if

$M[t_1\rangle M_1[t_2\rangle \dots M_{n-1}[t_n\rangle M_n = M'$ , and we write  $M[\sigma\rangle$ ,  $M[\sigma\rangle M'$  resp.;  $\sigma$  is called execution of N if  $M_N[\sigma\rangle$ . The empty transition sequence  $\lambda$  is enabled under every marking. M is called reachable if a transition sequence  $\sigma$  with  $M_N[\sigma\rangle M$  exists.

N is called bounded if, for every reachable marking M and every place p,  $M(p) \leq k$  for some constant  $k \in \mathbb{N}$ ; if k = 1, N is called safe. N is bounded if and only if the set  $[M_N]$  of reachable markings is finite. In this thesis, we are mostly concerned with bounded Petri nets.

A place p is implicit if it can be deleted from the net without changing the set of executions, and so an implicit place can be removed from the net without affecting its behaviour. Unfortunately, detecting implicit places is expensive: the problem is PSPACE-complete for safe and ExpSpace-complete for general Petri nets. A place p is duplicate if there is another place p' with the same pre- and postsets whose initial marking does not exceed that of p. Duplicate places are implicit, and are cheap to detect.

An STG is a tuple  $N = (P, T, W, M_N, In, Out, \ell)$  where  $(P, T, W, M_N)$  is a Petri net and In and Out are disjoint sets of input and output signals. For  $Sig = In \cup Out$  being the set of all signals,  $\ell : T \to Sig \times \{+, -\} \cup \{\lambda\}$  is the labelling function.  $Sig \times \{+, -\}$  or short  $Sig^{\pm}$  is the set of signal transitions; its elements are denoted as  $s^+$ ,  $s^-$  resp. instead of (s, +), (s, -) resp. A plus sign denotes that a signal value changes from logical low (written as 0) to logical high (written as 1), and a minus sign denotes the opposite direction. We write  $s^{\pm}$  if it is not important or unknown which direction takes place.

An STG can contain transitions labelled with  $\lambda$ , called dummy transitions, which do not correspond to any signal change. Hiding a signal s means to change the label of all transitions labelled with  $s^{\pm}$  to  $\lambda$ . (The idea of re-synthesis approach is to hide the signals used for communication between components, which results in an STG with fewer signals that often has a simpler implementation as a circuit.) The labelling of an STG is called injective if for each pair of distinct non-dummy transitions t and t',  $\ell(t) \neq \ell(t')$ .

Examples of STGs are shown in Figs. 3.1 and 3.2. Places are drawn as circles containing a number of tokens corresponding to the initial marking. Unmarked places which have only one transition in their presets and postsets are not drawn if

<sup>&</sup>lt;sup>1</sup>Note that an implicit place can cease to be implicit if another implicit place is removed first.

the corresponding arcs have the weight 1; they are implicitly given by an arc between these two transitions (and if such a place contains tokens, they are drawn on the arc itself). Transitions are drawn simply as their labels, and the weight function is drawn as directed arcs (x,y) whenever  $W(x,y) \neq 0$  (and labelled with W(x,y) if W(x,y) > 1).

We lift the notion of enabledness to transition labels: we write  $M[\ell(t)\rangle\rangle M'$  if  $M[t\rangle M'$ . This is extended to sequences as usual – deleting  $\lambda$ -labels automatically since  $\lambda$  is the empty word; i.e.  $M[s^{\pm}\rangle\rangle M'$  means that a sequence of transitions fires, where one of them is labelled  $s^{\pm}$  while the others (if any) are  $\lambda$ -labelled. A sequence  $\nu \in (Sig^{\pm})^*$  is called a trace of a marking M if  $M[\nu\rangle\rangle$ , and a trace of N if  $M=M_N$ . The language L(N) of N is the set of all traces of N.

The reachability graph RG(N) of an STG N is an arc-labelled directed graph on the reachable markings of N with  $M_N$  as the root; there is an arc from M to M'labelled  $\ell(t)$  whenever  $M[t\rangle M'$ . For bounded Petri nets and STGs, RG(N) can be seen as a finite automaton (where all states are accepting), and L(N) is the language of this automaton. Observe that automata with accepting states only can be regarded as STGs (with the states as places, the initial state being the only marked place, etc.); hence, all definitions for STGs also apply to automata.

N is deterministic if  $\mathsf{RG}(N)$  is a deterministic automaton: it contains no  $\lambda$ labelled transitions and there are no dynamic auto-conflicts, i.e. for each reachable

marking M and each signal transition  $s^{\pm}$  there is at most one M' with  $M[s^{\pm}\rangle\rangle M'$ .

(Note that a deterministic STG can have choices between different outputs, e.g. an

STG modelling the standard arbiter is deterministic).

An STG with a set of all markings  $S_2$  is said to *simulate* another STG with a set of all markings  $S_1$  iff there exist an  $R \subseteq S_1 \times S_2$  such that  $(M_{N1}, M_{N2}) \in R$  and for any pair of markings  $(M_1, M_2) \in R$ , a label l and a marking  $M'_1, M_1[l\rangle\rangle M'_1$  implies  $M_2[l\rangle\rangle M'_2$  for some  $M'_2$ . We call R the witness of simulation. Now we can say that STGs  $N_1$  and  $N_2$  are *bisimilar* iff  $N_2$  simulates  $N_1$  with witness R and  $N_2$  simulates  $N_1$  with witness  $R^{-1}$ .

For deterministic STGs, language equivalence and bisimulation coincide, and the language can be taken as the semantics of such a specification. Unfortunately, the class of deterministic STGs is too restrictive in practice [31], e.g.:

- using dummy transitions is often convenient in manual design;

- modelling OR-causality [63] as a safe STG requires non-determinism;

- hiding internal communication (and thus introducing dummy transitions) is a crucial step in re-synthesis.

Hence, one has to deal with non-deterministic STGs as well.

One might think that if RG(N) is non-deterministic, it can be determinised (using well-known automata-theoretic methods), i.e. turned into a language-equivalent deterministic automaton with accepting states only; in particular, the resulting automaton will have no  $\lambda$ -arcs. Unfortunately, this is a bad idea, as shown in [31], where the semantics of non-deterministic STGs was developed. It is based on the concept of output-determinacy, which is a relaxation of determinism: An STG N is outputdeterminate (OD) if  $M_N[\nu] M_1$  and  $M_N[\nu] M_2$  implies for every  $x \in Out_N$  that  $M_1[x^{\pm}\rangle\rangle$  iff  $M_2[x^{\pm}\rangle\rangle$ . It turns out that OD STGs are exactly the STGs which have correct implementations according to the implementation relation introduced in [31]. Hence, non-OD STGs are ill-formed, and in particular cannot be correctly implemented as circuits. This shows that in general, the language is not a satisfactory semantics of non-deterministic STGs; in particular, synthesising the determinised reachability graph of a non-OD STG will either fail or result in an incorrect circuit. On the other hand, for the class of OD STGs [31] shows that their language is an adequate semantics, and implementation relation can be formulated purely in terms of the language. An important property of OD STGs is that in them the enabledness of an output signal is a function of the trace, i.e. given a trace  $\nu$ , the set of outputs by which  $\nu$  can be extended is uniquely determined, even though there could be multiple executions corresponding to  $\nu$ .

In the following definition of parallel composition ||, see e.g. [61], we will have to consider the distinction between input and output signals. The idea of parallel composition is that the composed systems run in parallel and synchronise on common actions – corresponding to circuits that are connected on the wires corresponding to the signals. Since a system controls its outputs, we cannot allow a signal to be an output of more than one component; input signals, on the other hand, can be shared. An output signal of a component may be an input of other components, and in any case it is an output of the composition.

The parallel composition of STGs  $N_1$  and  $N_2$  is defined if  $Out_1 \cap Out_2 = \emptyset$ . If we drop this requirement, the definition gives the synchronous product  $N_1 \times N_2$ , which is often useful. The place set of the composition is the disjoint union of the place sets of the components; therefore, we can consider markings of the composition (regarded as multisets) as the disjoint union of markings of the components, and we will also write such a marking  $M_1 \dot{\cup} M_2$  of the composition as  $(M_1, M_2)$ . To define the transitions, let  $A = (In_1 \cup Out_1) \cap (In_2 \cup Out_2)$  be the set of common signals. If e.g. s is an output of  $N_1$  and an input of  $N_2$ , then firing of  $s^{\pm}$  in  $N_1$  is 'seen' by  $N_2$ , i.e. it must be accompanied by firing of  $s^{\pm}$  in  $N_2$ . Since we do not know a priori which  $s^{\pm}$ -labelled transition of  $N_2$  will fire together with some  $s^{\pm}$ -labelled transition of  $N_1$ , we have to allow for each possible pairing. Thus, the parallel composition  $N=N_1\parallel N_2$  is obtained from the disjoint union of  $N_1$  and  $N_2$  by fusing each  $s^{\pm}$ -labelled transition  $t_1$  of  $N_1$  with each  $s^{\pm}$ -labelled transition  $t_2$  from  $N_2$  if  $s \in A$ . Such transitions are pairs and the firing  $(M_1, M_2)[(t_1, t_2)\rangle(M'_1, M'_2)$  of N corresponds to the firings  $M_i[t_i\rangle M_i'$  in  $N_i$ , i=1,2; for an example of a parallel composition, see Fig. 2.2. More generally, we have  $(M_1, M_2)[\nu] \langle (M'_1, M'_2) \text{ iff } M_i[\nu]_{N_i} \rangle M'_i \text{ for } i \in \{1, 2\}, \text{ where } \nu|_{N_i}$ denotes the projection of the trace  $\nu$  onto the signals of the STG  $N_i$ . Hence, all reachable markings of N have the form  $(M_1, M_2)$ , where  $M_i$  is a reachable marking of  $N_i$ , i = 1, 2.

Obviously, one can extend the notion of the parallel composition to a finite family (or collection)  $(C_i)_{i\in I}$  of STGs as  $\|_{i\in I}$   $C_i$ , provided that no signal is an output signal of more than one of the  $C_i$ . We will also denote the markings of such a composition by  $(M_1, \ldots, M_n)$  if  $M_i$  is a marking of  $C_i$  for  $i \in I = \{1, \ldots, n\}$ . As above,  $(M_1, M_2, \ldots, M_n)[\nu\rangle\rangle(M'_1, M'_2, \ldots, M'_n)$  iff  $M_i[\nu|_{C_i}\rangle\rangle M'_i$  for all  $i \in \{1, \ldots, n\}$ . It is easy to see that C is deterministic if all  $C_i$  are. However, this is not true for a composition of OD STGs, as the result, in general, can be non-OD in such a case.

A composition can also be ill-defined due to computation interference, see e.g. [20]. Let  $C \stackrel{\text{df}}{=} ||_{i \in I} C_i$  be a composition of STGs. It is free from computation interference (FCI) if for every trace  $\nu$  of C the following holds: if  $\nu|_{C_j}x^{\pm}$  is a trace of  $C_j$  for some output x of  $C_j$ , then  $\nu|_C x^{\pm}$  is a trace of C.

Transition contraction [61] is an important operation in circuit re-synthesis. It removes a dummy transition from an STG and combines each place of its preset with each place of its postset to 'simulate' the firing of the deleted transition, see

Figure 2.2: Parallel composition example. In the net fragment on the left hand side, signal a is an output, and in the fragment in the middle it is an input. Hence, in their parallel composition (right) it is an output. In this example, there is *computation interference*: the left component activates  $a^+$  but the middle one is not ready to receive it.

Figure 2.3: An example of a transition contraction.

Fig. 2.3. Unfortunately, transition contractions are sometimes undefined (e.g. in case the transition has a self-loop, i.e. some place occurs in both its preset and postset); moreover, even when a contraction is defined, it might change the semantics of the STG. Hence, [61] uses the notion of *secure* contractions, that preserve the semantics.

Transition contractions preserve boundedness, but in general, can turn a safe net into a non-safe one, as well as introduce weighted arcs. In practice, it is often convenient to work with safe nets, and for this [32] introduced safeness-preserving contractions, i.e. ones which guarantee that the transformed STG is safe if the initial one was. (Note that the transitions with weighted arcs must be dead in a safe Petri net, and so we can assume that the initial and all the intermediate STGs contain no

such arcs.) Also, [32] developed a sufficient structural condition for a contraction to be safeness-preserving.

From the point of view of this thesis, it is important to remark that implicit places can adversely affect the (secure) contractibility of a transition, i.e. it is possible to have a situation when a transition is not contractible (or not securely contractible), but becomes securely contractible after some implicit place is removed from the STG. As detecting implicit places is expensive, it is very desirable to reduce their number by some other means, in particular the approach proposed in this thesis reduces the number of such places in STGs obtained by parallel composition. This has a direct effect on re-synthesis: if the composed STG has fewer implicit places, more dummy transitions in it can be contracted, and so it will be easier to synthesise the result.

#### 2.3 Conditional Partial Order Graphs

A Conditional Partial Order Graph (CPOG) [39][45] is a quintuple  $H = (V, E, X, \rho, \phi)$ , where V is a finite set of vertices,  $E \subseteq V \times V$  is a set of arcs between them, and X is a finite set of operational variables. An opcode is an assignment  $(x_1, x_2, \ldots, x_{|X|}) \in \{0, 1\}^{|X|}$  of these variables; X can be assigned only those opcodes which satisfy the restriction function  $\rho$  of the graph, i.e.  $\rho(x_1, x_2, \ldots, x_{|X|}) = 1$ . Function  $\phi$  assigns a Boolean condition  $\phi(z)$  to every vertex and arc  $z \in V \cup E$  of the graph.

Figure 2.4(a) shows an example of a CPOG containing |V|=5 vertices and |E|=7 arcs. There is a single operational variable x; the restriction function is  $\rho(x)=1$ , hence both opcodes x=0 and x=1 are allowed. Vertices  $\{a,b,d\}$  have constant  $\phi=1$  conditions and are called unconditional, while vertices  $\{c,e\}$  are conditional and have conditions  $\phi(c)=x$  and  $\phi(e)=\overline{x}$  respectively. Arcs also fall into two classes: unconditional (arc  $c\to d$ ) and conditional (all the rest). As CPOGs tend to have many unconditional vertices and arcs we use a simplified notation in which conditions equal to 1 are not depicted in the graph. This is demonstrated in Figure 2.4(b).

The purpose of conditions  $\phi$  is to 'switch off' some vertices and/or arcs in the graph according to the given opcode. This makes CPOGs capable of specifying multiple partial orders or instructions (a partial order is a form of behavioural description of an instruction). Figure 2.4(c) shows a graph and its two *projections*. The

Figure 2.4: Graphical representation of CPOGs and their projections

leftmost projection is obtained by keeping in the graph only those vertices and arcs whose conditions evaluate to 1 after substitution of the operational variable x with 1. Hence, vertex e disappears, because its condition evaluates to 0:  $\phi(e) = \overline{x} = \overline{1} = 0$ . Arcs  $\{a \to d, \ a \to e, \ b \to d, \ b \to e\}$  disappear for the same reason. The rightmost projection is obtained in the same way with the only difference that variable x is set to 0. Note also that although the condition of arc  $c \to d$  evaluates to 1 (in fact it is constant 1) the arc is still excluded from the resultant graph because one of the vertices it connects (vertex c) is excluded and obviously an arc cannot appear in a graph without one of its vertices. Each of the obtained projections can be treated as a specification of a particular behavioural scenario of the modelled system. Potentially, a CPOG  $H = (V, E, X, \rho, \phi)$  can specify an exponential number of different

partial orders of events in V according to one of  $2^{|X|}$  different possible opcodes.

A CPOG is well-defined if all its projections allowed by  $\rho$  are acyclic. We consider only well-defined CPOGs in this thesis, because a cyclic projection has no natural execution semantics, in particular it is not clear which event can be executed first unless some form of a 'token' is introduced as in the Petri Net model [14].

To summarise, a CPOG is a structure to represent a set of encoded partial orders in a compact form. Synthesis and optimisation methods presented in [45] provide a way to obtain such a representation given a set of partial orders and their opcodes. For example, the CPOG in Figure 2.4(c) can be synthesised automatically from the two partial orders below it and the corresponding opcodes x = 1 and x = 0. The next section shows that a particular assignment of opcodes to the partial orders has a strong impact on the final CPOG, therefore in order to obtain the most compact CPOG representation one has to search for the best opcode assignment.

Note that partial orders is not the only formalism for formal specification of instructions. In particular, there is an alternative approach [6] based on automata, which treats every instruction as a burst-mode state machine and defines an operation of composition on them. While benefiting from a direct correspondence between flowcharts of algorithms and automata, the approach cannot model true concurrency: a set of causally independent events can only be executed as a 'burst' in the same step/clock cycle. Also, it requires explicit memory to track the current state of the automaton. We believe that partial orders are better suited for modelling instruction sets of processing units built on heterogeneous platforms, i.e. exhibiting both asynchronous and synchronous interactions [41].

#### 2.4 Agda

Agda [49] is a system serving both as a programming language and as a proof assistant simultaneously. When viewed as a programming language, it is a purely functional language with its syntax largely inspired by Haskell. Its main distinguishing features are totality (the fact that every function is defined on every possible input) and dependent typing system that allows for types to depend on the values.

#### 2.4.1 Function definitions and algebraic data types

A very common language construct in Agda is a function definition. Function definition must consist of type signature followed by its defining equations. As a simple example, consider this Boolean exclusive OR function:

```

xor: Bool \rightarrow Bool \rightarrow Bool

xor \ x \ y = x \land (\neg y) \lor y \land (\neg x)

```

Here we define a function called xor of type  $Bool \rightarrow Bool \rightarrow Bool$  with two arguments x and y defined in terms of  $\_ \land \_, \_ \lor \_$  and  $\lnot \_.$

Functions can have more than one defining equation when each equation defines the function for a particular shape, or *pattern* of arguments. This is called *pattern* matching. For example, the Boolean negation function can be defined the following way:

```

\neg_-: Bool \rightarrow Bool

\neg false = true

\neg true = false

```

A more interesting example would be a Boolean AND:

```

\_ \land \_ : Bool \rightarrow Bool \rightarrow Bool

true \land true = true

\_ \land \_ = false

```

This example demonstrates an additional feature of pattern matching: equations are ordered and the earlier ones take precedence.

In the above we used the *Bool* data type to represent Boolean values. This data type is not a built-in language construct of Agda, but can be defined using the **data** keyword:

```

data Bool : Set where

true : Bool

false : Bool

```

Here definition gives the name for the type and lists *constructors* of its values: *true* and *false*. In this case constructors have no arguments, thus corresponding

to individual values, but in general a single constructor can correspond to multiple values, as will be shown later.

#### 2.4.2 Inductive types and recursion

We often want to reason about data types with infinite number of values, such as natural numbers. To represent them we use inductive type definitions:

data  $\mathbb{N}$ : Set where

$zero : \mathbb{N}$  $suc : \mathbb{N} \to \mathbb{N}$

Here we define natural numbers as something that has two forms: it is either a zero, or a successor  $suc\ x$  where x is another natural number. These two constructors allow us to construct an arbitrary number of values of type  $\mathbb{N}$  by successive application of suc to zero: zero corresponds to 0,  $suc\ zero$  corresponds to 1,  $suc\ (suc\ zero)$  to 2, etc.

To manipulate the values of inductive data types we use recursive functions:

$$z + z : \mathbb{N} \to \mathbb{N} \to \mathbb{N}$$

$zero + y = y$

$suc x + y = suc (x + y)$

Here we define natural number addition recursively by considering the cases for the first argument: the base case of 0 + y must evaluate to y and for the recursive case (1 + x) + y must evaluate to 1 + (x + y). The Agda compiler checks that the arguments to the function become smaller on recursive calls, thus ensuring that only well-behaved (terminating) definitions are admitted.

#### 2.4.3 Indexed types and propositions

There is a close correspondence between types and logic, a phenomenon known as Curry-Howard correspondence. Specifically, types can be thought of as propositions where the type is inhabited if and only if the corresponding proposition holds true. Similarly, well-typed terms can be thought of as proofs of the corresponding propositions. Consequently, the type-checker can be used as a proof checker.

With the language features described so far we can construct types  $\top$  and  $\bot$  corresponding to true (logical tautology) and false (logical contradiction). These are not to be confused with true and false values of type Bool that can not be used as types.

```

\mathbf{data} \top : Set \mathbf{where}

tt : \top

\mathbf{data} \perp : Set \mathbf{where}

```

Here the type  $\top$  has a constructor tt, which makes it inhabited, thus corresponding to the logic value of true. The type  $\bot$  has no constructors, which makes it uninhabited, thus corresponding to false.

To construct more complex propositions Agda provides parameterised types, dependent function types and indexed inductive data families.

Type parameters are a basic way to allow for generic data types or logic operators. Consider the following example:

```

data Both \ (A:Set) \ (B:Set) : Set \ \mathbf{where}

both : A \to B \to Both \ A \ B

data Either \ (A:Set) \ (B:Set) : Set \ \mathbf{where}

left : A \to Either \ A \ B

right : B \to Either \ A \ B

```

Here,  $Both \ A \ B$  can be thought of as a type of tuples of the form  $both \ x \ y$  with x : A and y : B. At the same time, for propositions P and Q,  $Both \ P \ Q$  can be thought of as their conjunction so that the proof  $both \ p \ q$  can be constructed if and only if both p and q (proofs of P and Q) can be constructed.

Similarly, Either is playing a dual role of taking the disjoint union of its type parameters and the logical disjunction operator. Type  $Either\ P\ Q$  is inhabited if and only if types P or Q or both are inhabited.

Another way to define parameterised types is to compute them as a result of a function.

Consider some examples:

```

Not : Set \rightarrow Set

Not P = P \rightarrow \bot

```

```

IsTrue : Bool \rightarrow Set

IsTrue \ true = \top

IsTrue \ false = \bot

```

Not takes a type P and computes another type Not P, which is inhabited if and only if contradiction is derivable from P. It is useful to think of Not P as being inhabited if and only if P is not.

Is  $True\ x$  is a type that is inhabited if and only if a Boolean value x happens to equal true.

Dependent function types have the form  $(x:X) \to Y$  where x can be free in Y. This lets the type of the function result to depend on the value passed in as the argument. In the case when Y is a logical proposition, the dependent type can be thought of as universal quantification over x. Indeed, let us construct a value that can serve as a proof that for any boolean value x one of x and  $\neg x$  must be true:

```

lemma_1: (x:Bool) \rightarrow Either (IsTrue\ x) (IsTrue\ (\neg\ x))

lemma_1\ true = left\ tt

lemma_1\ false = right\ tt

```

Finally, indexed inductive type families give you more flexibility by having the constructor choose the values for type parameter instead of having to construct a type for a given parameter value:

```

data IsEven: \mathbb{N} \to Set where

zero: IsEven 0

suc: (n: \mathbb{N}) \to IsEven n \to IsEven (suc (suc n))

```

Here  $IsEven\ n$  is inhabited if and only if n is an even number.

With dependent functions it is often useful to omit some of the arguments because their values are uniquely determined by the types of the arguments that follow. To be able to do that you can mark the corresponding parameter as implicit by putting it in curly braces:

```

lemma_2: \{x: \mathbb{N}\} \to IsEven \ x \to Not \ (IsEven \ (suc \ x))

lemma_2 \ zero \ ()

lemma_2 \ (suc \ e) \ (suc \ z) = lemma_2 \ e \ z

```

```

3 - not - even : Not (IsEven (suc (suc (suc zero))))

3 - not - even = lemma_2 (suc zero)

```

Here the special syntax of () is used to indicate that we are doing a pattern matching on a given parameter with no cases to choose from. This situation allows you to complete the definition without having to give a right-hand side.

Of special importance is the equality type,  $_{-}\equiv_{-}:\{A:Set\}\rightarrow(x:A)\rightarrow(y:A)\rightarrow Set$ . We have  $x\equiv y$  inhabited if and only if x and y are the same value. It is useful for equational reasoning that is often more natural than inductive proofs.

## Chapter 3

## Improved Parallel Composition

The contents of this chapter is based on the results published previously in [3]. The chapter covers in detail the proposed modification to the labelled Petri nets parallel composition algorithm allowing for simpler resulting nets while preserving result equivalence up to bisimulation.

#### 3.1 Introduction

Parallel composition (synchronous product) of labelled Petri nets is a fundamental operation in modular hardware design. It is often used to combine models of subsystems into a model of the whole system. In particular, there is a direct correspondence between parallel composition of Signal Transition Graphs (STGs), a class of labelled Petri nets used for modelling asynchronous circuits, and connecting circuits by wires. Hence performing this operation efficiently is important in practice.

Unfortunately, the standard definition of parallel composition almost always yields a 'messy' Petri net, with many implicit places even when the component Petri nets did not have them. Some of these places are computationally cheap to remove (e.g. duplicate places – places with identical pre- and postsets). In general, however, for removing remaining implicit places one needs full-blown model checking, something infeasible if the resulting composition is large [57]. Although implicit places do not have noticeable effect on tools based on state space exploration, such as Petrify [13], the performance of tools that are based on structural methods, such as Desij [56], often deteriorates.

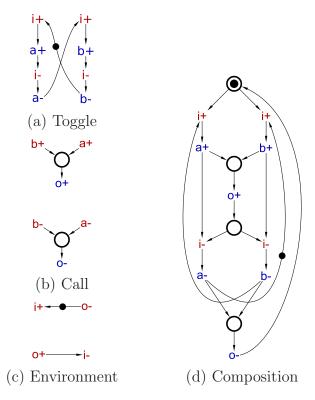

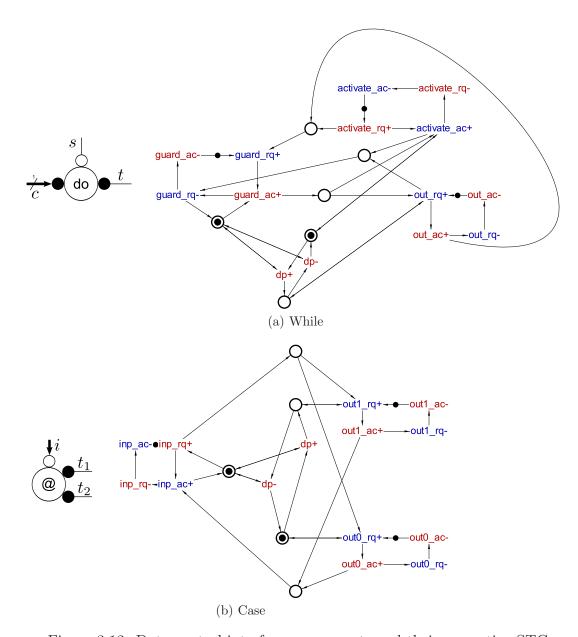

Figure 3.1: Example of standard STG composition.

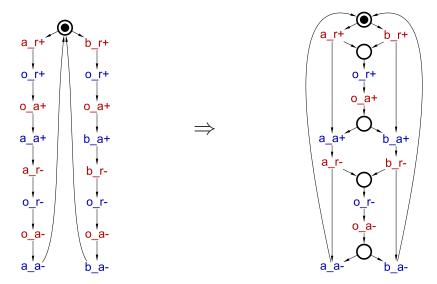

Consider the example in Fig. 3.1. It depicts an STG specifications of two components (a,b) and the specification of the environment (c). The used short-hand drawing notation for STGs is explained in Sect. 2.2. The model of the behaviour of the entire system can be obtained by constructing a parallel composition of these three STGs, as shown in part (d) of the figure. It contains a few implicit places that are not duplicate places; intuitively, they appear due to repeated causality specifications for every signal: the one coming from the component where this signal is an output, and others from the components where it is an input. Removing these places yields a much 'cleaner' STG, as shown in Fig. 3.2(d).

One operation where implicit places matter is transition contraction [61] – a crucial part of the resynthesis approach. The idea is to hide the internal communication between the components by labelling the corresponding transitions as 'dummy' (they correspond to signals a and b in our example), contract as many of these dummy transitions as possible, thus reducing the size of the STG, and resynthesise the ob-

Figure 3.2: Example of improved STG composition: the components are obtained from the corresponding ones in Fig. 3.1 by removing some places, and then the standard parallel composition is applied to these modified components.

tained STG as a circuit. The result is often smaller than the original circuit due to removal of some signals. Transition contraction is normally performed on very large STGs, such as those corresponding to the whole control path of the circuit, and so, for efficiency, it has to be a structural operation. However, such structural contractions are not always possible (see Sect. 2.2), and implicit places in the pre-set and/or post-set of a transition can prevent contracting it, even if a contraction is possible after removing these implicit places. In the example in Fig. 3.1(d), DESIJ [56] cannot contract any of the dummy transitions, even though it performs some structural tests for place redundancy. Yet, it is able to contract all the dummy transitions if the implicit places are removed, i.e. when applied to the STG in Fig. 3.2(d).

In Chapter 3 we present a new method for computing the parallel composition of labelled Petri nets that generates fewer implicit places. It uses the *freeness from* computation interference (FCI) assumption [20] stating that it is impossible that

when one component wants to produce an output it is prevented from doing so by another component not ready to receive it. Violation of the FCI assumption means that the behaviour of the composition does not correspond to that of an implied physical system. For example, an output of a circuit component cannot be physically disabled by another component that is not ready to receive this signal, and so producing this output will lead to a malfunction. However, the composition will be oblivious to the presence of the malfunction and behave as if such an output could not be produced. Hence FCI is a basic correctness requirement – whenever it is violated there is no point in computing a parallel composition since it would not characterise an intended behaviour. In practice, FCI is often guaranteed by construction, e.g. its satisaction is guaranteed for the control path of a BALSA [21] or Haste/Tangram [8, 51] specification of an asynchronous circuit. The idea of using the FCI condition is reminiscent of the method of input/output exposure in the synthesis by direct mapping described in [59] and of the correct by construction composition of Petri nets for circuit components and the environment used in the DI2PN tool [28].

The essence of the proposed method is illustrated by the example in Fig. 3.2. Before computing a parallel composition, one can remove some of the places in the components (see (a–c) in Fig. 3.2) and then compose the modified STGs. The precise conditions that allow us to remove a particular place will be stated in Sect. 3.2. At this point we shall only mention that they are structural and thus can be efficiently checked. The method guarantees that the number of places in the resulting Petri net is not larger and often much smaller (as the number of places in the composition is the total number of places in all the components), and, under the FCI assumption, the resulting behaviour is the same up to bisimularity. In the example, composing the modified components yields the STG in Fig. 3.2(d), containing no implicit places. The modified components may include unconstrained transitions and unbounded places and thus be non-implementable. Fortunately, this does not matter, as they are never used on their own, but only in composition with other components, and the resulting behaviour of the composition is guaranteed to correspond to that of the standard composition.

Resynthesis (Section 3.6) of asynchronous circuits is the intended application of the proposed method. However, we envisage that it may find a much wider

applicability since composition of labelled Petri nets is a fundamental operation and the FCI assumption is often known to hold for practically important examples.

#### 3.2 Improved parallel composition

The improved parallel composition algorithm extends the conventional one by adding a pre-processing step, where some places are removed from the components, as they are guaranteed to be implicit in the result. To identify these places, one can note that a place is required in the final composition only if under some reachable marking it can be the place that disables some transition in its postset.

For simplicity, consider the parallel composition  $C = C_1 \parallel C_2$ , whose components synchronise on a single signal s which is an output of  $C_1$  and an input of  $C_2$ . Let  $(M_1, M_2)$  be a reachable marking of C, where  $M_1$  and  $M_2$  are some reachable markings of  $C_1$  and  $C_2$ , respectively. Furthermore, suppose that  $M_1$  enables, say,  $s^+$  in  $C_1$ , where s is an output. Now, if  $M_2$  does not enable  $s^+$  in  $C_2$ , where s is an input, then there is computation interference. Therefore, if the FCI assumption holds,  $M_2$  has to enable  $s^+$  in  $C_2$ , i.e. whenever  $s^+$  is enabled in  $C_1$ , it is also enabled in  $C_2$ . In other words, the firing of  $s^+$  in C is fully controlled by  $C_1$ , and so the constraints on firing of s that are present in  $C_2$  can be ignored. This means that the places in the preset of an  $s^+$ -labelled transition in  $C_2$  will be implicit in the composition (subject to some technical conditions formulated below), and so can be removed before the composition is performed.

The above is true for the simple case of STGs with injective labelling and no dummies. However, the general picture is more complicated. In case of non-injective labelling, there can be multiple transitions corresponding to the same input signal transition, and the FCI assumption only guarantees the enabledness of one of them. Hence, some 'memory' (in the form of places) is required to trace which of these transitions has to be fired, which prohibits the removal of places from their presets. Furthermore, if the STG contains dummies, removing places from their postsets introduces some undesirable effects explained later. These considerations lead to the following conditions of applicability of the proposed optimisation.

**Proposition 1.** <sup>1</sup> Let  $C \stackrel{\text{df}}{=} ||_{i \in I} C_i$  be a composition of STGs that satisfies the FCI

<sup>&</sup>lt;sup>1</sup>Note that in our previous work [3] we claimed a stronger equivalence (viz. isomorphism of

Figure 3.3: Equivalence preserved by place removal in improved parallel composition.

property and yields an output-determinate STG, and, for each  $i \in I$ ,  $C'_i$  be the STG obtained from  $C_i$  by deleting all places p such that:

- 1. each transition  $t \in p^{\bullet}$  is labelled with a signal, say s, and:

- a) s is an input;

- b) there is an STG  $C_i$  for which s is an output;

- c) there are at most one  $s^+$  and at most one  $s^-$ -labelled transition in  $C_i$ ;

- 2. •p does not contain dummy transitions.

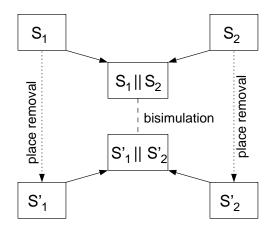

Then  $C' \stackrel{\text{df}}{=} ||_{i \in I} C'_i$  and C are bisimilar.

The proposition can be depicted schematically by a diagram in Fig. 3.3. Here the boxes named  $S_1$  and  $S_2$  represent the original STGs,  $S'_1$  and  $S'_2$  are represent STGs obtained from  $S_1$  and  $S_2$  by removing places according to the rules detailed above, and  $S_1 \parallel S_2$  and  $S'_1 \parallel S'_2$  represent  $S_1$  composed with  $S_2$  and  $S'_1$  composed with  $S'_2$  respectively. We use a dashed line to signify the bisimulation relation between  $S_1 \parallel S_2$  and  $S'_1 \parallel S'_2$ .

The conditions 1a and 1b are intrinsic to the proposed method, and essentially state that due to the FCI assumption, firing of an input signal in a component can

reachability graphs), but there was a subtle problem in the proof discovered by Walter Vogler from University of Augsburg, who found a counter-example. Here an updated version of the theorem is presented that avoids the discovered problem.

Figure 3.4: Example of an STG where removal of places in the postset of dummy transitions results in a wrong behaviour.

be controlled from the outside (viz. by the component controlling the corresponding output — whose existence is ensured by 1b), and so the component itself can get rid of the places controlling it.

The conditions 1c and 2 are technical restrictions on application of our method. If condition 1c is violated, there are several transitions that have the same label, say  $s^+$  (where s is an input) in the component. When the corresponding output  $s^+$  is produced by some other component, only one of these transitions should fire to match it — but to know which one, the component needs to control their firing, and so the places in their presets cannot be removed.

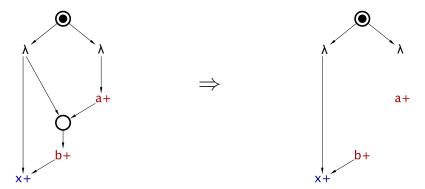

The necessity of condition 2 is illustrated by Fig. 3.4. Intuitively, the original STG on the left either receives  $a^+$  followed by  $b^+$  without outputting anything, or receives  $b^+$  and produces  $x^+$  in response. However, if the places in front of  $a^+$  and  $b^+$  are removed (which would be possible without condition 2), as shown on the right, then it might produce the unexpected  $x^+$  after the trace  $a^+b^+$ . Intuitively, in the initial STG firing of  $a^+$  acts as an evidence that the dummy transition in the right branch has fired, while in the modified one the postset of this dummy transition has been removed, and so it is not possible anymore to guarantee that it has fired when  $a^+$  fires.

Figure 3.5: Example of enforcing injective labelling in an STG.

#### 3.3 Discussion

In practice, when performing the parallel composition, one would like as few implicit places as possible in the result, and so it would be desirable to weaken the conditions in Prop. 1, so that as many places as possible are removed. As the conditions 1a and 1b are intrinsic, it is unlikely that they can be relaxed. However, the technical conditions 1c and 2 can be dealt with — by ensuring that the components always satisfy them. Indeed, as mentioned in Sect. 2.2, for output-determinate STGs the language is the semantics, and so one often can remove dummy transitions and enforce injective labelling without changing the language, e.g. using the PETRIFY tool [13]; this will ensure that conditions 1c and 2 hold. An example of such a transformation for the BALSA standard component Call is shown in Fig. 3.5. This operation is performed on (small) components rather than the (large) composition, and so is usually cheap. Moreover, in some applications, in particular circuit resynthesis, the components are taken from a fixed library of component types, and so the transformation can be performed only once for each component type, and subsequently incur no runtime penalty at all.

#### 3.4 Proof of Proposition 1

We begin by defining a relation R between markings of C and C', which we will show to be a bisimulation. We say that  $(M, M') \in R$  iff M is reachable in C and M(p) = M'(p) for each  $p \in P'$ . Note that M(p) is well-defined, as  $P' \subseteq P$  because C' was obtained from C by removing places. Also note that for any given reachable marking M there is exactly one M' such that  $(M, M') \in R$ , obtained by restricting the domain of M, so R is a function and we employ the notation M' = R(M) to use it as such.

Now we need to prove that the introduced relation R is indeed bisimulation. We start by proving that C' simulates C with R. For that, we first need to show  $M'_N = R(M_N)$ . That follows from both parallel composition and place removal preserving initial markings of individual places. Now given a reachable marking  $M^1$  with an enabled transition  $M^1[l\rangle\rangle M^2$  we must show that  $R(M^1)[l\rangle\rangle R(M^2)$ . To prove that we note that any transition enabled in  $M^1$  must also be enabled in  $R(M^1)$  because the enabledness condition gets weakened with removal of places. Using that fact we show that whichever transition t labelled t was enabled to allow  $M^1[t\rangle M^2$  it is also enabled in  $R(M^1)$ . The marking after firing must coincide with  $R(M^2)$  because the arcs to existing places and their weights are preserved by place removal. This shows  $R(M^1)[t]\rangle R(M^2)$  and concludes the proof that C' simulates C.

In the second part of the proof we show that C simulates C' with  $R^{-1}$ . Here, given  $R(M^1)[l\rangle M'^2$  we need to show that there exists an  $M^2$  such that  $M^1[l\rangle M^2$  and  $M'^2 = R(M^2)$ . Again, we note that there must be a transition t' labelled l such that  $R(M^1)[t'\rangle M'^2$ . If the corresponding transition t is enabled  $M^1[t\rangle M^2$  then the proof is complete since we already showed that  $M'^2$  must be equal to  $R(M^2)$ . For the sake of contradiction, suppose t is not enabled in marking  $M^1$ . Then there is necessarily one of the deleted places p in t in some of the component STGs  $C_i$ , and the number of tokens in this place at marking  $M^1$  is smaller than the weight of the arc (p,t) in  $C_i$  (\*). Since by condition 1a  $p^{\bullet}$  can contain only input transitions, t must be labelled by  $s^{\pm}$ , where s is an input signal of  $C_i$ ; wlog., we assume that the label is  $s^+$ . By condition 1b there is also a component STG  $C_j$  where s is an output signal.

Let  $\sigma$  be an execution of C terminating at marking  $M^1$ , and  $\nu$  be the trace