µSystems Research Group

School of Electrical and Electronic Engineering

## **Design of Reconfigurable Dataflow Processors**

Alessandro de Gennaro

Technical Report Series NCL-EEE-MICRO-TR-2014-193

October 2014

Contact: a.de-gennaro@newcastle.ac.uk

Supported by EPSRC Impact Acceleration Award EP/K503885/1 (project "Dataflow Computation a la Carte").

NCL-EEE-MICRO-TR-2014-193 Copyright © 2014 Newcastle University

μSystems Research Group School of Electrical and Electronic Engineering Merz Court Newcastle University Newcastle upon Tyne, NE1 7RU, UK

http://async.org.uk/

## POLITECNICO DI TORINO

Facoltà di Ingegneria Master's Degree in Computer Engineering

Graduation Thesis

## Design of Reconfigurable Dataflow Processors

Advisor: Prof. Luciano Lavagno

**Co-advisor:** Dr. Andrey Mokhov Candidate: Alessandro de Gennaro

October 24, 2014

A mia nonna Pina, alla quale avevo promesso che mi sarei laureato.

## Contents

|          | Abs  | stract                                                   |   |   | XI  |

|----------|------|----------------------------------------------------------|---|---|-----|

|          | Ack  | knowledgements                                           |   |   | XII |

| 1        | Intr | roduction                                                |   |   | 1   |

| <b>2</b> | Bac  | ekground                                                 |   |   | 6   |

|          | 2.1  | Conditional partial order graph model                    |   |   | 6   |

|          |      | 2.1.1 A factorial issue in the number of solutions       | • |   | 8   |

|          |      | 2.1.2 Examples considered                                |   |   | 12  |

|          |      | 2.1.3 Boolean equations extraction for each CPOG element |   |   | 14  |

|          |      | 2.1.4 Boolean equations extraction for the model         |   |   | 15  |

|          | 2.2  | Dataflow computing                                       |   |   | 19  |

|          |      | 2.2.1 Dataflow theory                                    |   |   | 20  |

| 3        | Asy  | nchronous dataflow pipelines design                      |   |   | 24  |

|          | 3.1  | Pipelining introduction                                  |   |   | 25  |

|          | 3.2  | Asynchronous pipelining                                  |   |   | 28  |

|          |      | 3.2.1 4-phase dual-rail protocol                         |   |   | 29  |

|          |      | 3.2.2 C-element                                          |   |   | 31  |

|          |      | 3.2.3 Pipeline implementation                            |   |   | 33  |

|          | 3.3  | Combinatorial circuitry                                  |   | • | 36  |

| 4        | Dat  | taflow graphs composition                                |   |   | 40  |

|          | 4.1  | Decoded circuit area evaluation                          |   |   | 41  |

|          |      | 4.1.1 Gate library used                                  |   |   | 41  |

|          |      | 4.1.2 ABC tool usage                                     |   |   | 41  |

|          | 4.2  | Cost function                                            |   |   | 43  |

|          |      | 4.2.1 Correlation between Partial Orders and op-codes    |   |   | 43  |

|          |      | 4.2.2 Cost function results and statistics               |   |   | 44  |

|          | 4.3  | Graph Isomorphism Similarity                             |   |   | 48  |

|          |               | 4.3.1   | Graph isomorphism recognition                                                                                                  | 49  |

|----------|---------------|---------|--------------------------------------------------------------------------------------------------------------------------------|-----|

|          |               | 4.3.2   | Similarities between graph isomorphism and encoding process                                                                    | 50  |

|          |               | 4.3.3   | Conclusions                                                                                                                    | 51  |

|          | 4.4           | Encod   | ling Generation                                                                                                                | 51  |

|          |               | 4.4.1   | Recursive encoding generation                                                                                                  | 52  |

|          |               | 4.4.2   | Random encoding generation                                                                                                     | 54  |

|          |               | 4.4.3   | Optimal encoding generation                                                                                                    | 56  |

|          |               | 4.4.4   | Tuning encodings by means of simulated annealing                                                                               | 57  |

|          |               | 4.4.5   | Generation outcome                                                                                                             | 63  |

| <b>5</b> | Wo            | rkcraft | integration and custom op-codes                                                                                                | 64  |

|          | 5.1           | Custo   | m op-codes $\ldots$                           | 65  |

|          | 5.2           | Worke   | eraft integration                                                                                                              | 67  |

|          |               | 5.2.1   | Front-end and back-end connection                                                                                              | 67  |

|          |               | 5.2.2   | Graphical User Interface                                                                                                       | 69  |

| 6        | $\mathbf{CP}$ | OG ap   | plied to ISA development                                                                                                       | 72  |

|          | 6.1           |         | $Cortex M0+\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots$ | 73  |

|          | 6.2           | ISA de  | esigning technique                                                                                                             | 73  |

|          | 6.3           | Armve   | 6-M representation via CPOG                                                                                                    | 75  |

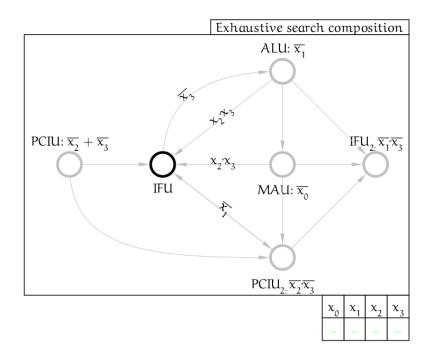

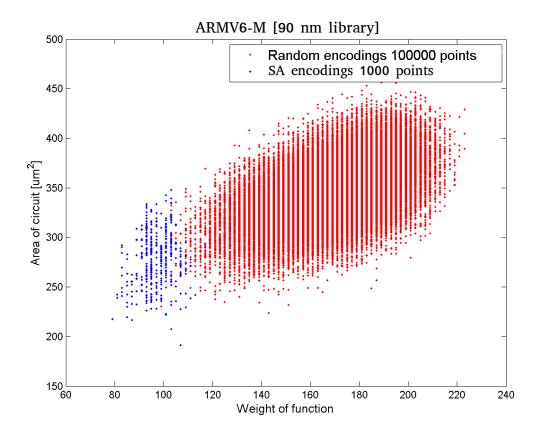

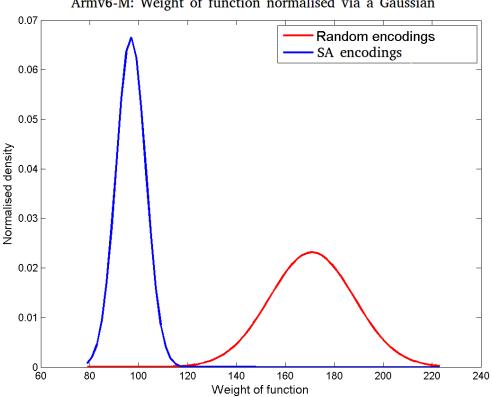

|          | 6.4           | Comp    | osition results                                                                                                                | 77  |

|          |               | 6.4.1   | Final considerations                                                                                                           | 84  |

| 7        | Self          | E-timed | l reconfigurable dataflow processors design                                                                                    | 88  |

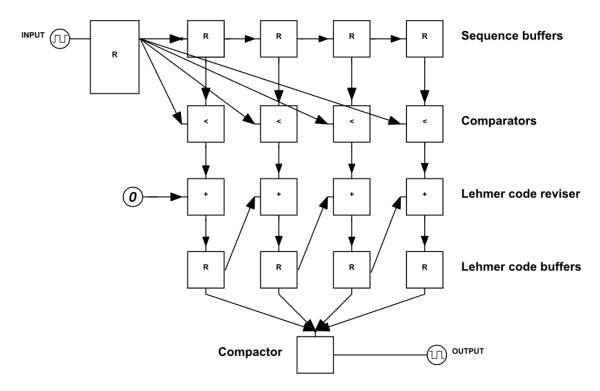

|          | 7.1           |         | al pattern encoding for ordinal analysis                                                                                       |     |

|          | 7.2           | Contro  | ol-Unit design                                                                                                                 | 92  |

|          | 7.3           | Datap   | ath design                                                                                                                     | 97  |

| 8        | Cor           | nclusio |                                                                                                                                | 109 |

|          | 8.1           |         | contributions                                                                                                                  |     |

|          | 8.2           | Future  | e research directions                                                                                                          | 111 |

| Α        | Par           | tial or | ders modelling Armv6-M                                                                                                         | 114 |

| Bi       | bliog         | graphy  |                                                                                                                                | 126 |

# List of Figures

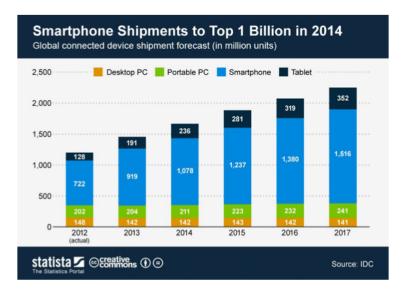

| 1.1  | Mobile devices growth along years, research by <i>IDC</i> [2]                                                         | 2             |

|------|-----------------------------------------------------------------------------------------------------------------------|---------------|

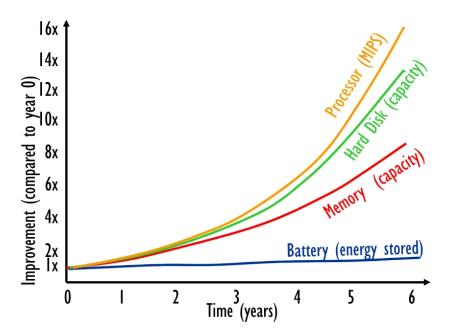

| 1.2  | CPU-Batteries improvements throughout years, Figure taken from                                                        | 0             |

| 19   | [11] p.7                                                                                                              | $\frac{2}{3}$ |

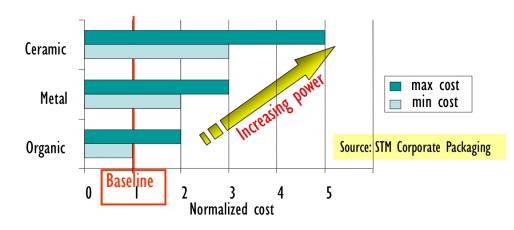

| 1.3  | Cost of chip package vs rower consumption, righte from [11] p.12.                                                     | 5             |

| 2.1  | Graphical representation of a <i>CPOG</i>                                                                             | 7             |

| 2.2  | <i>CPOG</i> projections: $\mathcal{H} _{\mathcal{X}=1}$ on the right, $\mathcal{H} _{\mathcal{X}=0}$ on the left side | 8             |

| 2.3  | Op-code ensemble of length 3                                                                                          | 9             |

| 2.4  | Two possible encodings for CPOG composed by 5 Partial Orders with                                                     |               |

|      | 3-bits opcodes                                                                                                        | 9             |

| 2.5  | Encoding for CPOG composed by 5 Partial Orders with 3-bits op-                                                        |               |

|      | codes exploiting don't care.                                                                                          | 10            |

| 2.6  | Simple $CPOG$ models four basic operations of a $ALU$ ,([3], Figure 7.9).                                             | 12            |

| 2.7  | 8 instruction classes model                                                                                           | 13            |

| 2.8  | Partial Order Graphs example ([3], Figure 2.5)                                                                        | 14            |

| 2.9  | Conditional Partial Order Graph with 4 instruction classes                                                            | 17            |

| 2.10 | CPOG-based microcontroller with acknowledgements/requests inter-                                                      |               |

|      | face, taken from [3], Figure 7.4.                                                                                     | 18            |

| 2.11 | Particular of Maxeler Technologies transparencies, Slide N. 5 "Intro-                                                 |               |

|      | duction of Dataflow computing" [30]                                                                                   | 20            |

|      | Static Dataflow Network example                                                                                       | 22            |

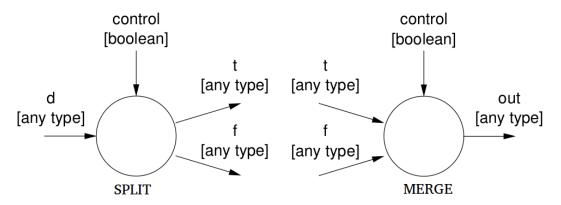

| 2.13 | Split and merge structures. ([31], Figures $6.12 - 6.13$ )                                                            | 22            |

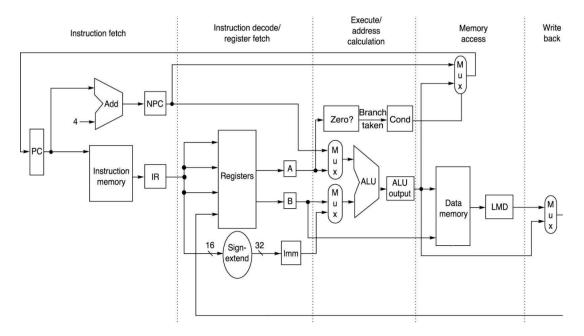

| 3.1  | General structure of a RISC-based processor. ([32], P. 13)                                                            | 25            |

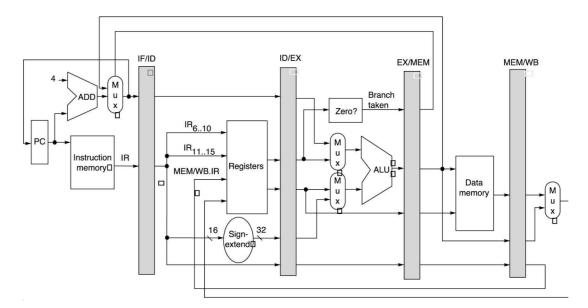

| 3.2  | Pipeline version of a RISC-based processor. ([32], P. 16)                                                             | 26            |

| 3.3  | Pipelined execution example. ([32], P. 26 modified)                                                                   | 27            |

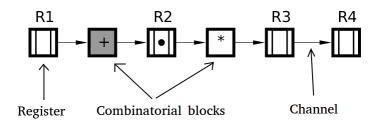

| 3.4  | Dataflow asynchronous pipeline example                                                                                | 28            |

| 3.5  | Typical handshaking protocol structure                                                                                | 29            |

| 3.6  | 4-phase asynchronous protocol behaviour                                                                               | 30            |

| 3.7  | Bundled-data protocol model                                                                                           | 31            |

| 3.8  | 4-phase asynchronous dual-rail protocol model                                                                         | 32            |

| 3.9  | Schematic of 2 inputs c-element                                                                                       | 32            |

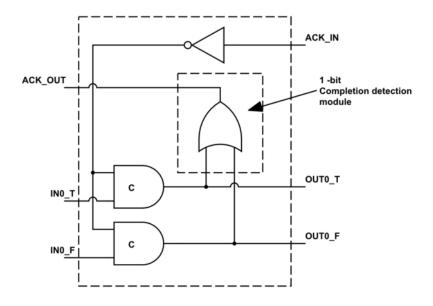

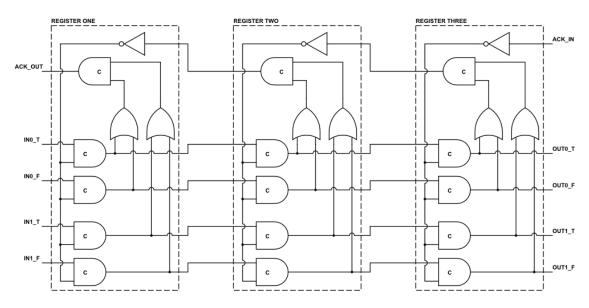

|      | 1 bit asycnhronous register                                                                      | 34 |

|------|--------------------------------------------------------------------------------------------------|----|

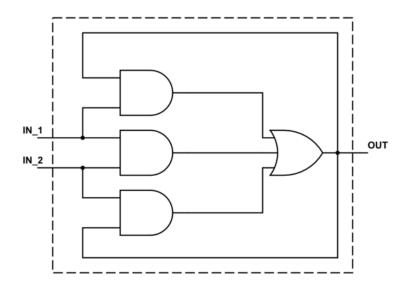

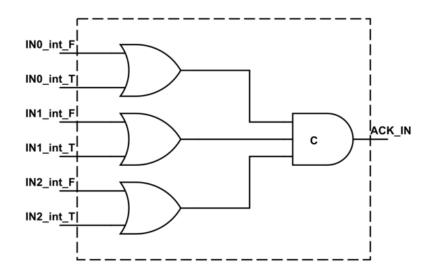

|      | 3 bits completion detection module                                                               | 35 |

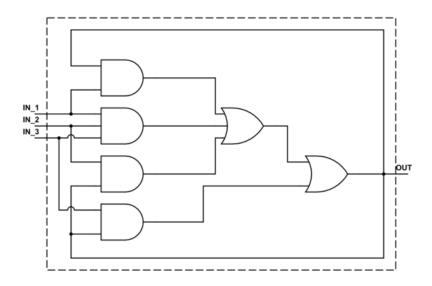

|      | 3 bits C-element implementation                                                                  | 35 |

|      | 2 bits - 3 stages asynchronous pipeline example                                                  | 36 |

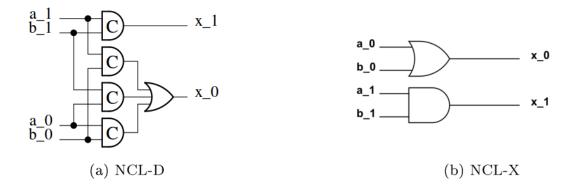

| 3.14 | Dual-rail AND gate implementations. ([38], Figure 2 modified)                                    | 37 |

| 4.1  | CPOG with four instruction classes analysed                                                      | 44 |

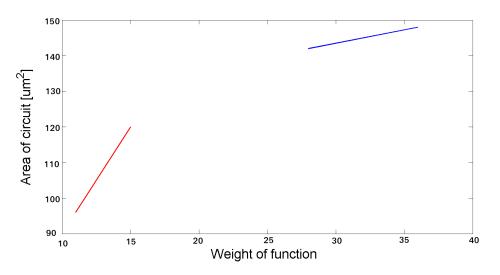

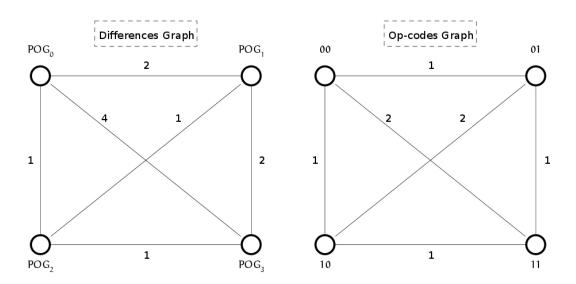

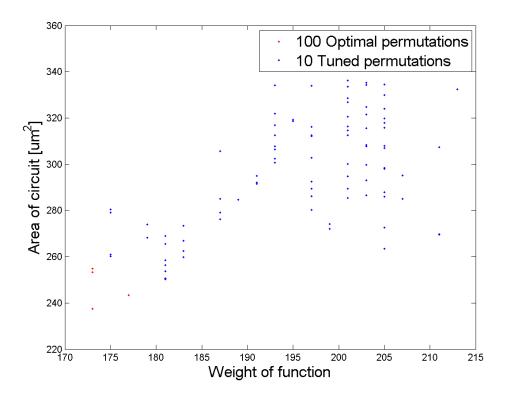

| 4.2  | Area- $\mathcal{F}$ plot of $CPOG$ on Figures 2.9 (Blue) and 4.1 (Red)                           | 45 |

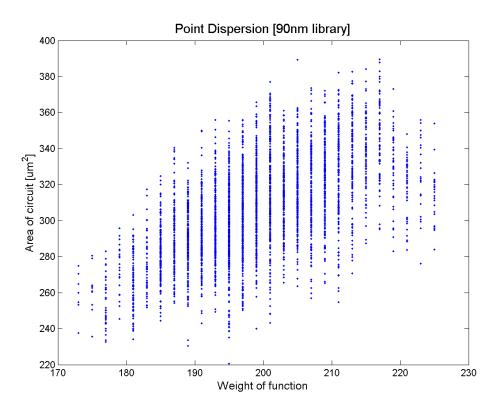

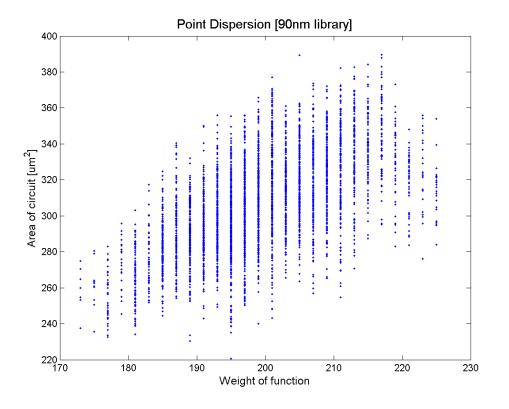

| 4.3  | Point dispersion of <i>CPOG</i> on Figure 2.7                                                    | 46 |

| 4.4  | Line interpolation of <i>CPOG</i> on Figure 2.7                                                  | 47 |

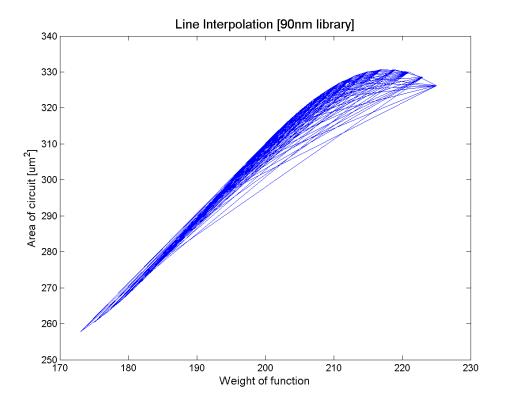

| 4.5  | Example of two isomorphic graphs.                                                                | 49 |

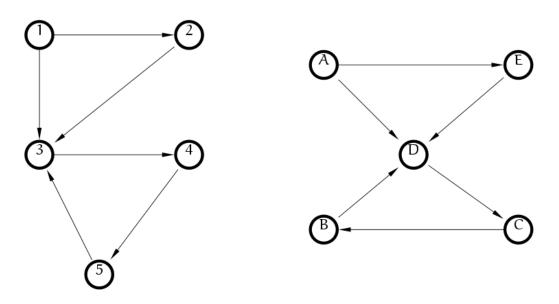

| 4.6  | On the left side an instance of Difference Graph, on the right side an                           |    |

|      | Op-codes graph is depicted.                                                                      | 51 |

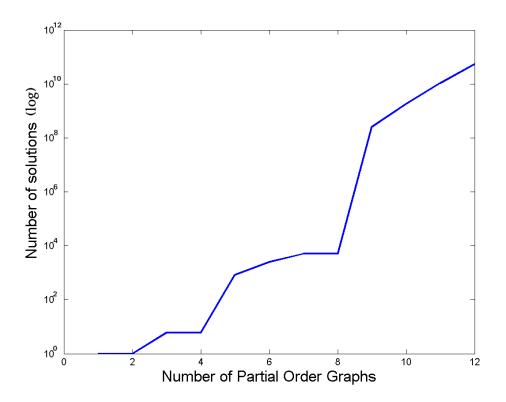

| 4.7  | Number of solutions increments into <i>Recursive Generation</i> technique.                       | 53 |

| 4.8  | Recursive encoding generation applied to <i>CPOG</i> on Figure 2.7                               | 55 |

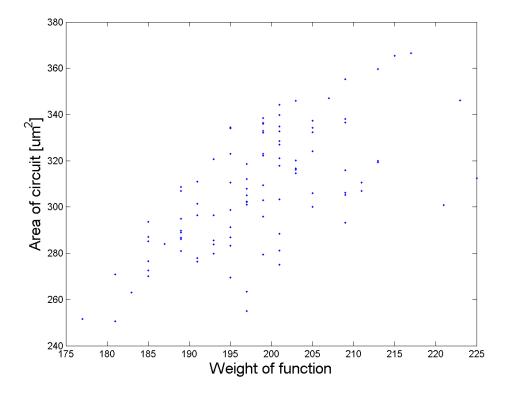

| 4.9  | Random encoding generation applied to <i>CPOG</i> on Figure 2.7                                  | 57 |

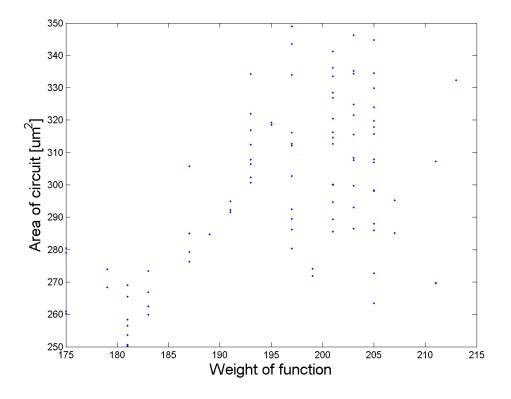

| 4.10 | Optimal encoding generation applied to <i>CPOG</i> on Figure 2.7                                 | 58 |

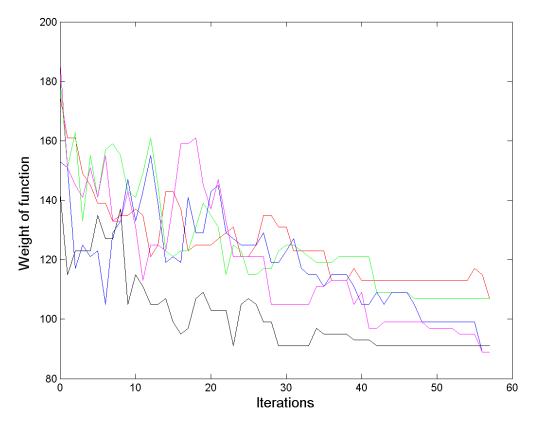

| 4.11 | Function fluctuations using Simulated annealing optimisation tech-                               |    |

|      | nique on Arm Cortex M0+ model.                                                                   | 60 |

| 4.12 | Optimised encodings, applied to <i>CPOG</i> in Figure 2.7                                        | 61 |

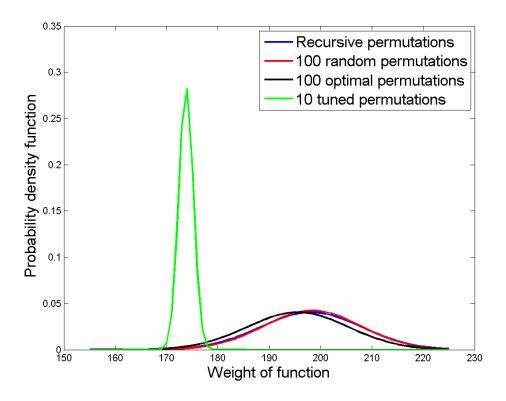

| 4.13 | Generation encoding algorithms comparison                                                        | 62 |

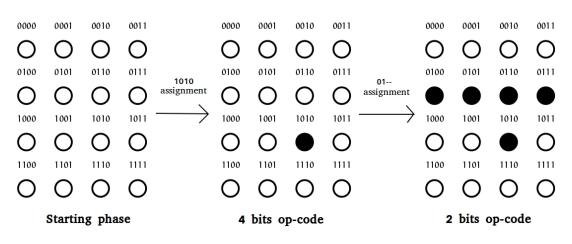

| 5.1  | Op-codes assignment example                                                                      | 66 |

| 5.2  | Graphical user interface of <i>SCENCO</i>                                                        | 70 |

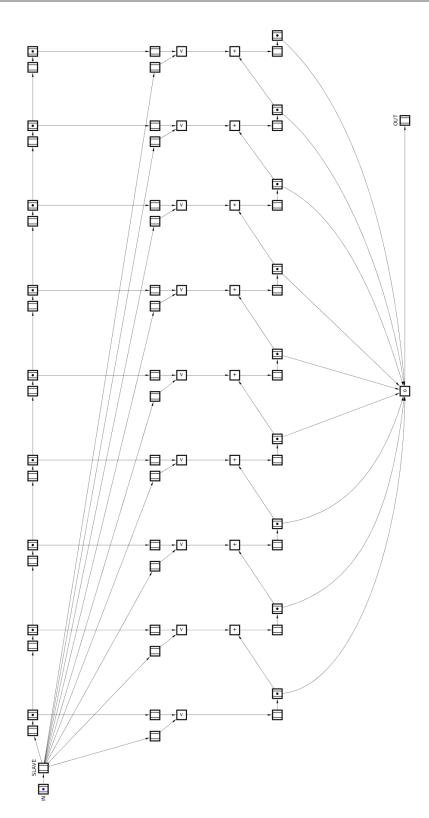

| 6.1  | ARMv6-M Instruction Set Architecture modelled via $CPOG$                                         | 76 |

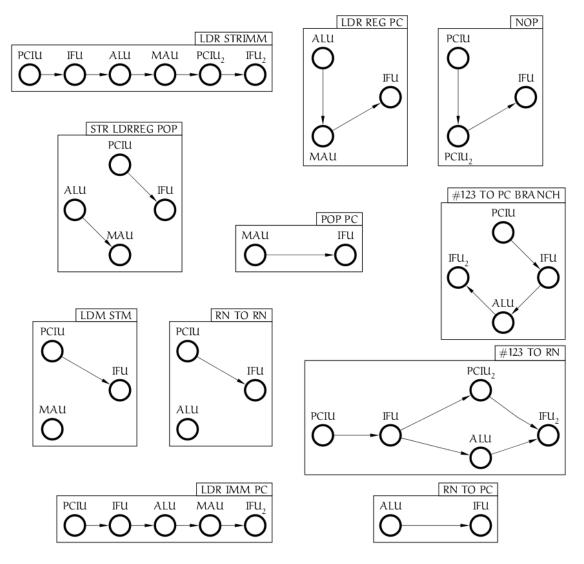

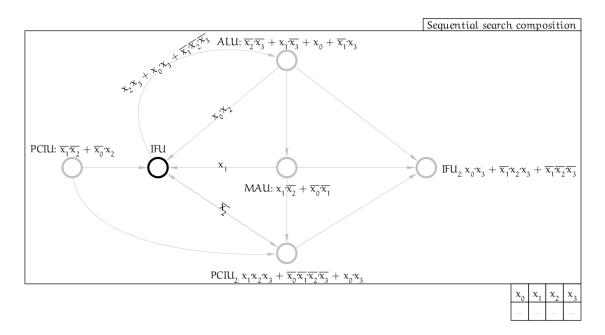

| 6.2  | Sequential encoding CPOG composition                                                             | 79 |

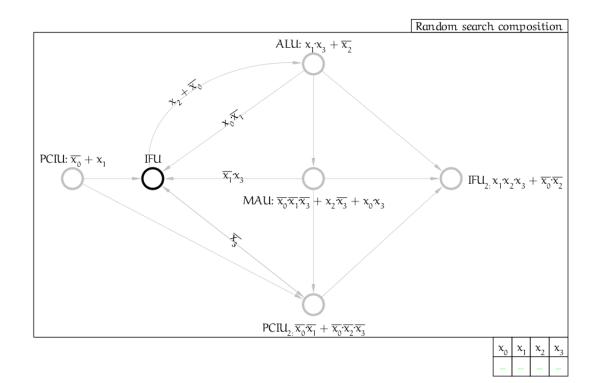

| 6.3  | Random encoding CPOG composition                                                                 | 80 |

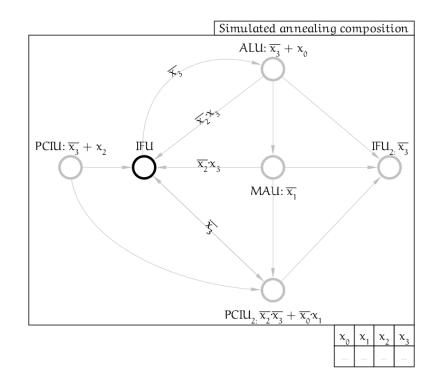

| 6.4  | Simulated annealing encoding CPOG composition                                                    | 82 |

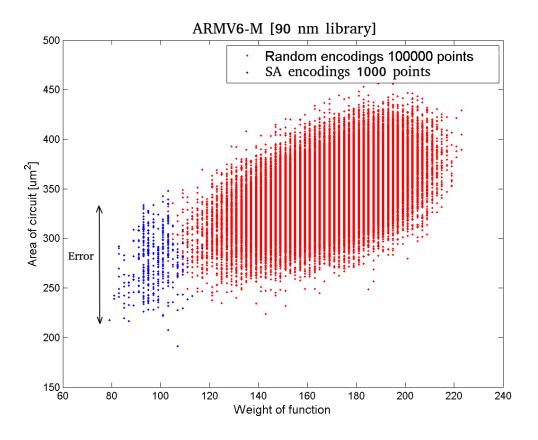

| 6.5  | Exhaustive search encoding CPOG composition                                                      | 83 |

| 6.6  | Comparison between Simulated Annealing and Random search tech-                                   |    |

|      | niques                                                                                           | 85 |

| 6.7  | Comparison between Simulated Annealing and Random search tech-                                   |    |

|      | nique (encodings weight) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 86 |

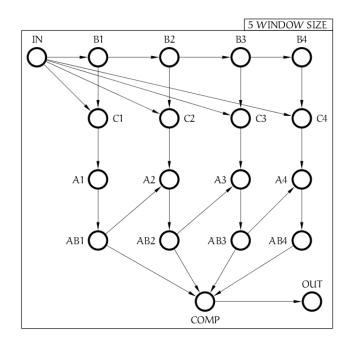

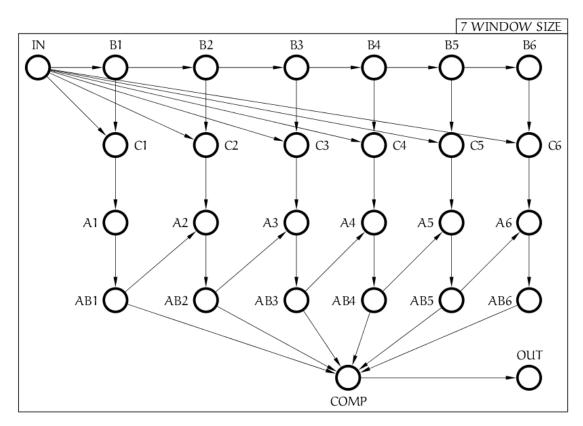

| 7.1  | Ordinal pattern encoding algorithm for subsequences of length 5,                                 |    |

|      | hardware structure inspired by [41]                                                              | 92 |

| 7.2  | Ordinal pattern model for subsequences of length 5                                               | 93 |

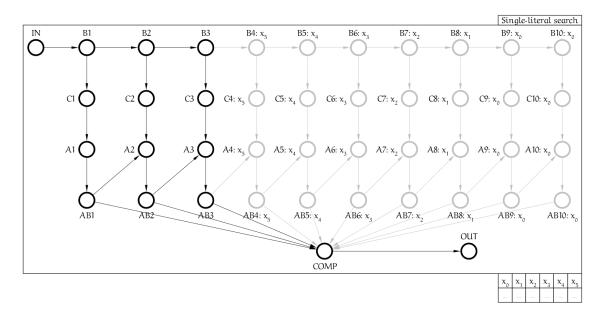

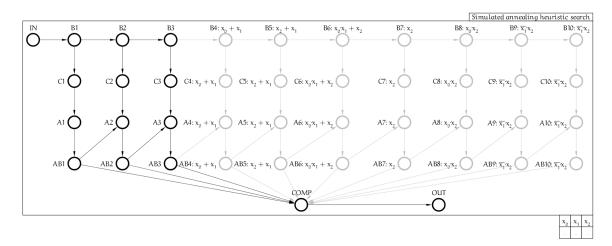

| 7.3  | Ordinal pattern model for subsequences of length 7                                               | 94 |

| 7.4  | Compositional graph with Single-literal search of ordinal pattern op-                            |    |

|      | eration structure.                                                                               | 95 |

| 7.5  | Compositional graph with Simulated annealing heuristic search of                                                                                            |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | ordinal pattern operation structure                                                                                                                         |

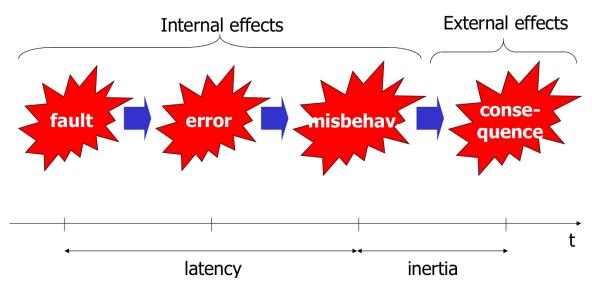

| 7.6  | From fault to external damage( $[45]$ , p.79)                                                                                                               |

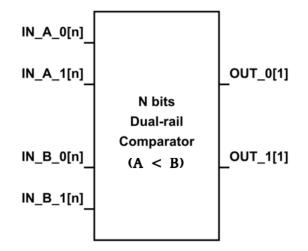

| 7.7  | N bit dual rail comparator from an external point of view 100                                                                                               |

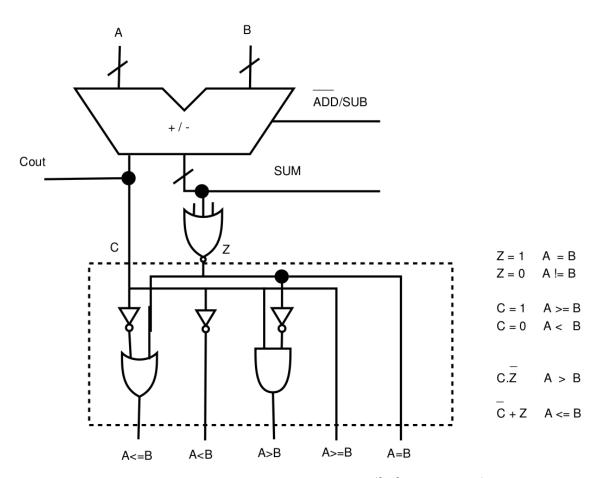

| 7.8  | Schematic of a comparator.([46], Figure 4.16)                                                                                                               |

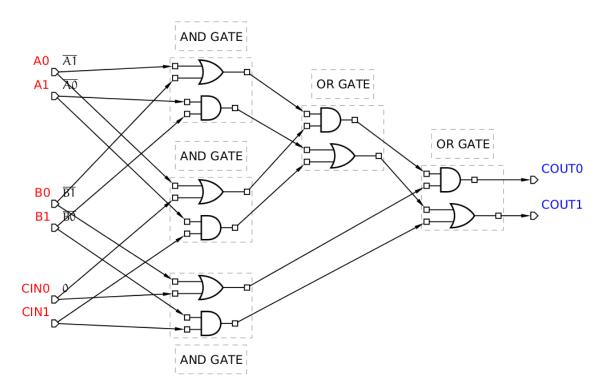

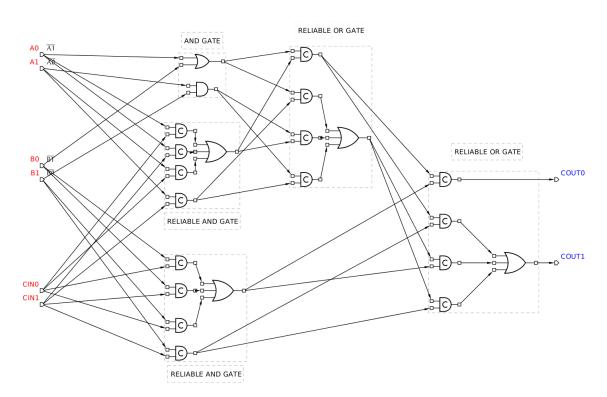

| 7.9  | 1-bit dual-rail carry adder implemented with NCL-X gates 102                                                                                                |

| 7.10 | 1-bit dual-rail carry adder implemented with $NCL\text{-}D$ and $NCL\text{-}X$ gates 103                                                                    |

| 7.11 | Schematic                                                                                                                                                   |

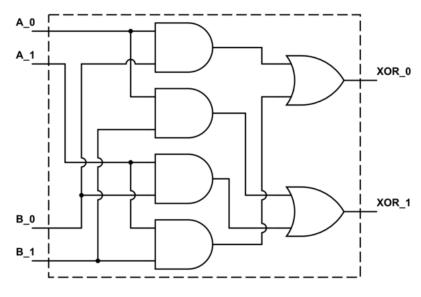

| 7.12 | NCL-X dual-rail XOR gate                                                                                                                                    |

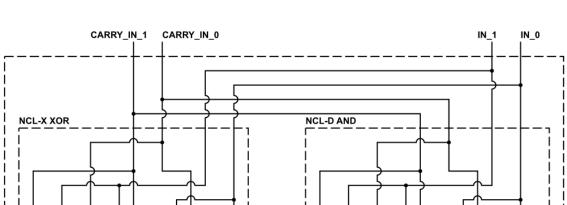

| 7.13 | 1-bit reliable dual-rail semi-adder implementation                                                                                                          |

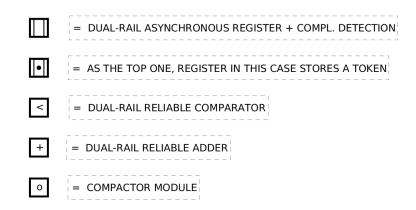

| 7.14 | Legend of blocks present on Figure 7.15                                                                                                                     |

| 7.15 | Ordinal pattern encoding hardware structure design under Workcraft. 108                                                                                     |

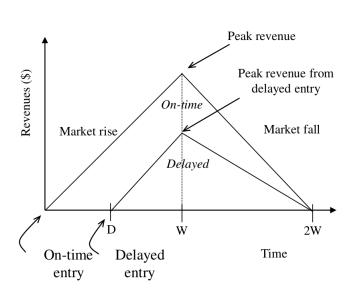

| 8.1  | Losses due to delayed market entry([47], p.13)                                                                                                              |

| 8.2  | Error showed due to cost function used. $\dots \dots \dots$ |

| 0.2  |                                                                                                                                                             |

| A.1  | Memory instructions (Immediate offset addressing mode)                                                                                                      |

| A.2  | Memory instructions (Register offset addressing mode)                                                                                                       |

| A.3  | Memory instructions (Bunch registers transferring)                                                                                                          |

| A.4  | Load instruction Immediate addressing on PC                                                                                                                 |

| A.5  | Load instruction register addressing on PC                                                                                                                  |

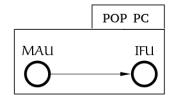

| A.6  | POP instruction                                                                                                                                             |

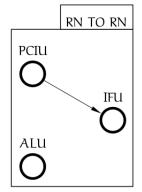

| A.7  | Arithmetical, logic and data copy instructions (register addressing) . 121                                                                                  |

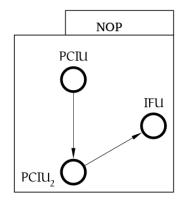

| A.8  | Nop instruction                                                                                                                                             |

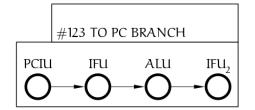

| A.9  | Unconditional branch instruction                                                                                                                            |

| A.10 | Instructions with immediate addressing mode                                                                                                                 |

| A.11 | Branch instructions                                                                                                                                         |

|      |                                                                                                                                                             |

# List of Tables

| $2.1 \\ 2.2$      | Example of Boolean conditions assignment of graph on Figure 2.8 $\dots$ Boolean equations for each element for <i>CPOG</i> on Figure 2.9 $\dots$ |    |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1<br>3.2<br>3.3 | Communication on dual rail protocol                                                                                                              | 33 |

| $4.1 \\ 4.2$      | Comparison between encodings generations applied to $CPOG$ on Fig-                                                                               |    |

| 61                | ure 2.7.    Controller size comparison for Armv6-M ISA model.                                                                                    |    |

|                   | Truth table.                                                                                                                                     |    |

### Abstract

This work presents a new method for designing reconfigurable dataflow hardware structures efficiently. The design-flow my research is based on is reliant on a model developed at Newcastle University named *Conditional Partial Order Graph*, also called *CPOG* [50], [3]. It is a representation which is finding many applications on the overall *VLSI* industry, because of its capability to capture different behaviours of a system in an extremely compact way.

Additionally, this dissertation presents a new heuristic algorithm, able to fill in the gap in this model at the controller synthesis phase. It is needed either for managing the reconfigurability of the system under design, and for handling request/acknowledgement signals for the sequentiality of the operations to be executed, in particular for self-timed structures. The new heuristic is able to seek an optimal op-code association (in terms of area consumption) for each different graph over a custom number of bits. The module comes up with the synthesis phase is used to control the events which may happen, likewise a control unit based structure.

The whole encoding tool has been integrated in Workcraft [54], which is a software that supports different models, both for synchronous and asynchronous devices design. One of the aim of this project indeed, was expanding such tool under CPOGplugin, and developing a Graphical User Interface to be used by designers during the former phases of a project. Furthermore, the whole design-flow has been applied to a real application in order to demonstrate the easiness through which a completely reconfigurable structure might be designed easily from scratch.

The number of applications this technique might be potentially applied for is huge. Let us think to how many systems could be splitted into events: the decoding part of *Instruction Set Architecture* of a processor for instance which tailors well to this technique, or an Application Specific hardware structure which must be able to perform different operations in parallel or sequentially. The limit of this design-flow could be found just into the imagination of the designer who has to be able to split the system to plan into smaller pieces, following the *Divide and Conquer* paradigm.

## Acknowledgements

First of all, I want to thank my supervisors who have helped me during this research by giving me a great support both professionally and from a human perspective. In particular, I want to thank Prof. Luciano Lavagno who introduced me to world of hardware and software modelling, and guided me to the path who led me to Newcastle University where I have conducted my Masters thesis. Then, I would like to thank Dr. Andrey Mokhov who helped me to get settled in Newcastle upon Tyne, to carry out my dissertation and who has fostered my education throughout this research answering to my countless and stressful questions, he has been more than a simple supervisor to me. They have also helped me with invaluable advices which guided me throughout the decisions for my future career. I am also grateful to Prof. Alex Yakovlev, without his support I would have not been able to study in United Kingdom.

Additionally, I would like to send my acknowledgements to all the collegues of the School of Electrical and Electronic Engineering of Newcastle University I have had the pleasure to work with: Danil Sokolov, Maxim Rykunov, Paulius Stankaitis. They have shared their knowledge with me supporting my work and this research.

Moreover, I want to send my best acknowledgements to my whole family who have supported and tolerated me since I was young, thoroughly encouraging me to study hard even during the most difficult situations. I will be always thankful to them because, even though the countless sad situations have been through, they have never ever stopped to believe in me. Furthermore, I am grateful to Silvia, who has sustained me throughout the years as a student, tolerating me during the exams sessions and cheering me up when I was upset, tired or about to give in, even regarding the choices which led us far each other.

Lastly, I want to thank all my relatives starting from my aunt Maria Luisa and my cousin Federica who have helped me with an unbelievably great moral and professional support (first exams). My best friends who have been extremely important in my life and that have contributed to shape my character. And also my grandparents, with a particular emphasis on Pina who would have been extremely glad to see me achieving this goal.

# Chapter 1 Introduction

The constant growth in the number of transistors it is possible to integrate in the same amount of area of an integrated circuit (as Moore estimated [1]), makes optimisation area problem one of the main concern designers should care about during the design of whichever electronic device. Additionally, the increasing amount of operations a component should be able to perform leads the need of an easy and flexible model to represent a system, simplifying not only the former phases of design-flow but even the latter ones. In fact, most of the mistakes that may affect a device stem by wrong specifications, or by the lack of a sound model to represent the whole system. On the light of above, a representation which cares about area/power consumption is needed, in order to reduce time to market of the products without loosing the quality of the device.

IDC (International Data Corporation), which is a corporation that helps IT professionals, business executives, and the investment community taking decisions via world wide statistics, forecasts an exponential growth on the smartphone shipment over the next few years, as depicted on Figure 1.1. It represents another valid reason for designers to address the high requirements in terms of battery life of mobile devices.

As illustrated in [11], four drivers lead the need of developing low power devices: technological, market, economical and environmental one. Poncino describes the former one as "the difficult to pack devices with high power consumption". In addition, another element which brought designers to care about power consumption was the big difference between battery and silicon technology improvement. As represented on Figure 1.2 in fact, during the past few years, while the silicon has been seeing an exponential enhancement, battery capacity has been remaining slightly unmodified, reducing battery-life of products.

Additionally, while *Market* is always more represented by higher number of portable devices, *Economical* reason expresses the correlation between the power consumed by a device and the cost of manufacturing it, due to chip packaging cost,

Figure 1.1: Mobile devices growth along years, research by *IDC* [2].

Figure 1.2: CPU-Batteries improvements throughout years, Figure taken from [11] p.7.

as depicted on Figure 1.3). Finally, it's important to develop low power components in order to build a sustainable market, as represented by *Environmental* reason.

Figure 1.3: Cost of chip package Vs Power consumption, Figure from [11] p.12.

In this research, I am going to tackle the problems illustrated above, by introducing a new design-flow which fits well to asynchronous dataflow reconfigurable hardware architectures. As the former word explains having a self-timed structure may save power and area at the same time. Maxim Rykunov, who developed a totally self-timed 8051-based microprocessor on [4], states: "with a current multibillion transistor design distribution of a global clock in the entire system could be costly in terms of area and power (up to 40% of the total chip power consumed by the clock distribution network)" ([4] p.6). Furthermore even a more flexible structure could be implemented, as proved in [4], able to keep working in very different operating conditions. It might tailor well to different kind of applications, spacing from medical to consumer market.

Additionally, designing a reconfigurable dataflow architecture means avoiding the whole the control-flow that takes place inside a single device. For instance, a RISC-based microprocessor contains several modules: from the fetching side to decoding part, which are in charge simply to figure out what an instruction should do. This is completely avoided with a dataflow structure which can execute the operation straight away. The drawback in the usage of such structure is the poor flexibility: as one might observe indeed, this application specific circuit can only perform one operation. Therefore the need of making such structure reconfigurable, in order to obtain an extremely good result tradeoff between flexibility and area/power consumption, as well as speed.

Hence, this work takes place. A recent model, able to describe such architectures very efficiently was born in order to support event-based hardware development. It is named *Conditional Partial Order Graphs* and described on [3] and [49] by Andrey Mokhov. First attempt to use such model can be found on [51], where phase-regeneration circuitry was the main concern. Afterwards, the theory of *Partial*

*order* has been elaborated and first presented officially on [50], where it was used in the context of asynchronous circuit design.

The model is composed by various number of graphs describing the different behaviours a system should be able to execute, and each of them may be seen also as a dataflow graph. The main goal of this thesis is to fill in the gap in this model by developing an algorithm for automating the composition of the separated graphs synthesising and mapping them on a real circuit, with a gate library set by the designer, trying to reduce area consumption of the controller for managing the whole structure. And to present the design-flow over a real application, with the future purpose to print it into an *ASIC*.

So far, *Conditional Partial Order Graphs* representation (hereinafter also called as *CPOG*) was used to build models for event-based hardware design, likewise dataflow structures, as well as asynchronous circuits. First step for synthesising such model into Boolean equations, is to assign an op-code to each scenario that composes the whole representation. The choice of a different encoding for each graph, affects the area of the final decoding circuit, and as will be pointed out over the next Chapters, the higher the numbers of *Partial orders* which compose the representation, the bigger the the area of the final circuit.

First aim of this research thus, is to automate the composition of several dataflow structures on the basis of *CPOG* theory, trying to reduce the area of the final decoder as much as possible. Along the research various examples will be analysed, and the design-flow will be applied to real applications, in order to demonstrate the results of the algorithm, and the applicability of this CPOG-driven flow in a more concrete case of study. Plenty of graphs have been analysed during time spent in the research. Here, for sake of readability, just few of them will be showed and discussed, the most meaningful ones.

The dissertation is composed by following Chapters: the Introduction presents the problem from a general point of view and illustrates the aim of this research, **Chapter 2** shows the background knowledge it is needed to reader for deeply inspecting the topic. Over the **Chapter 3** I am going to present and discuss about all the elements a designer needs to develop an asynchronous architecture, pinpointing on how to design a self-timed pipeline. Afterwards I am going to analyse the general procedure to design a reconfigurable hardware structure via the *CPOG* representation. The Conditional Partial Order Graph automation encoding problem is presented and discussed over the **Chapter 4**, where a rigorous analysis will be done, pinpointing on area optimisation. **Chapter 5** outlines the results obtained regarding high level software part (Graphical User Interface for supporting automation of graphs composition), illustrating how I modified the plugin for *CPOG* on **Workcraft**. Over **Chapter 6** is described an interesting possibility where such representation might be applied for: Instruction set architecture development, focusing on an example of a real processor. Finally, on **Chapter 7**, the designing phase of a reconfigurable dataflow asynchronous processor will be showed, in order to make reader understand the power of such design-flow applied to a real application. Finally the **Conclusion Chapter** where the key contributions of this thesis are presented, and the area of future research are outlined.

# Chapter 2 Background

This work is mainly based on previous research elaborated at Newcastle University, in particular by Dr. Andrey Mokhov and team of  $\mu$ System Research Group at School of Electrical and Electronic Engineering. With their work [3], they introduced a new light and flexible formalism able to model different event-based systems, spacing from self-timed to synchronous architectures.

Potentially, this representation might model each kind of structure that could be splitted into multiple events. For instance, as demonstrated in [4] by applying this formalism to Intel 8051, even the ISA of a processor could be modelled and synthesised with *Conditional Partial Order Graph* representation. Additional examples of the application of such method could be found in chapter 8 of [3].

In this Chapter I am going to revise the essential features of *CPOG*, in order to help the reader to understand this research and to introduce him to such formalism. Afterwards I am going to revise the properties of dataflow-computing, analysing the definitions and the different typologies it might be represented as.

#### 2.1 Conditional partial order graph model

**Definition.**<sup>1</sup> Conditional Partial Order Graph is a quintuple  $\mathcal{H}(\mathcal{V}, \mathcal{E}, \mathcal{X}, \rho, \varphi)$  where:

- V is a finite set of vertices which correspond to the events in the modelled system. V defines the system's event domain.

- $\mathcal{E} \subseteq \mathcal{V} \times \mathcal{V}$  is a set of edges representing dependencies between the events.

<sup>&</sup>lt;sup>1</sup>This definition was elaborated entirely by Andrey Mokhov on his PhD dissertation [3], p.38. I just report it to introduce briefly this model for the reader.

- Operational vector  $\mathcal{X}$  is a finite set of Boolean variables. An opcode is an assignment  $(x_1, x_2, ..., x^{|\mathcal{X}|}) \in 0, 1^{|\mathcal{X}|}$  of these variables. An opcode selects a particular partial order from those contained in the graph.

- $\rho \in \mathcal{F}(\mathcal{X})$  is a restriction function, where  $\mathcal{F}(\mathcal{X})$  is the set of all Boolean functions over variables in  $\mathcal{X}$ .  $\rho$  defines the operational domain of the graph:  $\mathcal{X}$ can be assigned only those opcodes  $(x1, x2, ..., x^{|\mathcal{X}|})$  which satisfy the restriction function, i.e.  $\rho(x1, x2, ..., x^{|\mathcal{X}|}) = 1$ . A graph is called singular iff its operational domain is empty, i.e. function  $\rho$  is a contradiction:  $\rho = 0$ .

- Function  $\varphi : (\mathcal{V} \cup \mathcal{E}) \to \mathcal{F}(\mathcal{X})$  assigns a Boolean condition  $\varphi(z) \in \mathcal{F}(\mathcal{X})$  to every vertex and arc  $z \in \mathcal{V} \cup \mathcal{E}$  in the graph. Let us also define  $\varphi(z) := 0$  for  $z \notin \mathcal{V} \cup \mathcal{E}$  for convenience.

This model is based on strict graphical representation, where each event is represented by a circle  $\bigcirc$ , and each connection between vertices is named arc, depicted as an arrow  $\longrightarrow$ . Both the previous elements are labelled with a predefined pattern composed by vertex/arc name, followed by condition  $\varphi(v/e)$ . Next to each graph, a further condition is present called "restriction function" ( $\rho$ ), composed by operational variables  $\mathcal{X}$ .

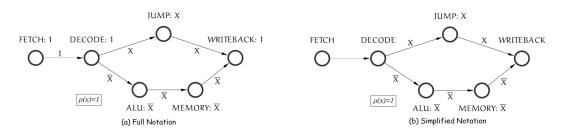

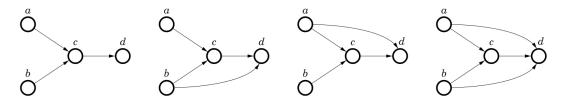

Figure 2.1: Graphical representation of a *CPOG*.

On figure 2.1, an example of a *Conditional Partial Order Graph* model is depicted. On the left of it all the Boolean conditions over each vertex and edge are listed, while on the right side of the Figure, a simplified notation is used. That is, where the element is always present in the model, a logic 1 is present, also indicated as no literals.

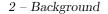

The purpose of the condition  $\varphi$  is to switch on/off vertices and edges, when the conditions on it are satisfied or not respectively. A clearer example could be observed on Figure 2.2, where the left side of the Figure shows the projection of the model if  $\mathcal{X} = 1$ , on the right side the projection on the other hand.

In this representation, dash edges and circles represent nodes and arrows switched off, in such a way not to affect the behaviour of that particular event class. Notice

**Figure 2.2:** *CPOG* projections:  $\mathcal{H}|_{\mathcal{X}=1}$  on the right,  $\mathcal{H}|_{\mathcal{X}=0}$  on the left side.

that, the edges followed by a logic 1 are not present if one of the two vertices associated on it is not present too. It is a quite important feature, that allows representing the introduction of the Don't Care Boolean conditions.

The purpose of this research is expanding the next step, that is the synthesis phase when a CPOG is already optimised, ready to be translated into logic circuit. For this purpose, later on behavioural semantics of the model will be presented.

#### 2.1.1 A factorial issue in the number of solutions

Once the *Partial Orders* have been prepared and optimised by the designer to model a system, each graph must be associated to an op-code in order to be distinguished by the remained ones. This is the first step of the synthesis stage, where the controller for managing the whole structure should be synthesised. Before discussing about the main issue I am going to handle during this research, let us define some useful words that will be used along the pages of the dissertation.

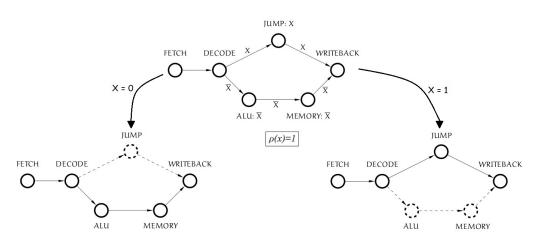

**Op-code** points out a variable length array of bits where each element can be a logic 0 or 1, the following ones are examples of feasible op-codes  $\{0010, 000000, 1110001, 0\}$ . **Op-code ensemble** is defined as the the group of *op-codes* it is possible to use with a particular number of bits, for instance the *Op-code ensemble* of length 2 is composed by *op-codes*:  $\{00,01,10,11\}$  while the one of length 3  $\{000,001,010,011,100,101,110,111\}$ . An **encoding**, also referred to as **solution**, is a subset of an *op-code ensemble* where each *op-code* is associated to one and only one *Partial Order* graph. Finally, the **solution space** is represented by the group of all the possible *encodings* for a particular CPOG. On Figure 2.3 is depicted the op-codes available to encode a CPOG that contains up to 8 *Partial Order*, composed by 3-bits op-codes.

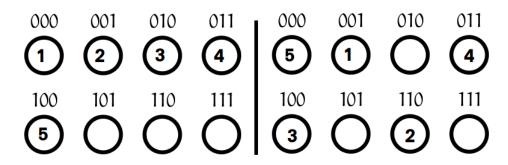

Figure 2.3: Op-code ensemble of length 3.

While on Figure 2.4, two possible solutions for what concerns a 5 graphs CPOG are depicted taking into account the op-code ensemble on Figure 2.3.

Figure 2.4: Two possible encodings for CPOG composed by 5 *Partial Orders* with 3-bits opcodes.

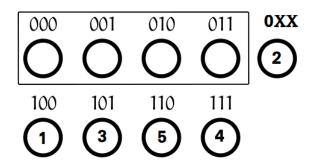

Moreover, another possibility designers have to exploit the higher size of the op-code ensemble with respect to number of graphs to encode, is represented by the *Don't care* conditions. For instance, on Figure 2.5 is represented the situation where the second *Partial Order* is encoded by the op-code 0XX.

On the light of above, as one might observe, there are plenty of possibilities to encode all the graph in a representation, therefore the size of the *solution space* can be really high depending on number of the graphs to encode and length of the opcode ensemble. Even though solutions allowing *don't care* conditions will be taken into account in this research, now I am going to neglect the *encodings* stem by them in the computation of the size of *solution space* due to the high complexity that might be followed. However this issue will be addressed on Chapter 5.

Referring to starting aim of this Section, the main goal of a designer, is the find inside the *solution space* related to a model, the best possible *encoding* in terms of area of the final controller. Due to the lack of a heuristic cost function able

Figure 2.5: Encoding for CPOG composed by 5 *Partial Orders* with 3-bits opcodes exploiting don't care.

to inspect cleverly each *solution*, designers needed to apply each different *encoding* to the representation and to synthesise it on a real circuit in order to be able to compare the various *solutions*. Nonetheless, as one might observe, it is extremely time consuming, in particular for the CPOGs contain several graphs internally. Indeed, as this Section aims to explain, the size of the *solution space* is directly correlated with the number of *Partial Orders* the model is composed by and by the length of the *op-code* designer wants the graphs the be encoded with. I

Hence, the size of the *solution space* is of primarily importance because potentially, all the *solutions* might become a good *encoding* in terms of area and should be inspected. As a consequence, an increase in the size of the possible *solutions* may mean a higher complexity during the search phase and might worsen the final solution. This is why the main aim at this step is trying to reduce the size of the *solution space* as much as possible.

Hence, the need of a function able to target a subset of *encodings*, without going through the entire *solution space*. Before concentrating on it, let us discuss about the size of the *solution space*, it is useful to understand how we can approach the problem.

Let us consider a very small *Conditional Partial Order Graph* representation, composed by 4 different graphs only. As analysed in [3] and briefly above, there could be several approaches to encode various graphs in order to minimise the Boolean function in each vertex and edge, they could be encoded on minimum number of bits, or by using an one hot encoding fashion for instance. What we are going to take into account below will be *op-codes ensemble* with minimum length related to number of *Partial Orders*.

It means that in order to encode 4 different graphs, we need 2 bits (*Op-code* ensemble of length 2). Therefore, in order to get the minimum number of bits needed to encode an entire model we need to use formula 2.1, where m stands for the size of current op-code ensemble, assuming the graphs to be encoded with

op-codes on minimum number of bits.

$$\#\{\mathcal{B}\} = \lceil \log_2(k) \rceil \tag{2.1}$$

In this case, number of *encodings* fit perfectly graph to encode since with two bits it is possible to encode exactly four elements  $(2^2 = 4)$ . Afterwards, in order to compute the entire solution space of such instance we should refer to permutation problem. It states that the total number of solutions we can select by sorting elements differently each time in a group of *m* different elements would be:

$$\#\{\mathcal{S}\} = \frac{m!}{(m-k)!}$$

(2.2)

where k is the number of graphs to encode. Since in such case m = k, formula comes up from example just mentioned depicted below:

$$\frac{4!}{(4-4)!} = \frac{4!}{1} = 4! = 24$$

Thus, total number of solution in this case is 24.

Moreover, there is another issue we have to take into account for reducing the size of *solution space*. The *encodings* I just considered contain all the possible combinations come up by permuting all the elements inside the *op-code ensemble*. Nonetheless one could reduce the *solution space* even more by fixing the first element of the *encoding*, without loosing any good results. It is because for each *encoding* present in the *solution space* can be found a complementary *solution* which comes up with the same final controller as for the complementary *encoding* with some inverter gates at the starting point. Thus with no area gain at all.

Hence, by taking into account statement before, we could modify formula 2.2 into:

$$\#\{\mathcal{S}\}' = \frac{(m-1)!}{(m-k)!} \tag{2.3}$$

It is extremely beneficial for the size of the *solution space*. By analysing problem before the ensemble reduces as following:

$$\frac{(4-1)!}{(4-4)!} = \frac{3!}{1} = 3! = 6$$

Since the gap in the *Partial Order* composition did not allow to automatically compose the graphs obtaining the area of the final controller. In order to first analyse the size the final controller comes up with various *encodings* and try to understand whether a correlation exists. I have focused on very small *Conditional Partial Order Graph* models, as it will be discussed on next section.

#### 2.1.2 Examples considered

In order to be able to inspect all the solutions for a particular Partial Order Graph, at the beginning just smaller graphs have been considered. It is because, the number of solutions actually available depends on the number of Graphs in a single representation in a factorial fashion, thus the more the number of CPOGs, the more the solutions available for the entire model as argued in chapter 2.1.1.

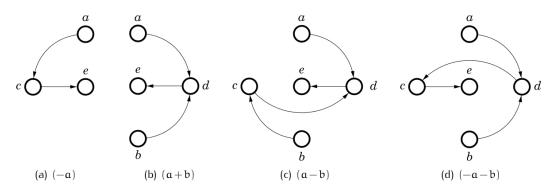

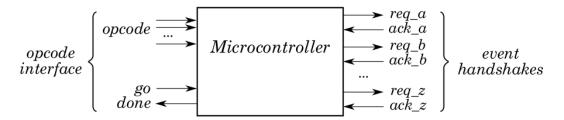

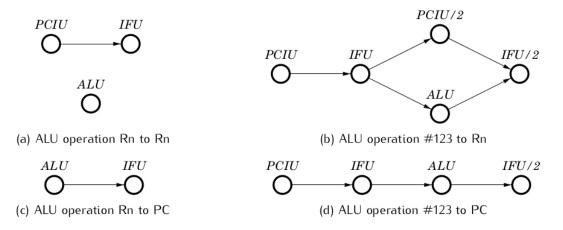

Hence, models analysed in order to see whether a correlation is present are the following ones, taken from [3]. As depicted in Figure 2.6, it is one of the most basic model for four arithmetic instructions of an ALU unit.

Figure 2.6: Simple *CPOG* models four basic operations of a *ALU*,([3], Figure 7.9).

A and b nodes represent load of a and b register respectively. C represents inverting operation, d the addiction and e the store instruction. As one could see this model is compact, and powerful at the same time, and may be able also used to model quite complex instructions, belonging to different kind of sectors inside the CPU, into very comprehensible and manageable graphs. This first example, is quite basic and simple, and allowed me to understand how I could deal with this representation.

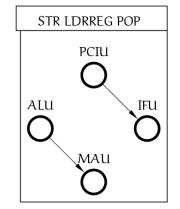

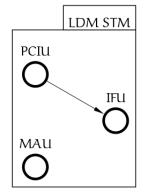

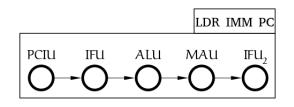

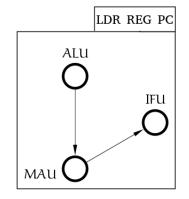

Then I handled other two representations, always composed by 4 CPOG, in such a way to keep the number of solutions reduced to 6 (by fixing first element), so that to inspect well the entire solution space. The models used were taken from a more bigger CPOG composed by eight instructions classes who will be analysed separately later on.

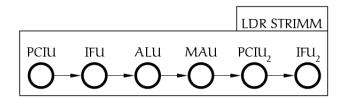

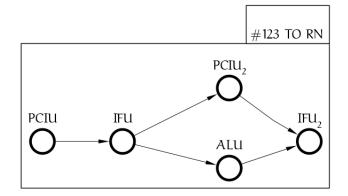

At this point, I analysed as two separate models the graphs  $\{a, b, c, d\}$  and  $\{a, c, g, h\}$  which may be seen as the representation of the path an instruction should go through inside a general processor: each node indeed, corresponds to a different stage of CPU part. For instance *IFU* stands for Instruction Fetch Unit, the component in charge of fetching next instruction from Instruction memory. *MAU* stands for Memory Access Unit, *PCIU* for Program Counter Increment Unit, the

Figure 2.7: 8 instruction classes model.

one able to increment Program Counter register in order to select next instruction, and so on and so forth.

Since Conditional Partial Order Graphs is an acyclic directed graph model, when the flow should pass twice through a single node, another node, referred to as "/2" upfront is needed, just for distinguishing among two different stages of the same vertex.

Another issue we should address before working with CPOG representation, is conditions on vertices. As in the node ALU/2 on f graph on Figure 2.7, nodes might have a condition on it; it means that the vertex, and the associated edges would be present inside the graph, if and only if the conditions on that vertex are satisfied. The theory of how to synthesise this kind of particular nodes is reported in [3].

#### 2.1.3 Boolean equations extraction for each CPOG element

First of all, what I had to do was extracting the Boolean conditions for each element of the graphs. Very basic operations are performed to reach this goal out, which may be done manually on such small graphs. Over this Section these kind of operations are illustrated and explained, with the help of short examples.

In order to get the Boolean equations of an element (either node or edge), one needs to represent it by means of Boolean conditions on each particular *CPOG* projection. Concerning a node: it could be present or not, depending whether it would affect or not the behaviour of a projection respectively. If it does one should represent the node with a 1, otherwise with 0. On the other hand, an edge could be more difficult to manage, because we have to take into account some properties of the model in order to optimise it as much as we can, such as the transitive property depicted on the Definition below.

**Definition**<sup>2</sup>. A dependency a < b (where < denotes edge from a to  $b \ a \rightarrow b$ ) between events  $a, b \in S$  in a partial order  $\mathcal{P}(S, <)$  is called transitive (denoted as a << b) iff there exists an event  $x \in S$  such that both conditions a < x and x < b hold:

$$(a \ll b) = \exists x \in \mathcal{S}, (a \ll x) \land (x \ll b)$$

$$(2.4)$$

Therefore, if in a particular graph two vertices are not directly connected, but they are in a transitive manner, one has to represent the edge in the projection with a Don't Care X. Let us consider for instance the Partial Order Graph on the Figure 2.8.

Figure 2.8: Partial Order Graphs example ([3], Figure 2.5).

The left-most image represents the reduced graph and on the Table 2.1 is depicted an example of the right way to assign a Boolean condition for that particular graph. As we can notice, a < d edge for instance is represented by a Don't Care condition; it is because a is connected to d by a transitive edge, as in the third graph from left of Figure 2.8.

<sup>&</sup>lt;sup>2</sup>Definition 4.2 from [3]

| 2 - | Background |

|-----|------------|

|-----|------------|

| Edge  | <b>Bool.</b> Condition |

|-------|------------------------|

| a < b | 0                      |

| a < c | 1                      |

| a < d | Х                      |

| b < a | 0                      |

| b < c | 1                      |

| b < d | Х                      |

Table 2.1: Example of Boolean conditions assignment of graph on Figure 2.8

Another rule we have to follow to assign conditions to each arc is the following: if at least one out of two vertices of the edge one is considering is not present, a Don't Care condition (X) might be assigner to that edge. It is because, no matter the presence or not of the edge, it would not influence the projection at all since the nodes are not present.

Once an encoding for each of the CPOG class has been chosen, one has to minimise the condition for each element via a logic minimiser. I used Karnaugh Map method when I faced with simple 4 instruction classes CPOG, while Espresso logic minimiser [13] while dealing with more complex representation.

On the light of above, I would like to show to reader the results of Boolean conditions extraction starting from a couple of encodings. They have been applied to CPOG showed on Figure 2.9, Boolean conditions are reported on Table 2.2. As explained on Section 2.1.1, there are 6 solutions per model (the small ones), but for simplicity's sake, just two of them will be reported, the most meaningful.

As one may notice, the first encoding looks way much better than the second one in terms of number of literals present in the Boolean equations. On the light of above, over the next section these conditions would be exploited in order to compute equations for the final controller, area measurements will be performed on it.

#### 2.1.4 Boolean equations extraction for the model

In order to extract all the Boolean equations from the *Conditional Partial Order Graph* model for developing the final circuit implementations, various steps are needed. Even tough they are described in [3], I want to outline some behavioural features of the representation.

As discussed on Section 2.1, when a CPOG is ready to be synthesised into Boolean equations, each vertex and edge have a Boolean condition associated to itself. And according to these conditions, a part of the graph would be present or not dynamically in the actual representation if and only if that condition is satisfied.

|                | Encoding Solutions    |                              |  |  |

|----------------|-----------------------|------------------------------|--|--|

| Elements       | 00 01 11 10           | 00 11 01 10                  |  |  |

| IFU            | !X0+!GE               | ((!X0*!X1) + (X0*X1))+!GE    |  |  |

| IFU < PCIU/2   | 1                     | 1                            |  |  |

| IFU < ALU/2    | 1                     | 1                            |  |  |

| PCIU/2         | (GE * X0) + (X0 * X1) | (!X0 * X1) + GE * (X0 * !X1) |  |  |

| PCIU/2 < IFU/2 | 1                     | 1                            |  |  |

| ALU/2          | X0*!GE                | !GE * ((X0*!X1) + (!X0*X1))  |  |  |

| ALU/2 < IFU/2  | !X1                   | !X1                          |  |  |

| IFU/2          | X0                    | (X0*!X1) + (!X0*X1)          |  |  |

| PCIU < IFU     | 1                     | 1                            |  |  |

| PCIU < PCIU/2  | 1                     | 1                            |  |  |

| PCIU           | X0+!X1                | !X0+!X1                      |  |  |

| ALU < IFU      | X0 + X1               | X0 + X1                      |  |  |

| ALU < PCIU/2   | 1                     | 1                            |  |  |

| ALU            | 1                     | 1                            |  |  |

**Table 2.2:** Boolean equations for each element for CPOG on Figure 2.9

Figure 2.9: Conditional Partial Order Graph with 4 instruction classes.

Before discussing about synthesis process, it is worth enunciating following definition:

**Definition**<sup>3</sup>. Opcode  $\psi : \mathcal{X} \cup \mathcal{Y} \to \{0, 1\}$  assigns Boolean values to all the static and dynamic operational variables in the graph. The preset  $\bullet_{\psi} v$  of a vertex  $v \in \mathcal{V}$ with respect to opcode  $\psi$  is:

$$\bullet_{\psi} v := \{ u \in \mathcal{V}, \ \varphi(u)|_{\psi} \cdot \varphi(u, v)|_{\psi} = 1 \}$$

$$(2.5)$$

It contains all the vertices  $u \in \mathcal{V}$  which precede vertex v in the partial order defined by complete projection  $\mathcal{H}|_{\psi}$ .

By considering definition just listed, I can analyse the mapping procedure for building the controller. During this phase a set of equations are produced. The overall size of them is thoroughly correlated to the size of the starting CPOG in terms of number of graphs and conditions on their elements, as already pointed out before. Therefore, applying optimisation techniques, as described in [3], before synthesising the final controller is extremely important in order to reduce the whole size of the circuit. Aim which must be also pursued by selecting the best op-code assignment, as this dissertation want to demonstrate.

<sup>&</sup>lt;sup>3</sup>Definition 5.17 from [3]

Andrey Mokhov, the author of *Conditional Partial Order Graph*, describes mapping procedure in the following way:

Mapping procedure. ([3], p.93) "a vertex  $v \in \mathcal{V}$  is enabled to fire if and only if:

- 1. It belongs to the current complete projection, i.e. its condition is satisfied:  $\varphi(v) = 1;$

- 2. All its preceding vertices have already fired, i.e.  $\forall u \in \mathcal{V}, (u \in \bullet v) \Rightarrow fired(u)$ .

This can be captured in terms of Boolean equations as follows:

$$enabled(v) = \varphi(v) \cdot \prod_{u \in \mathcal{V}} \{\varphi(u) \cdot \varphi(u, v) \Rightarrow fired(u)\}$$

Now predicates enabled(v) and fired(v) should be replaced with real signals."

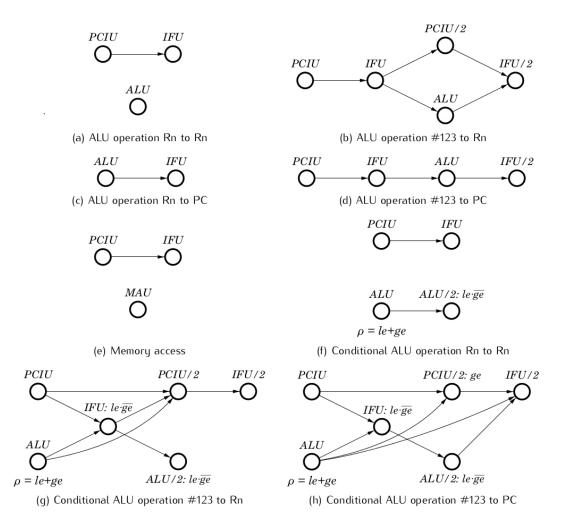

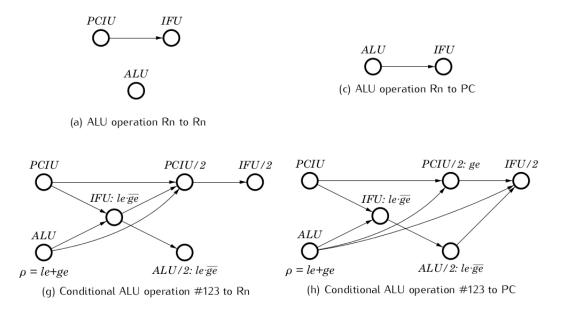

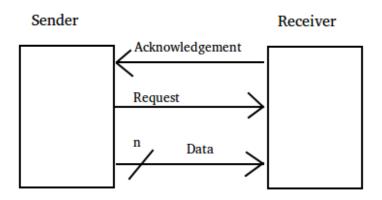

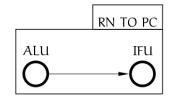

For instance, one might use an asynchronous-based interface where the transactions are managed by a central control-unit (as depicted on Figure 2.10) by a request-acknowledgement handshake interface. The enabled(v) might be represented by signal  $req_v$ , and fired(v) by signal ack(v).

$$req(v) = \varphi(v) \cdot \prod_{u \in \mathcal{V}} \{\varphi(u) \cdot \varphi(u, v) \Rightarrow ack(u)\}$$

(2.6)

In simple terms: an event is allowed to send a request signal as soon as preceding event has been completed (signalled by an acknowledgement).

Figure 2.10: CPOG-based microcontroller with acknowledgements/requests interface, taken from [3], Figure 7.4.

Once discussed about rules on how to extract Boolean equations from CPOG model, the only thing one needs to care about is grouping together each Boolean function for every vertex, in order to feed ABC tool and minimise Boolean equations. In such a way to perform a fair comparison for what concerns the encodings applied.

#### 2.2 Dataflow computing

Dataflow structure is a special kind of architecture which totally differs from control-flow like structure, because data can freely flow through the execution part of the computation, avoiding the decoding part of the instructions typical of a standard CPU of a CISC/RISC-based processor. In a general purpose processor indeed, before an instruction is executed, it must go through various stages of the pipeline which are useful to the CPU to fetch such instruction from the memory, and then to decode it. Hence, the typical stage an instruction must follow for being executed are the fetching phase and the decoding one; afterwards (depending on the instruction) even the operands the computation is based on must be fetched from the data-memory (in case of *Harward architecture*<sup>4</sup>) in order to have the operands of the computation ready for it.

Since all these operations are executed in parallel, the throughput of the CPU, which represents the rate of instructions to be executed in a specific amount of time, is not affected by such a long pipeline. It is implemented in this way in order to minimise the number of times CPU must wait for the result of any previous instructions of the program. Nonetheless, although this paradigm tailors well to really general purpose applications, that is where the user may carry out very different operations. It does not fit well to some particular kind of applications where, even tough the variability of the behaviour of the system can range from 1 to n predictable operations, such a big waste in terms of area can be avoided.

Even though the throughput of the processor is not affected by the control flow architecture, area is. As one might observe on Figure 2.11 indeed, the computational part which is the only really useful area dedicated to application occupies the minority of the whole chip. The one on the Figure is just a general example, but it is enough to make reader understand how much area one might save by avoiding the whole memory and control flow architecture, even if in this case the hardware would lose flexibility. Over the past few years dataflow computing has been one of the main research area of many companies, such as for Maxeler Technologies as one might read on [56] for example.

A good tradeoff could be obtained by making the dataflow structure reconfigurable. It means having various dataflow systems that can be also very different each other, but that can be interchanged as soon as user needs it. What one gains is having as many structures as wants where data can directly flow through, the area of the controller for managing the reconfigurability part may be negligible with respect to the area dedicated to computation and there is not an increment in the

<sup>&</sup>lt;sup>4</sup>Harvard architecture differs with respect to Von Neumann structure because data and memory are stored in two different memory elements.

#### L1 Data Cache L2 Cache Interrupt Computation Memory Ordering & Execution Paging **Branch Prediction** Out-of-Orde cheduling letiremer Decode 8 Instruction Fetch & L1 Cache Memory Controller Core Соге Core Core Соге Core id Uncore anar Shared L3 Cache Shared L3 Cache

#### Intel 6-Core X5680 "Westmere"

**Figure 2.11:** Particular of Maxeler Technologies transparencies, Slide N. 5 "Introduction of Dataflow computing" [30]

delay since all the structures are already synthesised onto the ASIC/FPGA chip under usage.

The really advantage of the representation I am going to use is the possibility to share different internal components between the dataflow structures available. Indeed CPOG allows designers to synthesise a controller able to activate the part actually needed for the computation without synthesising it multiple times onto the chip, getting a higher save of the area too.

In this Section I am going to introduce the dataflow paradigm, focusing on the typologies that such structures may have.

#### 2.2.1 Dataflow theory

Systems can be divided in two categories: *control-dominated systems* and *data-dominated systems*. The former ones are strongly dominated by taking decision

and by the latency, the computation time is not a main concern provided that it is lower than the clock period superimposed by the external environment. The latter one whereas are structures where the main concern is on data computation and the throughput. Here each part composes such systems is autonomous and often asynchronous.

In this paragraph I am going to cover three dataflow networks:

- Kahn process neworks

- Static dataflow neworks

- Boolean dataflow neworks

Maurizio Tranchero et al. describe in [31] the Kahn process as networks of processes made by sequential deterministic code, where each state communicates with the next one via a point to point  $FIFO^5$  connection. Reading operations are blocking, it means that a process does not go on until data is present on input FIFO. It guarantees the determinism, but may cause deadlock if such process does not receive any more data in input. Moreover another problem that affect such structures is the infinite memory requirements, due to various speed of the processes. A practical example may be found on [31] on pages 102-103.

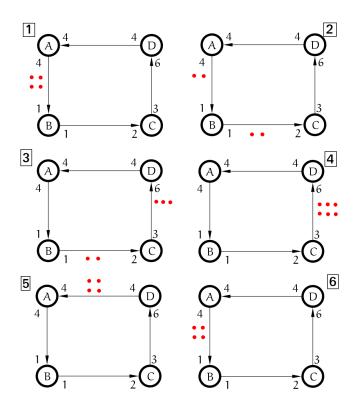

Static dataflow networks are a subset of the Kahn process networks, where the deadlock and the problem of infinite memory requirement is addressed. Each process indeed can be executed repeatedly reading and producing a fixed number of data, when it is present in its input. Moreover the position of the initial values are fixed at the beginning and they are called *tokens*. On Figure 2.12 an example is depicted.

The red dots represent the token, the numbers close to each state are the reading/production rates depending whether the arrow goes in or out respectively from the process, for instance process C takes 2 token and produces 3 tokens on the next FIFO each time. If the reader follows the sequence of events may see that this process may be repeated infinitely. In this case, the way the processes are scheduled is BBCBBCDA, or better 2(2(B)C)DA. It means that, if the processes follow this pattern can be executed without occurring into a deadlock and with the maximum size of a FIFO set by the connection between the process C and D which must able to contain 6 tokens.

The Boolean dataflow networks add two nodes to Static dataflow networks: split and merge. They are needed to express Boolean conditions for certain kind of applications like compression/decompression (as stated in [31]). Such structures are showed on Figure 2.13 and can be used to develop *loop* and *if-then-else* patterns.

$<sup>{}^{5}</sup>$ FIFO = First IN First OUT.

Figure 2.12: Static Dataflow Network example

Figure 2.13: Split and merge structures. ([31], Figures 6.12 - 6.13)

In summary, there can be different typologies of dataflow structures. The ones I am going to deal with are *static dataflow network* where the rate of reading/production is 1, and where the processes start executing itself when data is present at the input. As already mentioned, this representation I am going to use fits well to

asynchronous structures which do not need any memory between two processes due to protocol implemented.

### Chapter 3

## Asynchronous dataflow pipelines design

In this Chapter I am going to discuss about the design of dataflow pipelines, pinpointing on self-timed structures. As already mentioned before, several devices may benefit from asynchronous pattern usage for different reasons: first of all the lack of the clock-net extremely reduces the size of the design which can be really affected by such component. It affects also the power consumption, since even when the device is not working the clock is always active consuming power constantly. Designers tried during the last few years to lower such a source of power consumption by means of techniques as *clock gating*, or by acting at the RTL Level pre-computing the result for what concerns common case computation [11]. But it turns out that such modifications contribute to an higher size of the design as well increasing the static power consumption which is getting bigger than dynamic one nowadays [12].

Asynchronous designs may contribute solving such problem due to the capability to work when the data is ready only. Self-timed hardware structures indeed, consume an extremely small amount of power consumption when the data is not ready at the inputs. Even though such structures may bring great advantages to VLSI market, they have been neglected for many years also due to the complexity of the development phase, in particular from the protocol point-of-view. One of the aim of this research is to simplify such design-flow, in order to lead designers to use such structures more easily.

On the light of above, I am going to present all the tools a designer may need for developing self-timed hardware. The reconfigurability of the dataflow graphs will be discussed over the next Chapter.

## 3.1 Pipelining introduction

Before going through the core of this Chapter, it is worth giving a short introduction to readers about the general concept behind the *Pipeline*. In the context of Computer Science, a pipeline is defined as a set of processing parts, completely separated each other, which are connected in succession to form a system.

The singularity of this structure is the capability of each single module the pipeline is composed by to work without the influence of the preceding parts. Let us think for example about a general pipeline inside a RISC-based *CPU* for executing instructions, it is composed by five computational elements: **Instruction Fetch** which is in charge of getting the instructions from the memory (typically instruction memory), hereinafter called **F**. **Instruction Decode** that is the hardware part that decodes the instruction to figure out which operation needs to be performed and to fetch the operands for the computation, called **D**. **Execute/E** which is in charge of actually executing the instructions, **Memory access/M** that load/store instructions into memory and finally **Write Back/WB** which writes the results into a processor registers or forwards them into the ALU whether some particular conditions occur. Such structure is depicted on Figure 3.1

Figure 3.1: General structure of a RISC-based processor. ([32], P. 13)

As one may notice, this structure is not pipelined because it lacks of the structures needed to store the results in the middle of the computation, that are the registers. A more complete design is showed on Figure 3.2 where the registers are present between every two consecutive stages of the pipeline.

Figure 3.2: Pipeline version of a RISC-based processor. ([32], P. 16)

The hardware structures illustrated before are synchronous. Synchronous design benefits from Pipelining-based structures because of the reduction of the critical path and as a consequence the increasing frequency the microprocessor is able to run on. One of the parameter which contributes to *maximum operating frequency* of the circuit under design is the *critical path*. It is a time measure and is defined as the slowest path in the circuit present between two memory elements (registers) and it is connected to the frequency by following mathematical relationship:

$$\mathcal{F} = \frac{1}{\mathcal{CP}} \tag{3.1}$$

Therefore, the longer the critical path, the lower the frequency the CPU can run. On the light of above, one might observe that the advantage of inserting the registers in the middle of the computational units is reducing drastically the critical path and as a consequence thoroughly increasing the working frequency of the circuit.

Nonetheless, pipelining does not lead to advantages only, because first of all it increases the area of the circuit either due to the high number of registers needed to store all the results in the middle of the pipeline, and in particular for all the management units in charge of controlling the good behaviour of the structures and avoiding problems as hazards. In this brief description, I am not going to cover all the problems stem from the pipeline-based architecture design, but if the readers is interested on it, they can find several information in [32].

A fundamental characteristic of a pipeline is the *throughput*. It is defined as the rate of production of a structure over a time unit and it is crucial in the concept of digital circuit nowadays. In order to better understand this concept I am going to present a short example taking into account the structures presented before on Figure 3.1 and 3.2. Let us assume that the time needed to execute each computational part (**F-D-E-M-WB**) is 1  $\mu$ s both for pipelined and not pipelined-based structures; and let us compare how much time would elapse to execute five generic instructions consecutively assuming no hazards.

In the case of Figure 3.1, that is the not pipelined version, the  $\mu$  processor would execute each instruction one after the other, therefore in order to obtain the total time of execution one has to multiply the number of instructions times the time needed to process each instruction, as computed below:

#### $ExecutionTime = N_{inst} \times INST_{time} = 5 \times 5\mu s = 25\mu s$

For what concerns the pipelined version, in order to compute the overall execution time we have to consider that the instructions are internally executed in parallel, as represented on Figure 3.3

| Clock cycle number |    |    |     |     |     |     |     |    |    |

|--------------------|----|----|-----|-----|-----|-----|-----|----|----|

| 1                  | 2  | 3  | 4   | 5   | 6   | 7   | 8   | 9  | 10 |

| IF                 | ID | EX | MEM | WB  |     |     |     |    |    |

|                    | IF | ID | EX  | MEM | WB  |     |     |    |    |

|                    |    | IF | ID  | EX  | MEM | WB  |     |    |    |

|                    |    |    | IF  | ID  | EX  | MEM | WB  |    |    |

|                    |    |    |     | IF  | ID  | EX  | MEM | WB |    |

Figure 3.3: Pipelined execution example. ([32], P. 26 modified)

For instance, if one considers the operations under execution on fourth clock cycles, the ones inside the red circle, he might be able to observe that the first instruction is at the **Memory** stage, the second one at the **Execution phase**, the third one at the **Decode stage** and so on. In this case the overall time of execution is 9  $\mu s$ .

Hence the total speedup one can get is:

$$Speedup = \frac{ExecTime_{nonPipelined}}{ExecTime_{Pipelined}} = \frac{25\mu s}{9\mu s} = 2.77$$

The considerations discussed above refer to synchronous-based structures and do not take into account all the hazards that may occur which might stall the pipeline slowing down the whole architecture. Nonetheless, they are enough to readers to understand the general concept in order to better follow next Sections, where the composition of an asynchronous pipeline is the main concern.

## 3.2 Asynchronous pipelining

Asynchronous circuits may have several advantages as introduced at the beginning of this Chapter. As Jens Sparso, from University of Denmark, points out in [33], self-timed-base structures may lead to great advantages such as running at high operating speed, since it is determined not by worst-case latency, but by the local one. [35], less emission of electro-magnetic noise [34], soundness towards variations in temperature, supply voltage and fabrication process parameters since the communication is based on handshaking protocols [36] and finally the lack of the clock skew problem due to the absence of the clock.

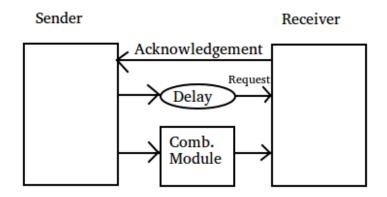

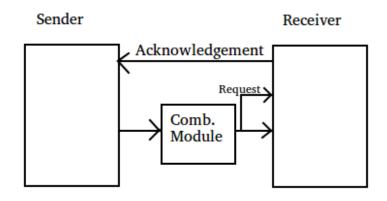

It is worth starting from a higher level of abstraction for analysing the functionality of an asynchronous circuit. As RTL (*Register Transfer Level*) represents a relatively good level of abstraction to understand what is going on inside the device regarding synchronous logic; *handshake-channel* and *data-token view* fit well to asynchronous circuits. The former models the signals connecting one register to next one, hence it represents the main link useful for communication purposes, while the latter one represents the data which is stored into the registers and that flows through the pipeline, where combinational logic between two registers should be as transparent as possible. Reader should think about a combinatorial block as a piece of logic which absorbs a token, performs its computation and outputs the results without looking at handshaking mechanism.

Figure 3.4: Dataflow asynchronous pipeline example.

As one might observe, dataflow representation tailors well to this kind of logic, and can be used for simplify the design-flow of such circuits. On Figure 3.4 are depicted the main components I described above. The tool I am going to use for representing such structures is the *Dataflow Structure Plugin* under Workcraft, in this dissertation I am not going to cover the ideas behind it but if the reader is interested might find a good starting point about the topic on [37].

This section is structured as following: in the next part I am going to introduce the protocol I used for the asynchronous transactions and then the so called *Muller pipeline* by illustrating some circuits examples for understandability's sake.

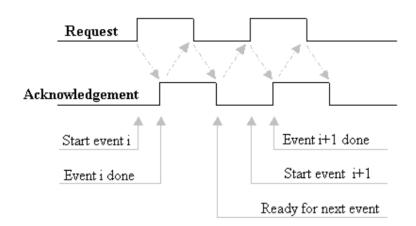

## **3.2.1** 4-phase dual-rail protocol

The advantage of having a synchronous architecture is the capability by all the elements to ideally share a predefined timing set by the clock signal. It should ideally come to each memory element at the same time, giving the possibility to every combinatorial part to finish its execution. It extremely simplifies the design process since designers may neglect the hazards that may happen between two clock ticks.

Figure 3.5: Typical handshaking protocol structure.