## µSystems Research Group

## **School of Engineering**

# Physical Parameter-aware Networks-on-Chip Design

Nizar Saadi Dahir

**Technical Report Series**

NCL-EEE-MICRO-TR-2016-202

Contact: fei.xia@newcastle.ac.uk, alex.yakovlev@newcastle.ac.uk

Supported by Iraqi Government PhD Studentship

NCL-EEE-MICRO-TR-2016-202

Copyright © 2016 Newcastle University

μSystems Research Group School of Engineering Merz Court Newcastle University Newcastle-upon-Tyne, NE1 7RU, UK

http://async.org.uk

# PHYSICAL PARAMETER-AWARE NETWORKS-ON-CHIP DESIGN

Nizar Saadi Dahir

A Thesis Submitted for the Degree of Doctor of Philosophy at Newcastle University

School of Electrical and Electronic Engineering Faculty of Science, Agriculture and Engineering February 2015

Nizar Dahir: Physical Parameter-Aware Networks-on-Chip Design ©2015

### DECLARATION

I hereby declare that this thesis is my own work and effort and that it has not been submitted anywhere for any award. Where other sources of information have been used, they have been acknowledged.

Newcastle upon Tyne February 2015

NIZAR DAHIR

## CERTIFICATE OF APPROVAL

I confirm that, to the best of my knowledge, this thesis is from the student's own work and effort, and all other sources of information used have been acknowledged. This thesis has been submitted with my approval.

ALEX YAKOVLEV

To my beloved wife, Noor, and our sweethearts, Warqaa and Zaid. — Nizar

#### ACKNOWLEDGEMENTS

I wish to express my sincere gratitude to my supervisors Prof. Alex Yakovlev, Dr Terrence Mak and Dr Fei Xia for their support, inspiring comments and guidance through my studies.

I am also grateful to the members of the Microelectronics System Design group at Newcastle University for their assistance and guidance in my studies. I appreciate the help of my friends and colleagues, Ra'ed Aldujaily, Ghaith Tarawneh, and Petros Missailidis for inspiring and wonderful discussions, productive criticism and suggestions, and for being very nice friends and supporters.

I am also grateful to Dr Maurizio Palesi for his advice and suggestions in modifying the NoC simulator and power model.

I would like to offer my special regards to all the staff of the school of Electrical and Electronic Engineering.

My father is also owed many thanks for his continuous support and encouragement and backup from abroad, which has helped me to overcome many difficulties and has given me strong motivation throughout my studies. Networks-on-Chip (NoCs) have been proposed as a scalable, reliable and power-efficient communication fabric for chip multiprocessors (CMPs) and multiprocessor systems-on-chip (MPSoCs). NoCs determine both the performance and the reliability of such systems, with a significant power demand that is expected to increase due to developments in both technology and architecture. In terms of architecture, an important trend in many-core systems architecture is to increase the number of cores on a chip while reducing their individual complexity. This trend increases communication power relative to computation power. Moreover, technology-wise, power-hungry wires are dominating logic as power consumers as technology scales down. For these reasons, the design of future very large scale integration (VLSI) systems is moving from being computation-centric to communication-centric.

On the other hand, chip's physical parameters integrity, especially power and thermal integrity, is crucial for reliable VLSI systems. However, guaranteeing this integrity is becoming increasingly difficult with the higher scale of integration due to increased power density and operating frequencies that result in continuously increasing temperature and voltage drops in the chip. This is a challenge that may prevent further shrinking of devices. Thus, tackling the challenge of power and thermal integrity of future many-core systems at only one level of abstraction, the chip and package design for example, is no longer sufficient to ensure the integrity of physical parameters. New designtime and run-time strategies may need to work together at different levels of abstraction, such as package, application, network, to provide the required physical parameter integrity for these large systems. This necessitates strategies that work at the level of the on-chip network with its rising power budget.

This thesis proposes models, techniques and architectures to improve power and thermal integrity of Network-on-Chip (NoC)-based many-core systems. The thesis is composed of two major parts: i) minimization and modelling of power supply variations to improve power integrity; and ii) dynamic thermal adaptation to improve thermal integrity. This thesis makes four major contributions. The first is a computational model of on-chip power supply variations in NoCs. The proposed model embeds a power delivery model, an NoC activity simulator and a power model. The model is verified with SPICE simulation and employed to analyse power supply variations in synthetic and real NoC workloads. Novel observations regarding power supply noise correlation with different traffic patterns and routing algorithms are found. The second is a new application mapping strategy aiming to minimize power supply noise in NoCs. This is achieved by defining a new metric, switching activity density, and employing a force-based objective function that results in minimizing switching density. Significant reductions in power supply noise (PSN) are achieved with a low energy penalty. This reduction in PSN also results in a better link timing accuracy. The third contribution is a new dynamic thermal-adaptive routing strategy to effectively diffuse heat from the NoC-based threedimensional (3D) CMPs, using a dynamic programming (DP)-based distributed control architecture. Moreover, a new approach for efficient extension of two-dimensional (2D) partially-adaptive routing algorithms to 3D is presented. This approach improves three-dimensional networkon-chip (3D NoC) routing adaptivity while ensuring deadlock-freeness. Finally, the proposed thermal-adaptive routing is implemented in field-programmable gate array (FPGA), and implementation challenges, for both thermal sensing and the dynamic control architecture are addressed. The proposed routing implementation is evaluated in terms of both functionality and performance.

The methodologies and architectures proposed in this thesis open a new direction for improving the power and thermal integrity of future NoC-based 2D and 3D many-core architectures.

#### Journal publications:

- 1. N. Dahir, T. Mak, F. Xia, and A. Yakovlev, *Modelling and Tools* for Power Supply Variations Analysis in Networks-on-Chip, IEEE Transactions on Computers (TC), vol. 99, PrePrints, pp. 1-14, 20 Nov. 2012..

- N. Dahir, R. Al-Dujaily, T. Mak, and A. Yakovlev, *Thermal Optimization in Network-on-Chip Based 3D Chip Multiprocessors Using Dynamic Programming Networks*, ACM Transactions on Embedded Computing Systems (TECS), (To appear), pp. 1-25, 2013.

- N. Dahir, T. Mak, R. Al-Dujaily, and A. Yakovlev, *Highly Adaptive* and Deadlock-Free Routing for Three-Dimensional Networks-on-Chip, Institution of Engineering and Technology (IET), Computers & Digital Techniques (CDT), 7:255-263, Nov. 2013.

- N. Dahir, T. Mak, F. Xia, and A. Yakovlev, *Power Supply Noise Minimization by Activity-Aware Mapping in Networks-on-Chip*, (revision submitted), IEEE Transactions on Parallel and Distributed Systems (TPDS), pp. 1-14, 2013.

- R. Al-Dujaily, N. Dahir, T. Mak, F. Xia, and A. Yakovlev. *Dynamic Programming-based Runtime Thermal Management (DPRTM): An On-line Thermal Control Strategy for 3D-NoC Systems*, ACM Transactions on Design Automation of Electronic Systems (TODAES), vol. 19, issue 1, article 2, pp. 1-28, December 2013.

#### Conference publications:

- N. Dahir, T. Mak, and A. Yakovlev, *Communication Centric On-Chip Power Grid Models for Networks-on-Chip*, In VLSI and Systemon-Chip (VLSI-SoC), 2011 IEEE/IFIP 19th International Conference on, pp. 180-183, 2011.

- N. Dahir, T. Mak, F. Xia, and A. Yakovlev, *Minimizing Power* Supply Noise Through Harmonic Mappings in Networks-on-Chip, In Proceedings of the eighth IEEE/ACM/IFIP international conference on Hardware/software codesign and system synthesis, CODES+ISSS'12, pp. 113-122, New York, NY, USA, 2012.

3. N. Dahir, G. Tarawneh, T. Mak, R. Al-Dujaily and A. Yakovlev, Design and Implementation of Dynamic Thermally-Adaptive Routing Strategy for Networks-on-Chip, In Parallel, Distributed and Network-Based Processing (PDP), 2014 22nd Euromicro International Conference on, Turin-Italy, 12-14 Feb. 2014.

#### Workshop and forum publications:

- N. Dahir, R. Al-Dujaily, A. Yakovlev, P. Missailidis, and T. Mak. Deadlock-free and plane-balanced adaptive routing for 3D networkson-chip, In Proceedings of the Fifth International Workshop on Network on Chip Architectures, NoCArc'12, pages 31-36, New York, NY, USA, 2012. ACM.

- N. Dahir, T. Mak and A. Yakovlev, Adaptive Run-Time Thermal Balancing in 3D Network-on-Chip Systems Using Dynamic Programming Networks, Proceedings of UK Electronics Forum (UKEF'12), Newcastle, 30-31th Aug. 2012, pp. 1 - 6.

- 3. **N. Dahir**, T. Mak and A. Yakovlev, *Networks-On-Chip Workload Impact on Power Delivery Grid*, Proceedings of UK Electronics Forum (UKEF'11), Manchester, 4-5th July, 2011, pp. 6 - 12.

#### I also contributed in the following works:

- A. Karkar, N. Dahir, K. Tong, R. Al-Dujaily, A. Yakovlev, and T. Mak, *Hybrid Wire-Surface Wave Architecture for One-to-Many Communication in Network-on-Chip*, In Proceedings of the conference on Design, automation and test in Europe, DATE'14, Dresden-Germany, 24-28 Mar. 2014.

- H. Alrudainy, N. Dahir, A. Mokhov, A. Yakovlev, A Scalable Physical Model for Nano-Electro-Mechanical Relays, Design automation conference, DAC'14, San Francisco, CA, 1-5 June 2014

| I | Τł  | nesis C | Chapters                                          | 1        |

|---|-----|---------|---------------------------------------------------|----------|

| 1 | INT | RODUC   | TION                                              | 2        |

|   | 1.1 | Motiv   | vation                                            | 2        |

|   | 1.2 |         | s Contributions                                   | 4        |

|   | 1.3 | Thesis  | s Layout                                          | 6        |

| 2 | BAC | KGROU   | JND AND LITERATURE REVIEW                         | 8        |

|   | 2.1 | Introc  | luction                                           | 8        |

|   | 2.2 | Backg   | ground                                            | 8        |

|   |     | 2.2.1   | Networks-on-Chip                                  | 8        |

|   |     | 2.2.2   | NoC Topology                                      | 9        |

|   |     | 2.2.3   | NoC Components                                    | 9        |

|   |     | 2.2.4   | Flow Control                                      | 13       |

|   |     | 2.2.5   | Routing Algorithms                                | 15       |

|   |     | 2.2.6   | NoCs in Three Dimensional ICs                     | 19       |

|   | 2.3 | Litera  | ture Review                                       | 21       |

|   |     | 2.3.1   | Evolution of NoCs                                 | 21       |

|   |     | 2.3.2   | Application Mapping                               | 22       |

|   |     | 2.3.3   | Router Design and Routing Algorithms              | 24       |

|   |     | 2.3.4   | NoC Architectures and Design Philosophies         | 28       |

|   |     | 2.3.5   | NoC Models and Simulators                         | 32       |

| 3 | моі | DELLIN  | IG AND ANALYSIS OF POWER SUPPLY VARIATION         | 15       |

|   | IN  | NOCS    |                                                   | 36       |

|   | 3.1 | Introc  | luction                                           | 36       |

|   | 3.2 | Relate  | ed Work and Background                            | 38       |

|   |     | 3.2.1   | Power Grid Modelling and Analysis                 | 39       |

|   |     | 3.2.2   | Workload Modelling                                | 40       |

|   | 3.3 | Metho   | odology                                           | 41       |

|   |     | 3.3.1   | Power Noise in Networks-on-Chip                   | 42       |

|   |     | 3.3.2   | Compartmental Modelling for Communication         |          |

|   |     |         | Fabrics                                           | 43       |

|   |     | 3.3.3   | Power Grid Granularity                            | 48       |

|   | 3.4 |         | rimental Results and Discussion                   | 49       |

|   |     | 3.4.1   | Experimental Setup                                | 49       |

|   |     | 3.4.2   | Model Verification                                | 50       |

|   |     | 3.4.3   | Granularity Analysis                              | 50       |

|   |     | 3.4.4   | Synthetic traffic patterns and Routing Algorithms | <u> </u> |

|   |     |         | 52                                                |          |

|   |     | 3.4.5   | Real Traffic                                      | 55       |

|   | 3.5         | Case           | Study: Power Supply-Aware Timing Analysis       | 56         |

|---|-------------|----------------|-------------------------------------------------|------------|

|   |             | 3.5.1          | Impact of Power Supply Variations on Link Delay | 56         |

|   |             | 3.5.2          | Probability of Timing Violation Errors and Bit  |            |

|   |             |                | Error Rates                                     | 58         |

|   | 3.6         | Sumn           | nary and Conclusion                             | 61         |

|   |             |                |                                                 | _          |

| 4 |             |                | PPLY NOISE MINIMIZATION THROUGH MAPPING         |            |

|   |             | NOCS           | de ation                                        | 63         |

|   | 4.1         |                | duction                                         | 63         |

|   | 4.2         |                | ed Work and Background                          | 64         |

|   |             | 4.2.1          | Related Work and Motivation                     | 64         |

|   |             | 4.2.2          | Background and Definitions                      | 66         |

|   | 4.3         |                | odology                                         | 69         |

|   |             | 4.3.1          | Local and Regional Activity Densities           | 69         |

|   |             | 4.3.2          | Power Supply Noise Optimization                 | 70         |

|   |             | 4.3.3          | Problem Formulation                             | 72         |

|   |             | 4·3·4          | Simulated Annealing-Based Solution              | 73         |

|   | 4.4         | -              | rimental Analysis and Results                   | 75         |

|   |             | 4.4.1          | Experimental Setup                              | 75         |

|   |             | 4.4.2          | Activity Density and Power Supply Noise         | 75         |

|   |             | 4.4.3          | Mapping Results                                 | 77         |

|   |             | 4.4.4          | Impact on Performance                           | 79         |

|   |             | 4.4.5          | Impact of Technology Scaling                    | 81         |

|   |             | 4.4.6          | Evaluation of Link Timing Variations and BER.   | 82         |

|   | 4.5         | Sumn           | nary and Conclusion                             | 85         |

| 5 | DYN         | AMIC           | THERMAL OPTIMIZATION IN 3D NOCS                 | 87         |

|   | 5.1         |                | duction and Motivation                          | 87         |

|   | 5.2         |                | ed Work                                         | 89         |

|   | 5.3         |                | em Definition and Background                    | 91         |

|   | 55          | 5.3.1          | Thermal Optimization and Management             | 91         |

|   |             | 5.3.2          | Temperature-Related Faults                      | 91         |

|   | 5.4         |                | Based Thermal Optimization in 3D NoCs           | 93         |

|   | J- <b>T</b> | 5.4.1          | Shortest Path Computation using Dynamic Pro-    | ))         |

|   |             | J- <b>-</b>    | gramming                                        | 93         |

|   |             | 5.4.2          | DPN Guided 3D NoC Routing                       | 95         |

|   |             | 5.4.3          | Deadlock-Freeness and Adaptiveness              | 97         |

|   |             | 5.4.4          | Coupling DP with 3D-NoC                         | 97<br>102  |

|   |             | 5.4.5          | DP-Network Convergence Time and Complexity      | 103        |

|   | 5.5         |                | mic Thermal Modelling for 3-D NoCs              | 103        |

|   | ر.ر         | 5.5.1          | Traffic Model                                   | 104        |

|   |             | 5.5.2          | Area and Power Model                            | 104        |

|   |             |                | Thermal Model                                   |            |

|   | 5.6         | 5.5.3<br>Resul | ts and Discussion                               | 105<br>106 |

|   | 5.0         | 5.6.1          | Experimental Setup and Tools                    | 100        |

|   |             | 5.6.2          | Temperature Results                             | 100        |

|   |             | 5.6.2<br>5.6.3 | Reliability Improvement                         |            |

|   |             | 5.0.3          |                                                 | 110        |

|              |     | 5.6.4 Performance Results                        | 111 |

|--------------|-----|--------------------------------------------------|-----|

|              |     | 5.6.5 Real Application Benchmarks                | 112 |

|              |     | 5.6.6 Hardware Implementation                    | 118 |

|              | 5.7 | Summary and Conclusion                           | 121 |

| 6            | FPG | A IMPLEMENTATION OF THERMAL-ADAPTIVE ROUT-       |     |

|              | ING | IN NOCS                                          | 123 |

|              | 6.1 | Introduction and Motivation                      | 123 |

|              | 6.2 | Related Work                                     | 124 |

|              | 6.3 | Background                                       | 126 |

|              |     | 6.3.1 Thermal Optimization and Management        | 126 |

|              |     | 6.3.2 On-Chip Thermal Sensing                    | 126 |

|              | 6.4 | Methodology                                      | 127 |

|              |     | 6.4.1 Thermal-Adaptive Dynamic Routing in NoCs . | 127 |

|              |     | 6.4.2 Deadlock and Livelock Freeness             | 129 |

|              |     | 6.4.3 Thermal-Aware DP Network Implementation .  | 130 |

|              |     | 6.4.4 DPN Convergence                            | 132 |

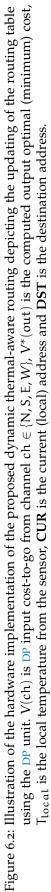

|              |     | 6.4.5 On-chip Thermal Sensing Implementation     | 133 |

|              | 6.5 | Results and Discussion                           | 135 |

|              |     | 6.5.1 Functional Verification Results            | 136 |

|              |     | 6.5.2 Spatial Thermal Regulation Results         | 139 |

|              |     | 6.5.3 Temporal Thermal Regulation Results        | 139 |

|              |     | 6.5.4 Performance Evaluation                     | 141 |

|              |     | 6.5.5 Hardware Evaluation                        | 142 |

|              | 6.6 | Summary and Conclusion                           | 143 |

| 7            | CON | ICLUSIONS AND FUTURE WORK                        | 145 |

|              | 7.1 | Summary and Conclusion                           | 145 |

|              | 7.2 | Future Work                                      | 147 |

|              | -   |                                                  |     |

| 11           | Th  | nesis Appendices                                 | 148 |

| Α            | THE | RMAL MATERIAL PARAMETERS                         | 149 |

| в            | DET | AILS OF POWER DELIVERY PARAMETERS AND TECH-      |     |

|              |     | LOGY SCALING                                     | 151 |

|              | B.1 | Setup                                            | 151 |

|              | B.2 | Scaling Parameters                               | 151 |

| 111          | Τh  | iesis Bibliography                               | 152 |

|              |     |                                                  |     |

| BIBLIOGRAPHY |     |                                                  | 153 |

### LIST OF FIGURES

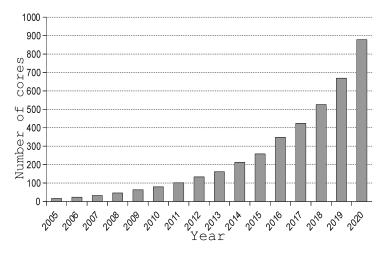

| Figure 1.1               | Expected number of processing elements in a system-on-chip (SoC) [103].          | 3  |

|--------------------------|----------------------------------------------------------------------------------|----|

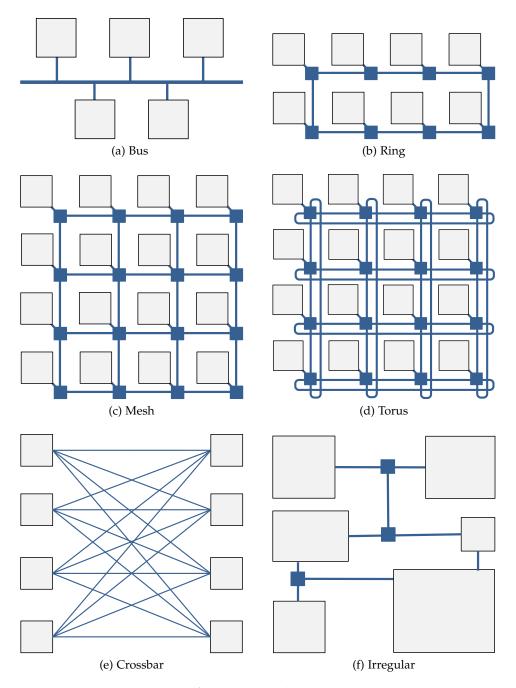

| Figure 2.1               | Examples of common on-chip network topologies.                                   | 10 |

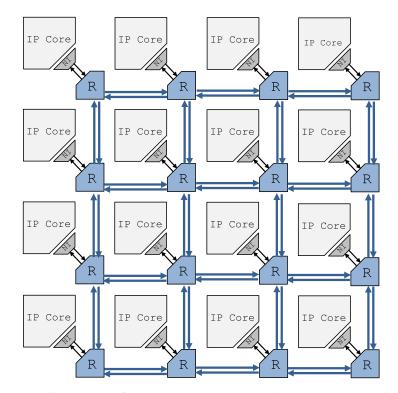

| Figure 2.2               | Illustration of components in a 2D mesh NoC.<br>NI: Network Interface, R: Router | 11 |

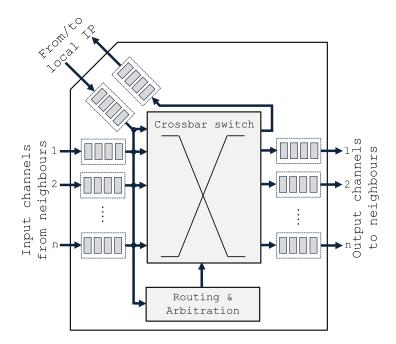

| Figure 2.2               | Illustration of NoC router microarchitecture [66].                               | 11 |

| Figure 2.3<br>Figure 2.4 | Illustration of $NoC$ flow control units of different                            | 12 |

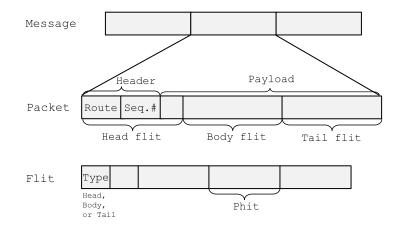

| rigure 2.4               | granularities [109].                                                             | 14 |

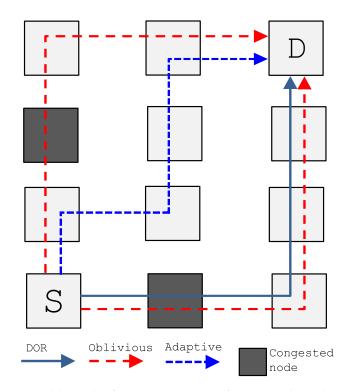

| Figure 2.5               | Possible paths for various types of routing algo-                                |    |

| 0 9                      | rithms for a 2D mesh, dimension-ordered rout-                                    |    |

|                          | ing (DOR) show the path for X-Y routing while                                    |    |

|                          | Oblivious alternates between X-Y and Y-X paths                                   |    |

|                          | between a source, S, and a destination, D. For                                   |    |

|                          | Adaptive routing an example of a possible path                                   |    |

|                          | that avoids congestion is illustrated                                            | 16 |

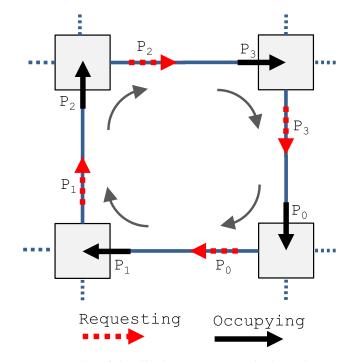

| Figure 2.6               | An example of deadlock scenario in which pack-                                   |    |

| C                        | ets are forming a dependency cycle and cannot                                    |    |

|                          | progress forward because they request channels                                   |    |

|                          | that are occupied by other packets                                               | 17 |

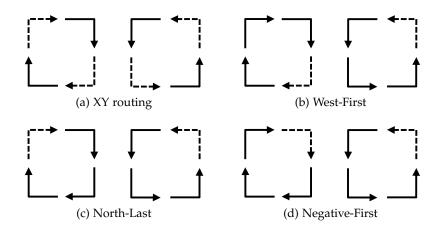

| Figure 2.7               | Allowable and prohibited turns in XY DOR and                                     |    |

| -                        | turn model routing algorithms in a 2D mesh.                                      |    |

|                          | Dashed lines indicate prohibited turns and solid                                 |    |

|                          | lines indicate allowable turns                                                   | 18 |

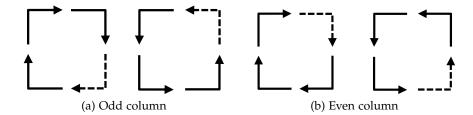

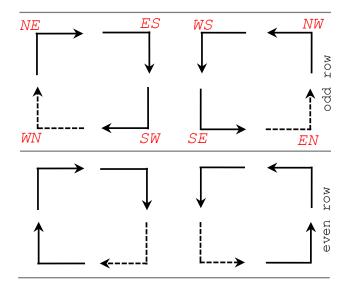

| Figure 2.8               | Allowable and prohibited turns in odd-even turn                                  |    |

|                          | model routing algorithm for odd and even columns                                 |    |

|                          | in a 2D mesh. Dashed lines indicate prohibited                                   |    |

|                          | turns and solid lines indicate allowable turns                                   | 19 |

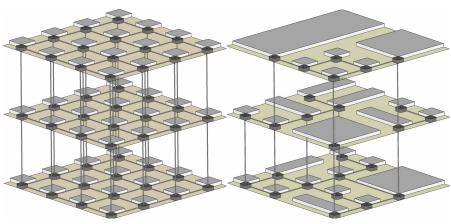

| Figure 2.9               | Homogeneous and heterogeneous 3D mesh NoC                                        |    |

|                          | geometries that uses through-silicon vias (TSVs)                                 |    |

|                          | as vertical interconnects for the stacked layers.                                | 21 |

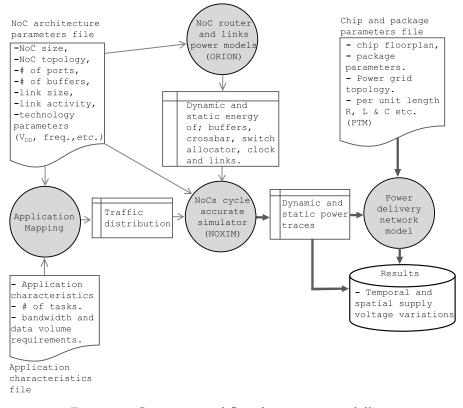

| Figure 3.1               | Computational flow for NoC PSN modelling                                         | 42 |

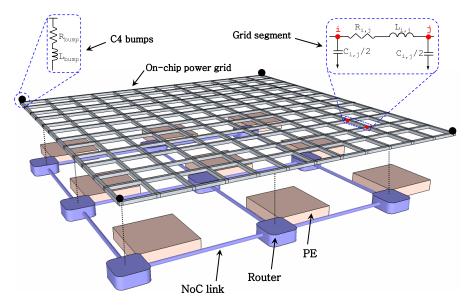

| Figure 3.2               | Illustration of NoC power delivery network and                                   |    |

|                          | its RLC model. $R_{i,j}$ , $L_{i,j}$ and $C_{i,j}$ are the resis-                |    |

|                          | tance, inductance and capacitance of gird wire                                   |    |

|                          | segment between nodes i and j. $R_{bump}$ and                                    |    |

|                          | $L_{bump}$ are resistance and inductance of the C4                               |    |

|                          | bumps                                                                            | 43 |

|                          |                                                                                  |    |

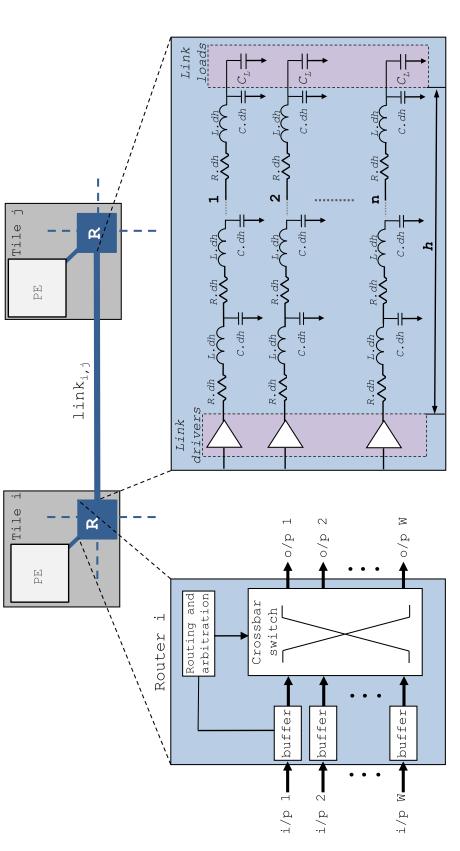

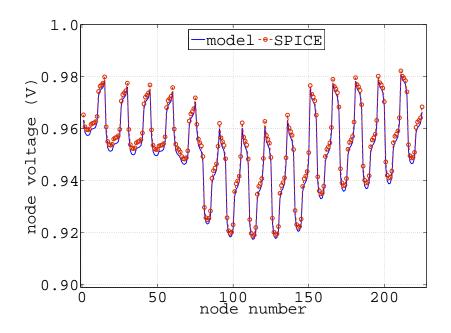

| Figure 3.3  | Illustration of the modelled NoC components in-<br>cluding the routers connecting tiles i and j, with |          |

|-------------|-------------------------------------------------------------------------------------------------------|----------|

|             | the router functional components, and NoC link,                                                       |          |

|             | with its equivalent circuit assuming that router i                                                    |          |

|             | is sending and router j is receiving. n: number                                                       |          |

|             | of wires in the link, h: link length, W: number                                                       |          |

|             | channels in the router.                                                                               | 46       |

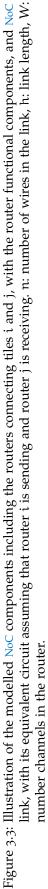

| Figure 3.4  | Illustration of the mapping from a fine-grained                                                       | 40       |

| Figure 3.4  | to a coarse-grained model of the power delivery                                                       |          |

|             | grid                                                                                                  | 49       |

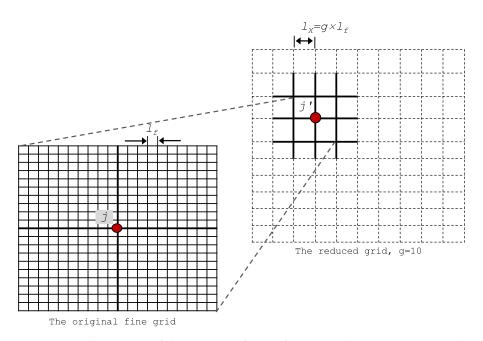

| Figure 3.5  | Comparison of node voltages computed by the                                                           |          |

|             | proposed model with SPICE simulation for a                                                            |          |

|             | $3 \times 3$ NoC configuration                                                                        | 51       |

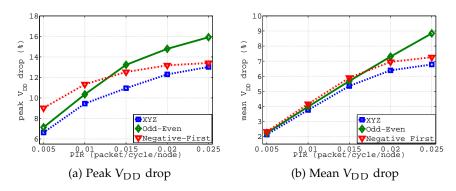

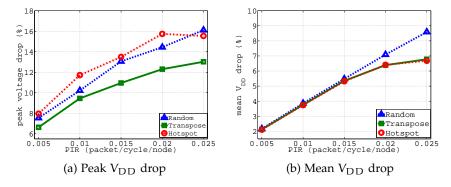

| Figure 3.6  | V <sub>DD</sub> drop versus packet injection rate (PIR) for                                           |          |

|             | various routing algorithms                                                                            | 52       |

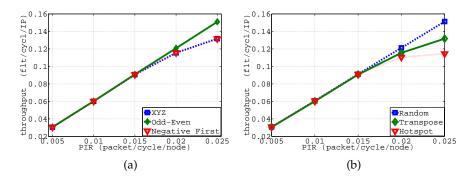

| Figure 3.7  | $V_{DD}$ drop versus PIR for various traffic patterns .                                               | 52       |

| Figure 3.8  | Throughput for different (a) routing algorithms,                                                      |          |

|             | and (b) traffic patterns                                                                              | 53       |

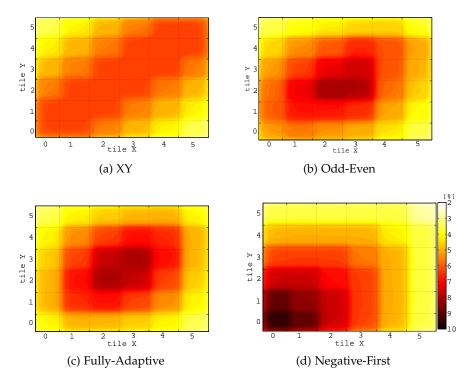

| Figure 3.9  | Spatial distribution of mean $V_{DD}$ drop (%) for                                                    |          |

| 0           | different routing algorithms and Transpose traffic.                                                   | 54       |

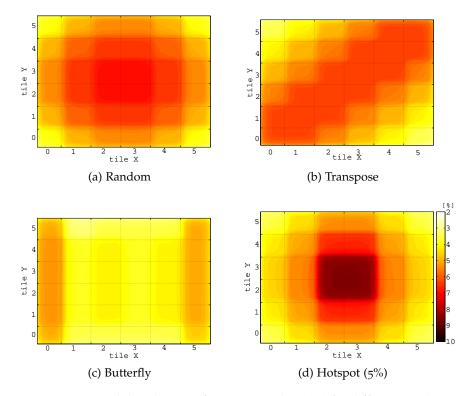

| Figure 3.10 | Spatial distribution of mean $V_{DD}$ drop (%) for                                                    |          |

| 0 0         | different synthetic traffic patterns with XY routing.                                                 | 55       |

| Figure 3.11 | Spatial distribution of mean V <sub>DD</sub> drop (%) for                                             |          |

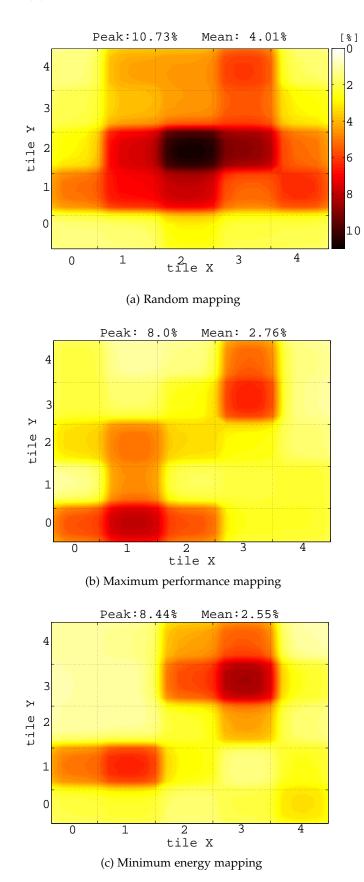

| 0 0         | the MMS application traffic with three mapping                                                        |          |

|             | strategies.                                                                                           | 57       |

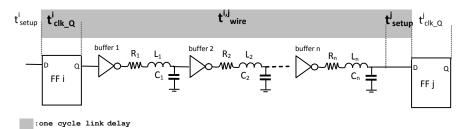

| Figure 3.12 | A model of on-chip link illustrating the delay                                                        |          |

| 0 9         | components and timing constrains [158]                                                                | 58       |

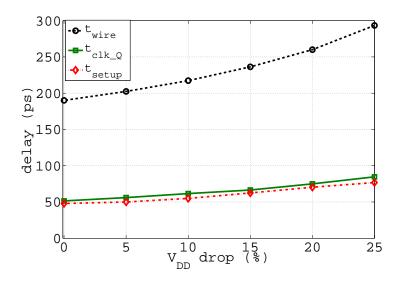

| Figure 3.13 | The $t_{wire}$ , $t_{clk_Q}$ and $t_{setup}$ link delays versus                                       |          |

| 0 9 9       | $V_{DD}$ drop                                                                                         | 59       |

| Figure 3.14 | Links delay statistics for the MMS benchmark                                                          | <i>」</i> |

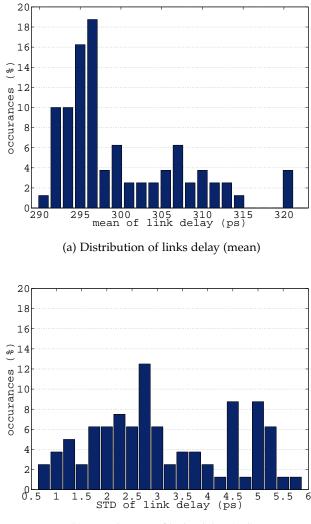

| 0 5 1       | using maximum performance mapping                                                                     | 61       |

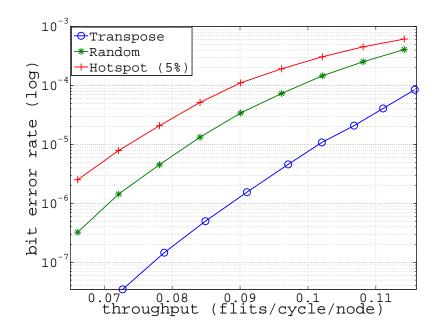

| Figure 3.15 | Bit error rate versus throughput for various syn-                                                     |          |

| 0           | thetic traffic patterns                                                                               | 62       |

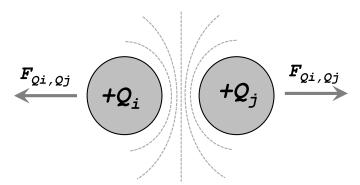

| Figure 4.1  | Illustration of tile repulsive force.                                                                 | 71       |

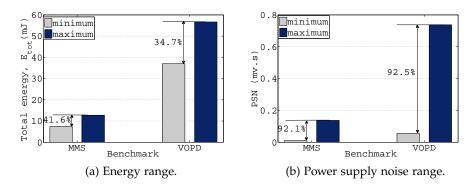

| Figure 4.2  | Energy and PSN ranges for two benchmarks with                                                         | /-       |

|             | random mapping. Different mappings can have                                                           |          |

|             | effects on PSN. Similar results are found for other                                                   |          |

|             | benchmarks.                                                                                           | 75       |

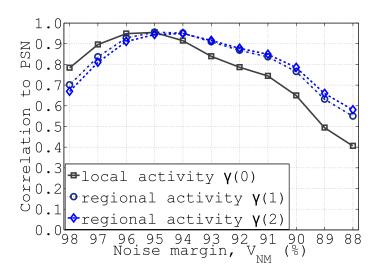

| Figure 4.3  | Correlation of PSN and activity density. Results                                                      | 15       |

|             | from 100 random mappings for the VOPD bench-                                                          |          |

|             | mark. A significant correlation between PSN and                                                       |          |

|             | 5                                                                                                     |          |

|             | activity density can be seen, which is higher for                                                     | -6       |

|             | regional activity than local activity                                                                 | 76       |

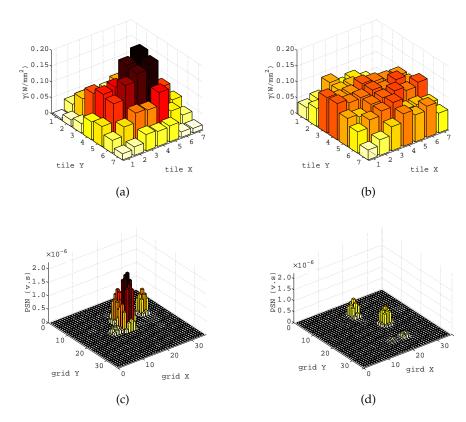

| Figure 4.4 | Illustration of the proposed mapping results: The spatial distribution of activity density and PSN |   |

|------------|----------------------------------------------------------------------------------------------------|---|

|            | for the AMI49 application. Significant reduction                                                   |   |

|            | in PSN is achieved by uniform distribution of ac-                                                  |   |

|            | tivity. a) Activity density ( $\gamma$ ) for min. E <sub>tot</sub> map-                            |   |

|            | ping, b) Activity density $(\gamma)$ for the proposed                                              |   |

|            | min. $F_{tot}$ mapping, c) PSN for min. $E_{tot}$ map-                                             |   |

|            | ping, d) PSN for the proposed min. $F_{tot}$ mapping 7                                             | 8 |

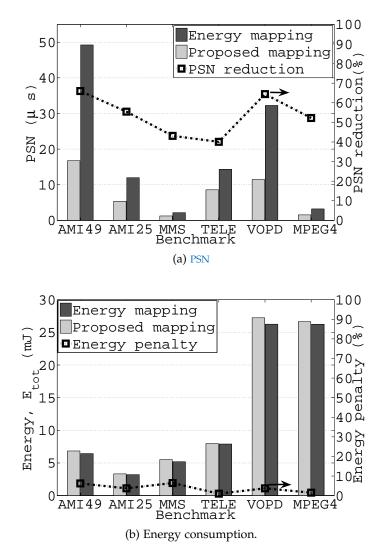

| Figure 4.5 | Comparison of PSN and energy optimizations.                                                        |   |

| 11guie 4.9 | Our noise minimization could achieve significant                                                   |   |

|            | reductions in PSN compared to energy minimiza-                                                     |   |

|            | tion, with a low energy penalty.                                                                   | 0 |

| Figure 16  | Evaluation of the proposed mapping with dif-                                                       | 0 |

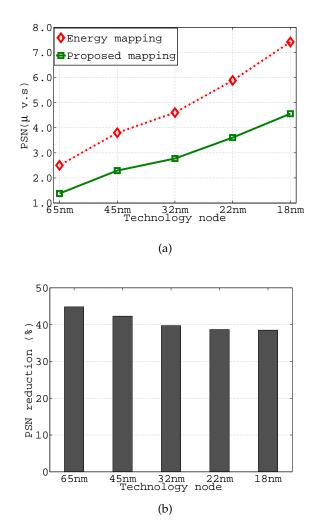

| Figure 4.6 |                                                                                                    |   |

|            | ferent technology nodes: a) PSN for both the pro-                                                  |   |

|            | posed (min{ $F_{tot}$ }) mapping and energy (min{ $E_{tot}$ })                                     |   |

|            | mapping and; b) the percentage reduction in                                                        |   |

|            | PSN, for the MMS benchmark with different tech-                                                    |   |

| <b></b>    | nology nodes                                                                                       | 2 |

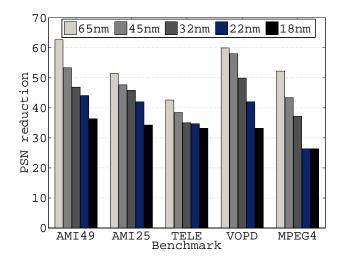

| Figure 4.7 | The reduction in PSN achieved by the proposed                                                      |   |

|            | $(\min{F_{tot}})$ mapping compared to energy $(\min{E_{tot}})$                                     | ) |

|            | mapping for various benchmarks with different                                                      |   |

|            | technology nodes                                                                                   | 3 |

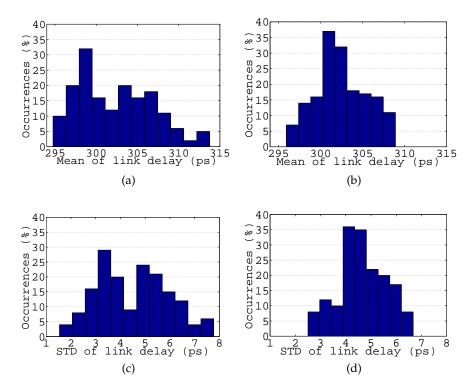

| Figure 4.8 | Comparison of link delay statistics for the AMI49                                                  |   |

|            | benchmark with both $min{E_{tot}}$ and the pro-                                                    |   |

|            | posed (min{F <sub>tot</sub> }) mappings. Mean of delay with;                                       |   |

|            | a) energy mapping; b) proposed (min{F <sub>tot</sub> }) map-                                       |   |

|            | ping, and STD of delay with; c) energy mapping;                                                    |   |

|            | d) proposed (min{ $F_{tot}$ }) mapping 8                                                           | 4 |

| Figure 5.1 | Illustration of thermal-aware routing paths 8                                                      | 8 |

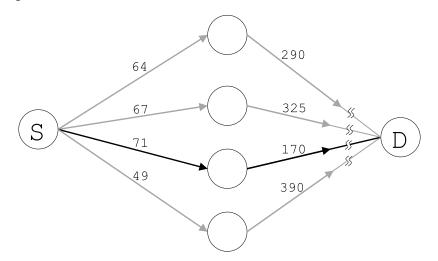

| Figure 5.2 | Illustration of finding the shortest path in a                                                     |   |

|            | graph: a straight line indicates a single edge;                                                    |   |

|            | a discontinuous line indicates a shortest path                                                     |   |

|            | between the two nodes it connects (other nodes                                                     |   |

|            | on these paths are not shown); the bold line is                                                    |   |

|            | the overall shortest path from source, S, to desti-                                                |   |

|            | nation, D                                                                                          | 4 |

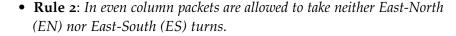

| Figure 5.3 | Illustration of prohibited turns for odd-even rout-                                                |   |

| 0          | ing (rules 1 and 2). Dashed lines represent pro-                                                   |   |

|            | hibited turns.                                                                                     | 8 |

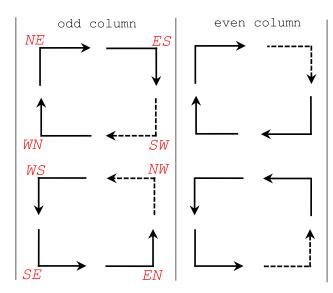

| Figure 5.4 | Illustration of prohibited vertical turns for the                                                  |   |

| 0 0        | 3D odd-even routing (rule 3)                                                                       | 9 |

| Figure 5.5 | Illustration of prohibited turns in modified odd-                                                  |   |

| 0          | even routing (rules 4 and 5)                                                                       | 0 |

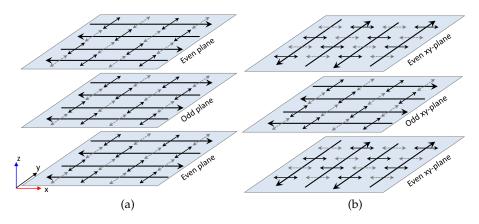

| Figure 5.6 | Illustration of path diversities for both, (a) con-                                                |   |

| 0 2        | ventional 3D odd-even, and (b) the proposed                                                        |   |

|            | balanced 3D odd-even                                                                               | 1 |

|            |                                                                                                    |   |

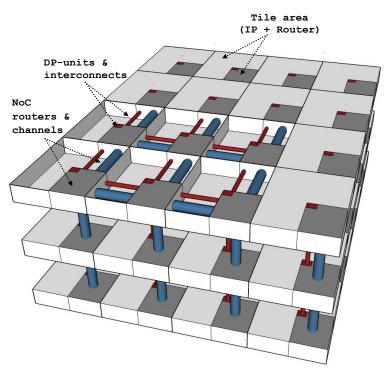

| Figure 5.7           | A 3D mesh NoC with dynamic programming net-                                                            |

|----------------------|--------------------------------------------------------------------------------------------------------|

|                      | work (DPN) for coupled                                                                                 |

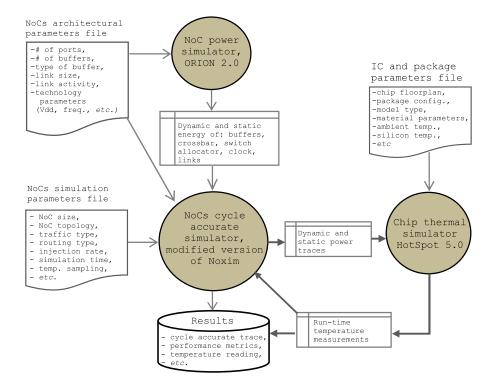

| Figure 5.8           | Automated computational flow of the proposed                                                           |

|                      | tool for dynamic thermal optimization for 3D NoC.104                                                   |

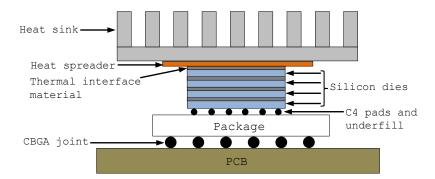

| Figure 5.9           | Illustration of various layers in a typical ceramic                                                    |

|                      | ball grid array (CBGA) package of a 3D IC with                                                         |

|                      | four layers [96]                                                                                       |

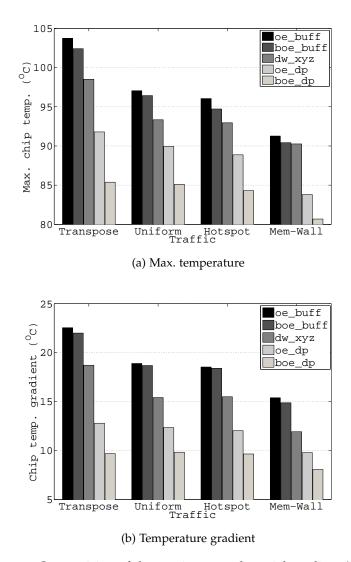

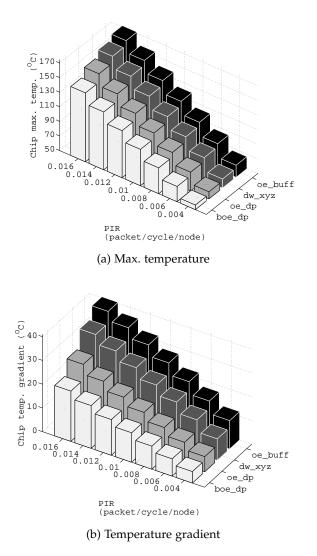

| Figure 5.10          | Comparision of the maximum and spatial gra-                                                            |

| 0                    | dient (minmax.) of chip temperature for the                                                            |

|                      | considered routing strategies with various traffic                                                     |

|                      | scenarios                                                                                              |

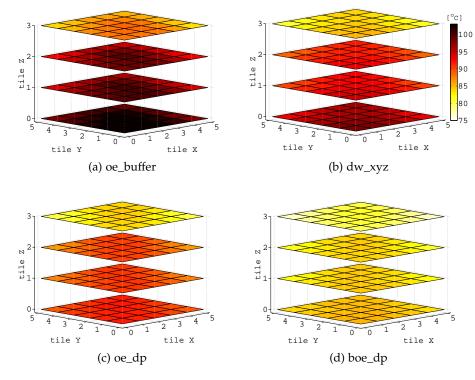

| Figure 5.11          | Spatial thermal distributions (°C) for the four                                                        |

| 0 5                  | routing strategies                                                                                     |

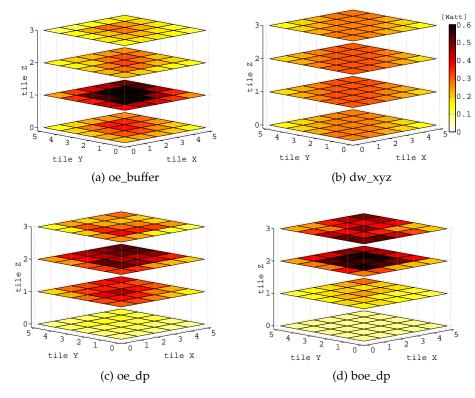

| Figure 5.12          | Spatial power distributions (W) for the four rout-                                                     |

| 0 9                  | ing strategies                                                                                         |

| Figure 5.13          | Maximum and gradient (minmax.) of chip tem-                                                            |

| 0 9 9                | perature variation with PIR for the four routing                                                       |

|                      | strategies with Transpose traffic                                                                      |

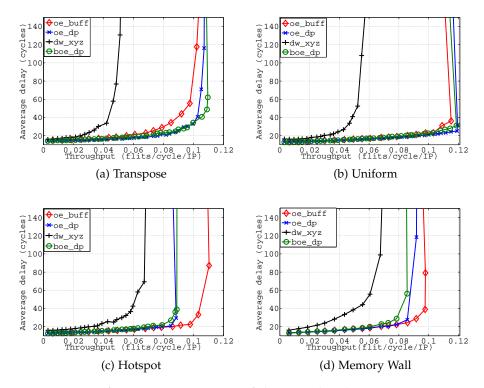

| Figure 5.14          | Performance comparison of the considered rout-                                                         |

|                      | ing strategies in terms of delay versus through-                                                       |

|                      | put curves for different traffic scenarios 114                                                         |

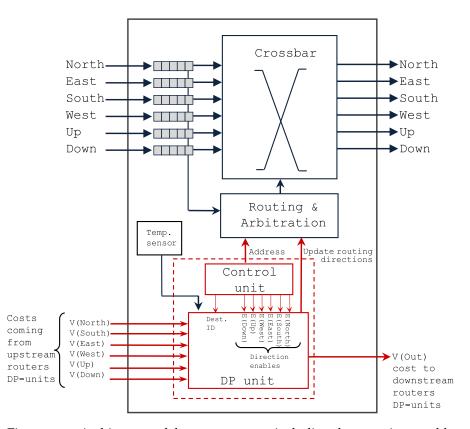

| Figure 5.15          | Architecture of the <sub>3</sub> D N <sub>o</sub> C router including the                               |

| i iguie j.i j        | DP unit to enable dynamic thermal-aware routing.119                                                    |

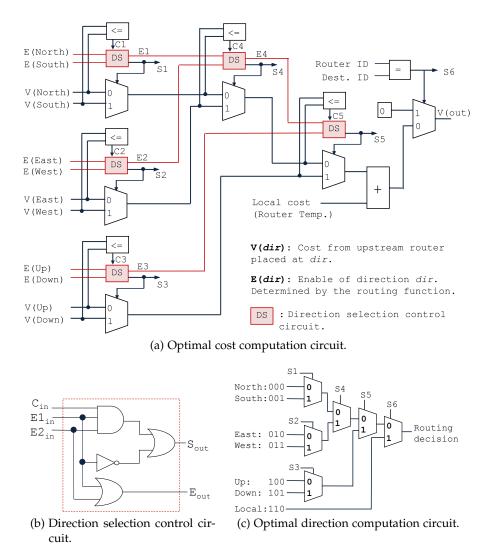

| Figure 5.16          | Hardware realization of the DP unit                                                                    |

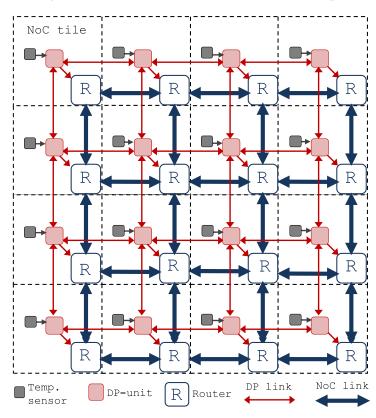

| Figure 6.1           | Dynamic programming network and tempera-                                                               |

| Figure 0.1           | ture sensor array coupled to a 2D mesh NoC 128                                                         |

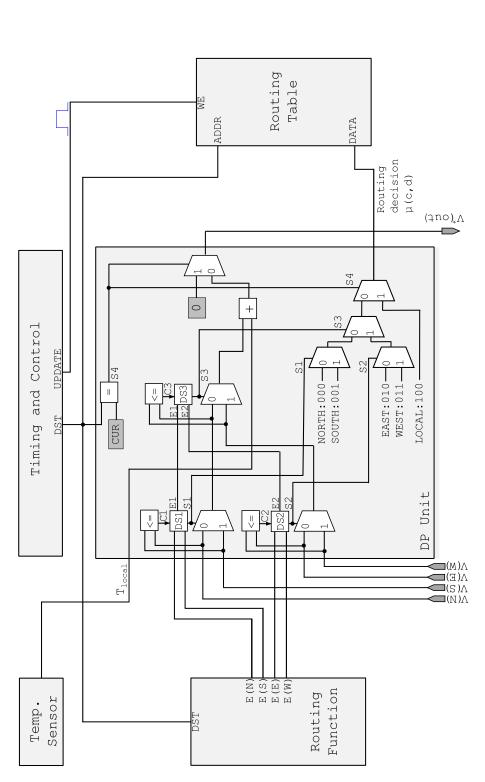

| Figure 6 a           | Illustration of the hardware implementation of                                                         |

| Figure 6.2           | the proposed dynamic thermal-aware routing                                                             |

|                      |                                                                                                        |

|                      | depicting the updating of the routing table us-<br>ing the DD upit $V(ab)$ is DD input soft to go from |

|                      | ing the DP unit. V(ch) is DP input cost-to-go from                                                     |

|                      | channel ch $\in$ {N, S, E, W}, V*(out) is the com-                                                     |

|                      | puted output optimal (minimum) cost, T <sub>local</sub>                                                |

|                      | is the local temperature from the sensor, <b>CUR</b>                                                   |

|                      | is the current (local) address and <b>DST</b> is the                                                   |

| Eigenera (           | destination address                                                                                    |

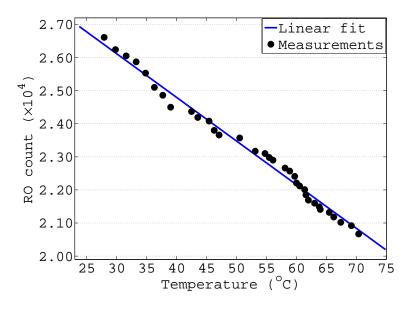

| Figure 6.3           | Ring oscillator-based thermal sensing components.134                                                   |

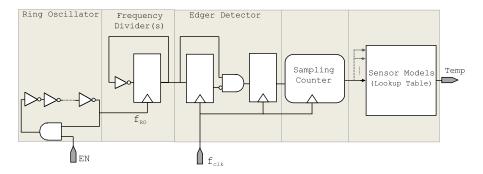

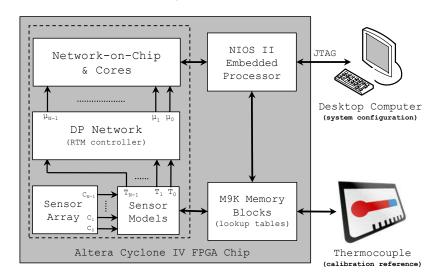

| Figure 6.4           | Illustration of the FPGA implementation of the                                                         |

|                      | NoC thermal characterization system used to ob-                                                        |

|                      | tain the experimental results. $\mu_i$ is the routing                                                  |

|                      | decisions for node i, $C_i$ is the count output for                                                    |

|                      | sensor i, and $T_i$ is the temperature output for                                                      |

| <b>D·</b> <i>· ·</i> | sensor i                                                                                               |

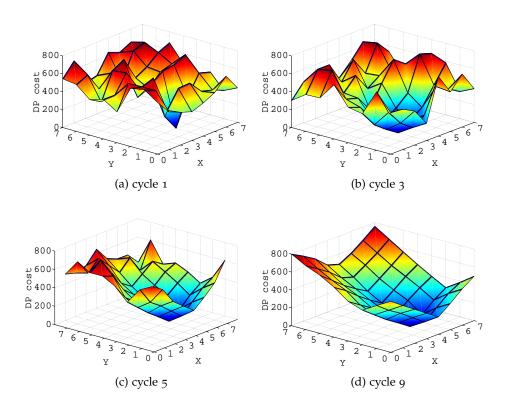

| Figure 6.5           | Illustration of DPN cost-to-go convergence at dif-                                                     |

|                      | ferent DPN cost computation phases for destina-                                                        |

| <b>TI i i i</b>      | tion 20                                                                                                |

| Figure 6.6           | Illustration of sensor accuracy                                                                        |

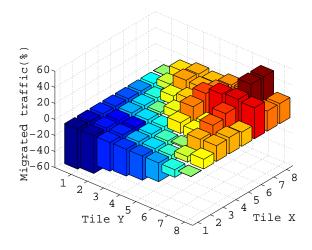

| Functional verification results: the DPN responds        |                                                                                                                                                                                                                            |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| to a chip thermal gradient by migrating traffic          |                                                                                                                                                                                                                            |

| to the cooler region in the chip                         | 138                                                                                                                                                                                                                        |

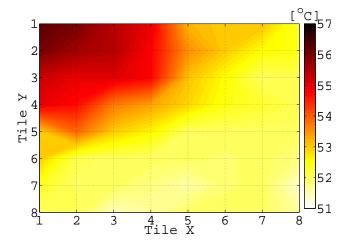

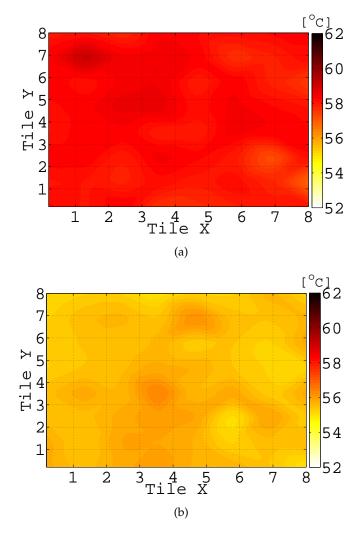

| Example illustrating the chip spatial temperature        |                                                                                                                                                                                                                            |

| distributions for <i>Transpose1</i> traffic with both a) |                                                                                                                                                                                                                            |

| BL and b) <b>DP</b> routings                             | 140                                                                                                                                                                                                                        |

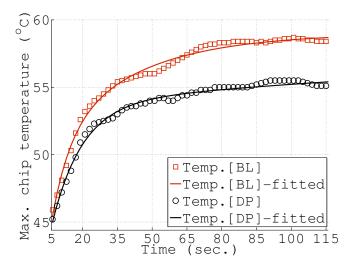

| Chip heating versus time: maximum tempera-               |                                                                                                                                                                                                                            |

| ture for <i>Transpose1</i> traffic with both BL routing  |                                                                                                                                                                                                                            |

| and thermally adaptive DP routing                        | 141                                                                                                                                                                                                                        |

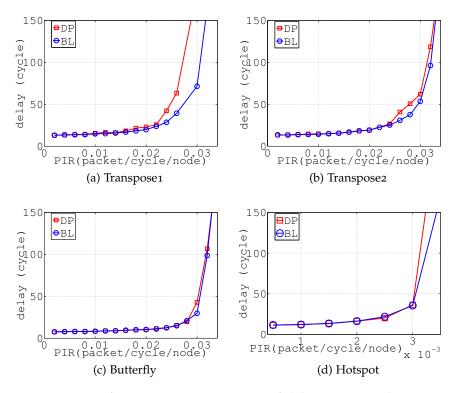

| Performance curves in terms of delay versus              |                                                                                                                                                                                                                            |

| packet injection rate (PIR) for both DP and BL           | 143                                                                                                                                                                                                                        |

|                                                          | to a chip thermal gradient by migrating traffic<br>to the cooler region in the chip Example illustrating the chip spatial temperature<br>distributions for <i>Transpose1</i> traffic with both a)<br>BL and b) DP routings |

## LIST OF TABLES

| Table 2.1 | Comparison of various NoC application mapping works.                              | 26 |

|-----------|-----------------------------------------------------------------------------------|----|

| Table 2.2 | Comparison of various NoC models and simulators.                                  | 33 |

| Table 3.1 | Notation and symbols used in this chapter                                         | 44 |

| Table 3.2 | Comparison of the proposed model with dif-                                        |    |

| 9         | ferent power grid granularities with the SPICE                                    |    |

|           | simulation of a fine granularity.                                                 | 51 |

| Table 3.3 | Summary of V <sub>DD</sub> drop (%). Results of four dif-                         | 2  |

|           | ferent routing algorithms and three traffic patterns.                             | 54 |

| Table 4.1 | Definitions and notation used in this chapter.                                    | 67 |

| Table 4.2 | Summary of the benchmarks. GD is the graph                                        |    |

|           | connection density and is defined as $GD = \frac{2 A }{ S ( S -1) }$              | ×  |

|           | 100%, while the $\overline{BW}$ is the average communica-                         |    |

|           | tion bandwidth among the task graphs and is                                       |    |

|           | defined as $\overline{BW} = \left(\sum_{\forall a \in \{A\}} b(a)\right) /  A $ . | 77 |

| Table 4.3 | Summary of mapping results in terms of the                                        |    |

|           | total PSN and energy consumption for both min-                                    |    |

|           | imum energy mapping, $min\{E_{tot}\}$ , and the pro-                              |    |

|           | posed minimum total repulsive force , $min{F_{tot}}$ .                            | 79 |

| Table 4.4 | Performance comparison of the two mappings                                        |    |

|           | showing time required for draining 5MB of data                                    |    |

|           | for each application and using the proposed                                       |    |

|           | mapping and energy-aware mapping strategies.                                      |    |

|           | Percentage difference between the two mappings                                    |    |

|           | are also shown.                                                                   | 81 |

| Table 4.5 | The resulting bit error rate (BER) reduction achieved                             |    |

|           | by the proposed mapping strategy compared to                                      |    |

|           | energy mapping for various real benchmarks                                        | 85 |

| Table 5.1 | Comparison of failures-in-time (FIT) due to dif-<br>ferent fault mechanisms for the four routing          |     |

|-----------|-----------------------------------------------------------------------------------------------------------|-----|

|           | strategies and different traffic patterns for a $6 \times$                                                |     |

|           | $6 \times 4_{3D}$ NoC configuration.                                                                      | 112 |

| Table 5.2 | Achievable performance metrics with different routing algorithms for different thermal limits             |     |

|           | 1                                                                                                         | 115 |

| Table 5.3 | Real benchmarks results. Chip maximum, $T_{max}$ , and gradient, $T_{gradient}$ , of temperature, NoC en- |     |

|           | ergy consumption for dw_xyz [38] and boe_dp                                                               |     |

|           | in addition to the percentage improvement of                                                              |     |

|           |                                                                                                           | 117 |

| Table 5.4 | Synthesis results: Router and DP-unit power and                                                           | 11/ |

| 10010 9.4 | area in addition to DP unit relative overhead.                                                            | 121 |

| Table 6.1 | Results for chip spatial temperature. Maximum                                                             |     |

|           | and range of temperature for both DP routing                                                              |     |

|           | and BL routing with percentage improvement in                                                             |     |

|           | both maximum and range of temperature for the                                                             |     |

|           | four traffic patterns considered . The improve-                                                           |     |

|           | ment is computed after subtracting the initial                                                            |     |

|           |                                                                                                           | 140 |

| Table 6.2 | Results of temporal thermal regulation: Thermal                                                           |     |

|           | time constant, $\tau$ , of chip heating and the num-                                                      |     |

|           | ber of packets delivered within a thermal limit                                                           |     |

|           | of 55°C for both DP and BL routings with the                                                              |     |

|           | percentage improvement of DP over BL                                                                      | 142 |

| Table 6.3 | FPGA implementation results: FPGA resource uti-                                                           |     |

|           | lization of DPN and thermal sensing with the per-                                                         |     |

|           | centage overhead relative to 64 core NoC. Sensing                                                         |     |

|           | hardware include ring oscillator (RO) sensors,                                                            |     |

|           | sensor models and lookup tables                                                                           | 142 |

| Table A.1 | The material parameters used in this work for                                                             |     |

|           | the thermal simulation.                                                                                   | 150 |

| Table B.1 |                                                                                                           | 151 |

| Table B.2 | Technology scaling factors for various parameters.                                                        | 151 |

## LIST OF ALGORITHMS

| 4.1 | Pseudo code of the force-based application mapping for |    |

|-----|--------------------------------------------------------|----|

|     | activity density minimization in NoCs                  | 74 |

| 5.1 | Operations performed by the DP-unit for thermal opti-<br>mization. | 96  |

|-----|--------------------------------------------------------------------|-----|

| 6.1 | Pseudo code of the thermal $DP$ unit algorithm                     | 129 |

## ACRONYMS

| 2D                                       | two-dimensional                           |

|------------------------------------------|-------------------------------------------|

| 3D No                                    | Cs three-dimensional networks-on-chip     |

| 3D NoC three-dimensional network-on-chip |                                           |

| 3D                                       | three-dimensional                         |

| 3D-ICs                                   | three-dimensional integrated circuits     |

| ASIC                                     | application-specific integrated circuit   |

| BE                                       | best effort                               |

| BER                                      | bit error rate                            |

| CMP                                      | chip-multiprocessor                       |

| CMPs                                     | chip multiprocessors                      |

| DOR                                      | dimension-ordered routing                 |

| DP                                       | dynamic programming                       |

| DPN                                      | dynamic programming network               |

| DSP                                      | digital signal processing                 |

| DVFS                                     | dynamic voltage and frequency scaling     |

| FIFO                                     | First-In-First-Out                        |

| FPGA                                     | field-programmable gate array             |

| GALS                                     | globally asynchronous locally synchronous |

| GT                                       | guaranteed service                        |

| ILP                                      | instruction-level parallelism             |

| IP                                       | intellectual property                     |

| IR                                       | resistive                                 |

|                                          |                                           |

MIQP mixed integer quadratic programming

MPSoC multiprocessor system-on-chip

MPSoCs multiprocessor systems-on-chip

MTTF mean-time-to-failure

- NI network interface

- NIs network interfaces

- NoC Network-on-Chip

- NoCs Networks-on-Chip

- NoP Neighbours-on-Path

- OCP Open Core Protocol

OCP-IP open core protocol-international partnership

- PE processing element

- PEs processing elements

- PSN power supply noise

- QoS quality of service

- RF radio frequency

- RO ring oscillator

- RTM run-time thermal management

- SA simulated annealing

- SoC system-on-chip

- SoCs systems-on-chip

- STA statistical timing analysis

- TSVs through-silicon vias

- VCs virtual channels

- VLSI very large scale integration

- MOR model order reduction

- PDN power delivery network

- PIR packet injection rate

- FIT failures-in-time

# Part I

# Thesis Chapters

#### 1.1 MOTIVATION

Continuing technology scaling is enabling the integration of billions of gates in a chip, and Moore's law is expected to hold for the next fifteen years. This rapidly increasing integration density allows hundreds to thousands of intellectual property (IP) cores to be placed in one chip [103]. Placing that many IP cores in one chip comes with many challenges. The major challenge is to provide an efficient and reliable communication fabric among these cores. This communication fabric must provide scalable, reliable and power-efficient on-chip communication. To cope with the communication requirements of these many-core architectures, Network-on-Chip (NoC) is proposed as a modular packet-switched communication paradigm for many-core very large scale integration (VLSI) architectures.

In system-on-chip (SoC), multiprocessor system-on-chip (MPSoC) and chip-multiprocessor (CMP), Networks-on-Chip (NoCs) can tackle many limitations associated with traditional bus-based on-chip interconnections [23]. Moreover, NoCs can provide IP re-usability and the standardization of communication interfaces, such as in the open core protocol-international partnership (OCP-IP) protocol. These characteristics are crucial in delivering industry-standard flexibility and to facilitate the plug and play IP integration which reduces design effort and the time-to-market for future VLSI systems. Notable examples of architectures that have adopted NoCs are Intel's 80-core TeraFLOPS [193], Tilera's TILE64 [183], and MIT's RAW chip [181].

The power budget of NoCs can represent a significant portion of overall chip power and this portion is expected to increase in the future [147]. There are two main reasons for this; technology scaling and the trends in many-core architecture. In terms of technology scaling, there is a significant difference in scaling between metal and silicon. Smaller feature size would cause interconnects to dominate logic in power consumption [104]. This is mainly because shrinking technology node size results in lower power consumption and delay for logic gates whereas interconnects become relatively slower and more power hungry. As a result, interconnect power would take up the majority of total chip power in future technology nodes. Moreover, the majority of interconnects power is dissipated by global interconnects [147, 127], which are part of NoCs.

In terms of architecture, the International Technology Roadmap for Semiconductors (ITRS) predicts that the number of cores that can be placed in a chip will exponentially increase with technology scaling [104], as shown in Fig. 1.1. Moreover, a trend in many-core system microarchitectures favours the integration of many (hundreds or thousands) simple cores over few complex cores [33]. This results in higher performance and provides finer control on these cores with dynamic voltage and frequency scaling (DVFS). However, this will result in lower core complexity and higher core number, which increases communication power consumption relative to computation power. On one hand, this is due to the simplicity of these cores, while on the other hand, a higher number of connected cores increases network communication activity. This is exacerbated by the fact that power management in the network is not preferred since such techniques can lead to a wake up latency which can severely affect performance [33].

Figure 1.1: Expected number of processing elements in a SoC [103].

As a result of the aforementioned factors, many-core VLSI design is moving towards being communication-centric and NoC power dissipation is becoming increasingly significant. Thus, NoCs are responsible not only for higher energy consumption, but also for the unwanted effects associated with high energy dissipation and power density, such as power supply variations, or power supply noise (PSN), and thermal noise. As a result, the modelling, characterization and management of the workload of NoCs taking into account their PSN and thermal impacts in modern many-core systems is becoming increasingly indispensable. This is particularly important for applications with high communication demand, where the network is shown to surpass the cores in varying these physical parameters [170].

High power consumption density is a source of both increased PSN and high temperature in VLSI systems. Moreover, PSN and high temperature are exacerbated by technology scaling due to increased device and switching activity densities [35, 154, 17, 39]. PSN and temperature can severely degrade the performance and reliability of VLSI systems. However, the most prominent impact of PSN is on the delay

of both logic and interconnects [22, 43, 163, 116]. High temperatures can also increase leakage and delay [154, 96]. However, a major impact of high temperature in VLSI systems is to reduce lifetime reliability due to reduced mean-time-to-failure (MTTF) [35, 175]. High temperature is a major challenge for the emerging three-dimensional (3D) system integration or three-dimensional integrated circuits (3D-ICs) in particular.

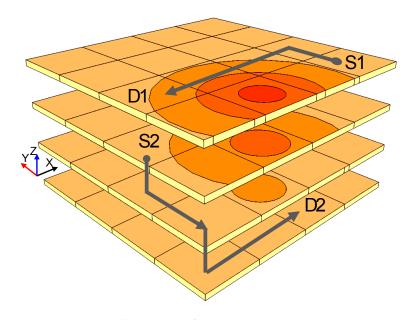

In <sub>3</sub>D system integration, multiple die (or wafer) layers are stacked vertically and connected using through-silicon vias (TSVs). This technology is promising and can increase integration capacity and result in less global interconnects length and delay. In particular, with many-core system integration and NoCs, <u>3D</u> integration enables a massive integration of cores in a chip and <u>3D</u> NoCs are ideal for connecting these cores [204, 167]. <u>3D</u> NoCs can provide high data bandwidth due to their shorter interconnects and lower average hop counts [204, 167]. However, <u>3D</u> integration comes with many challenges, of which thermal challenge is the most alerting due to the high power density and longer major heat diffusion paths [126, 38, 86].

A considerable amount of research has been conducted in the field of the modelling and mitigation of both PSN and thermal noise for CMP and MPSoC systems [75, 65, 126, 209, 17, 163, 185]. However, most studies assume applications with independent tasks and the impact of the rapidly increasing NoC communication workload is often ignored. Moreover, the impact of PSN and thermal noise on NoC performance and reliability is rarely studied.

This thesis focuses on the impact of NoC workload on PSN and temperature in multi/many core VLSI systems. In contrast to processors, this workload would have an interesting correlation with the temporal and spatial distributions of traffic load. NoC workload can be determined in early design stages, once the characteristics of the application are known. Moreover, NoC workload is spread across most of the chip area. Thus, by controlling this workload, a considerable overall mitigation of PSN and temperature noise can be achieved.

#### **1.2 THESIS CONTRIBUTIONS**

The major contributions of this thesis can be summarized as follows:

Developing a tool for computing the on-chip power supply noise caused by NoC traffic patterns. This tool integrates models for the power grid, NoC traffic simulation, and router microarchitectural power. Moreover, rigorous verification of the models is conducted using SPICE simulations. The developed models have been employed to analyse the power supply noise in NoCs. Novel correlations are found between PSN and different traffic patterns and routing algorithms [54, 51].

- Studying the impact of the resulting PSN on NoC reliability. A statistical timing analysis (STA) of link timing is conducted in the presence of power supply noise. From this analysis high level fault metrics are evaluated such as the probability of timing errors and bit error rate (BER) for both real world and synthetic communication scenarios. Correlations between these metrics and NoC traffic patterns, routing algorithms and application task mapping are then analysed and discussed [54, 53]

- A new concept for optimizing PSN in NoCs application mapping is introduced. The proposed mapping considers the impact of communication workload on the power delivery network in multi-core NoC-based systems using the new metric of *activity density* and the analysis of the impact of its spatial patterns on power supply integrity. Relationships between the spatial distribution patterns of core activity and PSN are studied and discussed [53].

- *Tile repulsive force* is proposed as an objective of mapping strategy which, in contrast to other NoC mapping strategies, results in spreading high activity tiles across the chip in order to minimize activity density. This achieves significant reductions in PSN with low energy penalties compared to energy mapping. Moreover, statistical timing analysis of the resulting systems shows a considerable reduction in BER. This is achieved in the new mapping strategy due to the reduced PSN, and the lower frequency of timing violations, which leads to better timing accuracy [53].

- Proposing a new run-time thermal-adaptive routing strategy which can effectively diffuse heat from NoC-based 3D chip multiprocessors (CMPs). This strategy uses a distributed dynamic programming-based control architecture called the dynamic programming network (DPN). Moreover, the DPN is improved such that computation and propagation of the cost is in compliance with deadlock-free routing algorithms. The proposed routing is evaluated through experimental studies and comparisons with state-of-the-art NoC run-time thermal management (RTM) schemes using various synthetic and real traffic scenarios. Temperature, reliability, energy and performance results are compared and discussed. Moreover, the hardware implementation of the proposed method is discussed in detail and area and power overheads are evaluated. The proposed technique is shown to outperform existing RTM approaches in terms of thermal regulation, chip reliability and performance [55, 14].

- A new approach for extending two-dimensional (2D) partiallyadaptive routing algorithms to 3D is introduced. This improves the adaptive 3D NoC routing algorithms in order to achieve higher

path diversity and more balanced adaptiveness. As a result, better DPN performance is gained. This is achieved by applying different turn prohibition rules for different layers, resulting in different restrictions on traffic flow for different layers and a more balanced degree of adaptiveness [55, 56, 52].

• The DPN-based RTM for NoCs is implemented in field-programmable gate array (FPGA). Direct on-chip temperature readings from distributed thermal sensors are used, and a low-cost implementation of DPNis achieved. For thermal sensing, ring oscillator (RO) is used and the challenges associated with sensor accuracy and precision, including V<sub>DD</sub> drop isolation and compensation for intra-chip process variations, are addressed. In terms of functionality, the proposed design is shown to be highly flexible in maneuvering packets away from hot regions. This results in reductions in maximum chip temperature up to 16% and chip's thermal gradient is reduced by up to 51% compared to performance-driven routing. Moreover, the proposed scheme results in significantly slower chip heating, reflected in higher performance of up to 100% when the chip works under a thermal limit [57].

#### 1.3 THESIS LAYOUT

The thesis is organised into seven chapters. The major contributions of the thesis are described in two major parts. The modelling and optimization of PSN in NoCs is covered in Chapters 3 and 4, while Chapters 5 and 6 cover thermal optimization in NoCs. The chapters are summarized as follows:

Chapter 1 "Introduction". Introduces the motivations, contributions, assumptions and layout of the thesis.

Chapter 2 "Background and Literature Review". Describes the background of relevant theory and applications concerning on-chip interconnection networks. Also, a review of the methodologies for NoC research and industry designs is presented.

Chapter 3 "Power Supply Variations Modelling in Networks-on-Chip". Explains a modelling tool of power supply variations (noise) in NoCs. This tool integrates a fast power grid model, an NoC traffic simulator, an on-chip link model and a router energy model. The chapter also demonstrates the use of the proposed model in analysing the impact of PSN on the reliability of NoC interconnects. This is conducted through a STA of NoC interconnects in the presence of power supply variations and the evaluation of BER.

Chapter 4 "Power Supply Noise Minimization Mapping". A new mapping strategy is proposed in this chapter. This mapping aims for activity balancing in the chip, which is achieved by employing a force-based metric optimization. Metrics for regional activity density are defined and their impacts on PSN are analysed. Evaluation results of the proposed strategy, with many real-application benchmarks, are presented and discussed.

Chapter 5 "Dynamic Thermal Optimization in 3D NoCs". An adaptive run-time routing strategy is introduced. This strategy effectively optimizes heat distribution in 3D NoC-based CMPs. This is achieved by employing DPN to select and optimize the direction of data maneuver in the NoC with thermal-awareness. Moreover, a technique for improving routing algorithms path diversity and degree of adaptiveness is presented and evaluated. The proposed routing scheme is compared with recent NoCs thermal optimization techniques in terms of thermal reduction, reliability improvement, and throughput performance overhead.

Chapter 6 "FPGA Implementation of Thermal-Adaptive Routing in NoCs". In this chapter, FPGA implementation of the proposed thermaladaptive routing in NoCs is described. DPN is used to implement the adaptive routing control logic and ROs are used for temperature sensing implementation. Challenges associated with DPN and sensor implementations are addressed. Moreover, implementation results in terms of functionality and thermal regulation, with a variety of traffic patterns, are presented and discussed.

Chapter 7 "Conclusions and Future Work". This chapter draws major conclusions and gives suggestions for future extensions of the works in the thesis.

#### 2.1 INTRODUCTION

With the shrinking of feature size, both the scale of integration and complexity of very large scale integration (VLSI) systems that can be placed in a chip are increasing. This motivated the development of multi-core and many-core systems-on-chip (SoCs), multiprocessor systems-on-chip (MPSoCs) and chip multiprocessors (CMPs) to deliver new levels of performance. However, buses, were traditionally the mainstay of on-chip interconnection, but these cannot keep up with the communication demands of multi-core systems. Even thought bus-based architectures have evolved from a single-shared bus to multiple bridged buses, such as in the AMBA multi-layer [177], they have remained non-scalable for large number of cores making on-chip communication a performance bottleneck.

To tackle the challenges of on-chip interconnection complexity, *Networks-on-Chip* (*NoCs*) have been proposed as a power efficient, modular, reliable and scalable on-chip communication paradigm [63, 23]. Since their emergence, packet-switched NoCs have became a common solution to overcome the limitations of point-to-point and bus-based on-chip communication architectures.

This chapter reviews the major concepts associated with on-chip networks, including architectures, topologies, routing, switching and flow control, in addition to emerging technologies in NoCs research such as three-dimensional networks-on-chip (3D NoCs). Moreover, recent advances in Network-on-Chip (NoC) research by the leading academic and industrial communities are surveyed.

#### 2.2 BACKGROUND

#### 2.2.1 Networks-on-Chip

NoCs have emerged as a new communication platform for connecting intellectual property (IP) cores in the same chip to form a system-onchip (SoC) or chip-multiprocessor (CMP). On-chip communication is achieved through packet-based messaging, and routers are used to relay packets among the interconnected components. On-chip networks share many design challenges with networks at other scales, such as on-board networks of processors or computer networks. However, NoCs connect components on the same chip. This imposes tighter power and area constraits on their design. Since the introduction of NoCs over a decade ago, rapid advances in both research [130, 145, 23, 86, 112, 110] and industry [193, 181, 183, 164] have occurred. This section briefly introduces various aspects of on-chip networks, including architectures, topologies, routing, switching, flow control and 3D NoCs.

#### 2.2.2 NoC Topology

The morphological structure or connection pattern of network nodes that are connected by a set of channels is called network topology. Network topology is chosen based on many factors, such as scalability, cost and performance. Fig. 2.1 illustrates a set of the most popular onchip network topologies that are used in research and industry [59, 66]. The simplest topology is the shared bus (Fig. 2.1a) where all IP cores share a common link and, thus, compete for exclusive access to this link. For systems with high communication requirements and large numbers of IPs, buses cannot scale efficiently and can be a performance bottleneck.

The bus can be slightly modified to create a ring topology (Fig. 2.1b) to achieve better performance. However, the ring can become saturated at a low injection rate and it is still not efficiently scalable. The crossbar topology (Fig. 2.1e) provides full connectivity which enable one-hop distance between any two IPs. However, the crossbar is poorly scalable since the number of links required increases exponentially with the number of nodes. Mesh and torus topologies provide much better performance and they are more scalable than other topologies. Thus, many commercial implementations of NoC-based CMPs and SoCs have adopted the mesh [181, 193, 164] and torus [59, 66]. On the other hand, some SoCs adopt irregular or application-specific topologies (Fig. 2.1f) that are tailored to the requirements of the target application [138, 167].

#### 2.2.3 NoC Components

The architecture of the NoC and its components can vary considerably between one system and another depending on the requirements of the design. However, the description of NoC components here assumes a generic design. The generic NoC architecture consists of routers, links and network interfaces (NIs) which connect IP cores to the network, as shown in Fig 2.2. A brief description of each of these components is given bellow.

#### 2.2.3.1 Router

The router is a major part of a NoC. Its function is to relay data packets in their journey from source to destination. Router architectures can

Figure 2.1: Examples of common on-chip network topologies.

Figure 2.2: Illustration of components in a 2D mesh NoC. NI: Network Interface, R: Router.

vary significantly from one design to another as routers must be designed to meet area and power constraints, as well as, the performance requirements of the target on-chip system. These requirements and constraints vary from one on-chip system to the other and the router design varies accordingly.