$\mu Systems$  Research Group

School of Electrical and Electronic Engineering

## Elastic Bundles: Modelling and Architecting Asynchronous Circuits with Granular Rigidity

Johnson Fernandes

Technical Report Series

NCL-EEE-MICRO-TR-2017-206

Contact: johnson.fernandes@ncl.ac.uk

Supported by EPSRC grant EP/I038551/1

NCL-EEE-MICRO-TR-2017-206

Copyright (C) 2017 Newcastle University

µSystems Research Group School of Electrical and Electronic Engineering Merz Court Newcastle University Newcastle upon Tyne, NE1 7RU, UK

http://async.org.uk/

# Elastic Bundles: Modelling and Architecting Asynchronous Circuits with Granular Rigidity

Johnson Fernandes

A Thesis submitted for the degree of Doctor of Philosophy School of Electrical and Electronic Engineering Newcastle University

March 2017

### Abstract

Integrated Circuit (IC) designs these days are predominantly System-on-Chips (SoCs). The complexity of designing a SoC has increased rapidly over the years due to growing process and environmental variations coupled with global clock distribution difficulty. Moreover, traditional synchronous design is not apt to handle the heterogeneous timing nature of modern SoCs. As a countermeasure, the semiconductor industry witnessed a strong revival of asynchronous design principles. A new paradigm of digital circuits emerged, as a result, namely mixed synchronous-asynchronous circuits. With a wave of recent innovations in synchronous-asynchronous CAD integration, this paradigm is showing signs of commercial adoption in future SoCs mainly due to the scope for reuse of synchronous functional blocks and IP cores, and the co-existence of synchronous and asynchronous design styles in a common EDA framework.

However, there is a lack of formal methods and tools to facilitate mixed synchronousasynchronous design. In this thesis, we propose a formal model based on Petri nets with step semantics to describe these circuits behaviourally. Implication of this model in the verification and synthesis of mixed synchronous-asynchronous circuits is studied. Till date, this paradigm has been mainly explored on the basis of Globally Asynchronous Locally Synchronous (GALS) systems. Despite decades of research, GALS design has failed to gain traction commercially. To understand its drawbacks, a simulation framework characterising the physical and functional aspects of GALS SoCs is presented.

A novel method for synthesising mixed synchronous-asynchronous circuits with varying levels of rigidity is proposed. Starting with a high-level dataflow model of a system which is intrinsically asynchronous, the key idea is to introduce rigidity of chosen granularity levels in the model without changing functional behaviour. The system is then partitioned into functional blocks of synchronous and asynchronous elements before being transformed into an equivalent circuit which can be synthesised using standard EDA tools.

### Acknowledgements

I would like to thank my supervisors; Prof. Alex Yakovlev, Dr. Alex Bystrov and Dr. Danil Sokolov for their invaluable guidance throughout this research. This thesis would not have been possible without their support, patience and encouragement over the last five years.

I would also like to thank Prof. Maciej Koutny and Dr. Marta Pietkiewicz-Koutny for formalisation of concepts presented in Chapter 4.

Thanks goes to Dr. James Docherty, Dr. Athanasios Grivas, Dr. Graeme Coapes and Mr. Alessandro De Gennaro for their hours of friendly discussions that kept the research atmosphere lively.

Special thanks goes to my parents Joseph and Apoline, and to my sisters Jenifer and Jessica for their love and constant encouragement during the course of this research. I am also thankful to Ravneet for her patience and wholehearted support, especially during the writing up of this thesis.

Finally, I would like to acknowledge that this work was partly sponsored by the School of Electrical and Electronic Engineering, Newcastle University and the EPSRC under the research grant GAELS EP/I038551/1.

### Publications

Parts of this work have appeared in the following publications:

- Journal Paper

- J. Fernandes, M. Koutny, L. Mikulski, M. Pietkiewicz-Koutny, D. Sokolov, and A. Yakovlev, "Persistent and Nonviolent steps and the design of GALS systems", Fundamenta Informaticae, vol. 137, pp. 143–170, 2015.

- Conference Papers

- J. Fernandes, D. Sokolov, and A. Yakovlev, "Elastic Bundles: Modelling and synthesis of asynchronous circuits with granular rigidity", International Symposium on Asynchronous Circuits and Systems (ASYNC), 2017. (in press)

- J. Fernandes, M. Koutny, M. Pietkiewicz-Koutny, D. Sokolov, and A. Yakovlev,

"Step persistence in the design of GALS systems", International Conference on Applications and Theory of Petri Nets and Concurrency (ICATPN), vol. 7927,

pp. 190-209, 2013.

- Technical Report

- J. Fernandes, M. Koutny, M. Pietkiewicz-Koutny, D. Sokolov, and A. Yakovlev,

"Step persistence in the design of GALS systems", Technical Report Series, CS-TR-1349, School of Computing Science, Newcastle University, 2012.

## Contents

|                                         | Abs              | stract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                         | i   |

|-----------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----|

|                                         | Acknowledgements |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                         | ii  |

|                                         | Pub              | olicatio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ns                                      | iii |

|                                         | List             | of Fig                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | gures                                   | x   |

|                                         | List             | cknowledgements       ii         ublications       iii         st of Figures       x         st of Tables       xi         st of Abbreviations       xii         troduction       1         1       Motivation       1         2       Research Goals and Thesis Contribution       5         3       Thesis Organisation       6         ackground       8       2.1.1       Step Transition Systems       8         2.1.2       Petri nets       9       9         2       Bundled-Data Asynchronous Pipelines       13       2.2.1       Synchronous vs. Asynchronous Pipelines       13         2.2.2       Bundled-data protocols       15       15 |                                         |     |

|                                         | List             | of Ab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | breviations                             | xii |

| 1                                       | Intr             | oducti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | on                                      | 1   |

|                                         | 1.1              | Motiv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ation                                   | 1   |

|                                         | 1.2              | Reseat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | rch Goals and Thesis Contribution       | 5   |

|                                         | 1.3              | Thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Organisation                            | 6   |

| 2 Background                            |                  | ıd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8                                       |     |

|                                         | 2.1              | Behav                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ioural Modelling                        | 8   |

|                                         |                  | 2.1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Step Transition Systems                 | 8   |

|                                         |                  | 2.1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Petri nets                              | 9   |

| 2.2 Bundled-Data Asynchronous Pipelines |                  | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         |     |

|                                         |                  | 2.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Synchronous vs. Asynchronous Pipelines  | 13  |

|                                         |                  | 2.2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Bundled-data protocols                  | 15  |

|                                         |                  | 2.2.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | RT-based Bundled-Data Circuit Synthesis | 16  |

| 3 | Phy            | sical F | Partitioning and its Limitations                     | 19            |  |  |  |

|---|----------------|---------|------------------------------------------------------|---------------|--|--|--|

|   | 3.1            | Introd  | uction                                               | 19            |  |  |  |

|   | 3.2            | Metho   | dology                                               | 22            |  |  |  |

|   |                | 3.2.1   | Characterising a GALS Design                         | 22            |  |  |  |

|   |                | 3.2.2   | Simulation Framework                                 | 27            |  |  |  |

|   |                | 3.2.3   | Trade-off Analysis                                   | 34            |  |  |  |

|   |                | 3.2.4   | Tool Description                                     | 37            |  |  |  |

|   | 3.3            | Result  | S                                                    | 38            |  |  |  |

|   |                | 3.3.1   | GALS Design Impact to System Latency                 | 38            |  |  |  |

|   |                | 3.3.2   | GALS Design Benefit to System Power                  | 40            |  |  |  |

|   |                | 3.3.3   | Energy Efficiency Analysis                           | 43            |  |  |  |

|   | 3.4            | Conclu  | usions and Future Work                               | 45            |  |  |  |

| 4 | The            | eory of | Bundles                                              | <b>49</b><br> |  |  |  |

|   | 4.1            | Introd  | uction                                               | 49            |  |  |  |

|   | 4.2            | Step F  | Persistence in Nets                                  | 53            |  |  |  |

|   |                | 4.2.1   | Defining Persistent Steps                            | 54            |  |  |  |

|   |                | 4.2.2   | Basic Properties of Persistent Steps                 | 56            |  |  |  |

|   |                | 4.2.3   | Global Persistence in Safe PT-nets                   | 59            |  |  |  |

|   | 4.3            | Prunir  | ng Reachability Graphs                               | 61            |  |  |  |

|   | 4.4            | Signifi | cance of Bundles in Digital Circuits                 | 71            |  |  |  |

|   | 4.5            | Conclu  | usions and Future Work                               | 74            |  |  |  |

| 5 | $\mathbf{Syn}$ | thesis  | of Asynchronous Circuits with Granular Rigidity      | 76            |  |  |  |

|   | 5.1            | Introd  | uction                                               | 76            |  |  |  |

|   | 5.2            | Model   | ling Digital Systems                                 | 78            |  |  |  |

|   |                | 5.2.1   | PN building blocks                                   | 79            |  |  |  |

|   |                | 5.2.2   | Modelling a Conceptual Design                        | 80            |  |  |  |

|   |                | 5.2.3   | Partitioning with Bundles                            | 81            |  |  |  |

|   | 5.3            | Digita  | l Circuit Synthesis from PN Models                   | 84            |  |  |  |

|   |                | 5.3.1   | Model Transformation to Asynchronous Pipeline Models | 84            |  |  |  |

|   |                |         |                                                      |               |  |  |  |

|              |        | 5.3.2                     | Partitioning into Elastic Bundles                | 85  |

|--------------|--------|---------------------------|--------------------------------------------------|-----|

|              |        | 5.3.3                     | From PN Models to Digital Circuits               | 88  |

|              | 5.4    | 4 16-point FFT Case Study |                                                  | 92  |

|              | 5.5    | Conclu                    | usions and Future Work                           | 96  |

| 6 Conclusion |        |                           | n                                                | 97  |

|              | 6.1    | Summ                      | nary of Contributions                            | 98  |

|              | 6.2    | Future                    | e Work                                           | 100 |

| Bi           | ibliog | graphy                    |                                                  | 100 |

|              | Apj    | pendix                    |                                                  | 113 |

|              |        | MATI                      | LAB code of GALS physical partitioning analysis  | 113 |

|              | App    | pendix                    | B                                                | 144 |

|              |        | 16-poi                    | int FFT Top-Level Verilog Code                   | 144 |

|              |        | 16-poi                    | int FFT Control Verilog Code                     | 149 |

|              |        | 4-poin                    | nt FFT Datapath Verilog Code                     | 163 |

|              |        | 4-poin                    | nt FFT Bundled-Data Control Verilog Code         | 165 |

|              |        | 4-poin                    | nt FFT EB Maximal Control Verilog Code           | 181 |

|              |        | 4-poin                    | nt FFT Top-Level Verilog Code                    | 185 |

|              | Ap     | pendix                    |                                                  | 188 |

|              |        | Timin                     | ng Assumption Scripts for EB Maximal 4-point FFT | 188 |

|              | Ap     | pendix                    |                                                  | 191 |

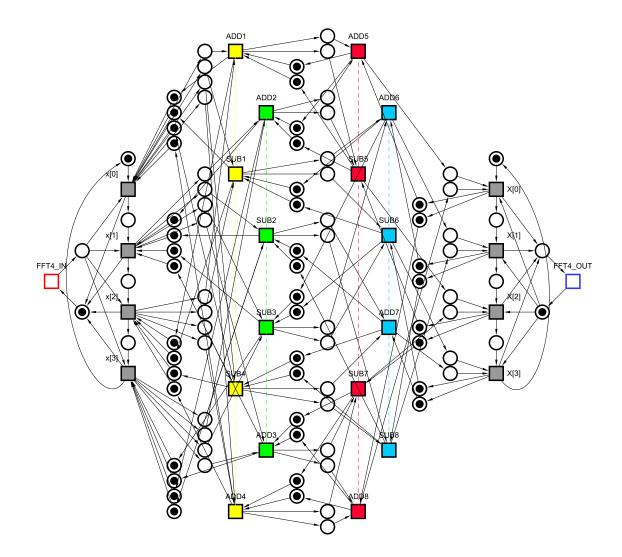

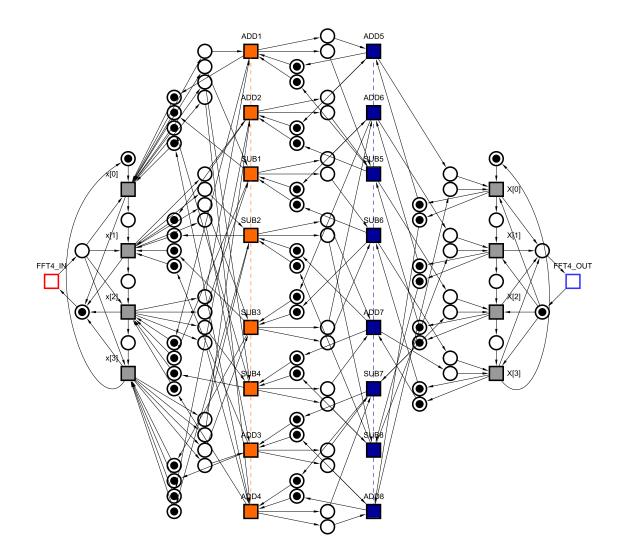

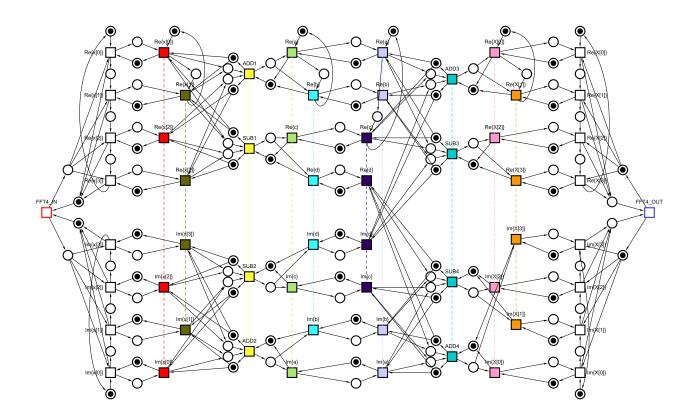

|              |        | 4-poin                    | nt FFT Asynchronous CDFG                         | 191 |

|              |        | 4-poin                    | nt FFT Temporal Bundle CDFG                      | 192 |

|              |        | 4-poin                    | nt FFT Maximal Bundle CDFG                       | 193 |

|              |        | 4-poin                    | nt FFT Reuse Bundle CDFG and Control Circuits    | 194 |

# List of Figures

| 1.1  | Illustration of mixed synchronous-asynchronous circuits                                        | 4  |

|------|------------------------------------------------------------------------------------------------|----|

| 2.1  | A PT-net $\mathcal{N}(a)$ ; and its concurrent reachability graph $CRG(\mathcal{N})(b)$ . Note |    |

|      | that arcs (in fact, self-loops) labelled by the empty step are not shown in                    |    |

|      | $CRG(\mathcal{N})$                                                                             | 10 |

| 2.2  | A safe persistent PT-net $\mathcal{N}$ (a); and its concurrent reachability graph              |    |

|      | $CRG(\mathcal{N})$ (b)                                                                         | 12 |

| 2.3  | Synchronous versus asynchronous pipelines                                                      | 14 |

| 2.4  | Four-phase and two-phase asynchronous signalling protocols                                     | 15 |

| 2.5  | Relative-timing based asynchronous design flow (reproduced from $[1]$ )                        | 16 |

| 2.6  | Characterised handshake control element for bundled-data circuits $\ldots$                     | 18 |

| 3.1  | Typical GALS design block.                                                                     | 20 |

| 3.2  | Global CDN and GALS partitioning.                                                              | 23 |

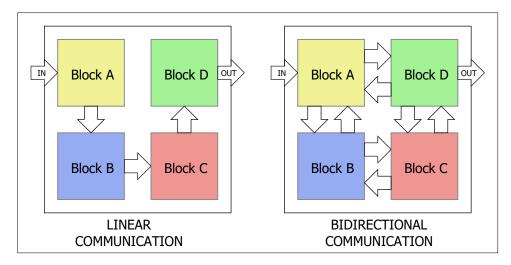

| 3.3  | Linear versus bidirectional block communication.                                               | 32 |

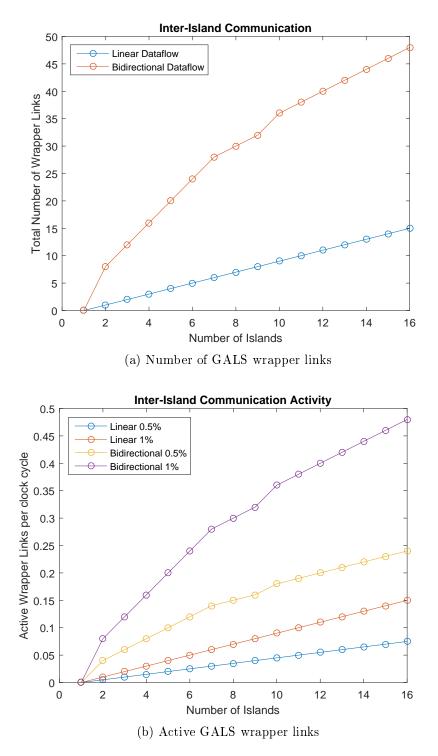

| 3.4  | GALS inter-island communication distribution                                                   | 39 |

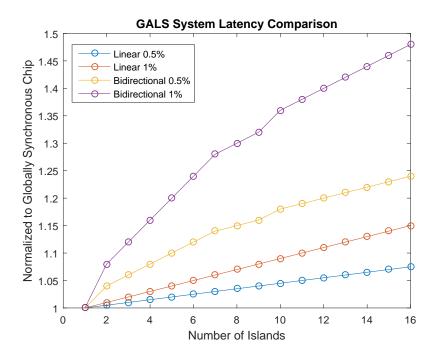

| 3.5  | System latency analysis of GALS versus synchronous chip                                        | 40 |

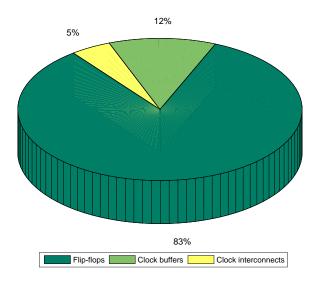

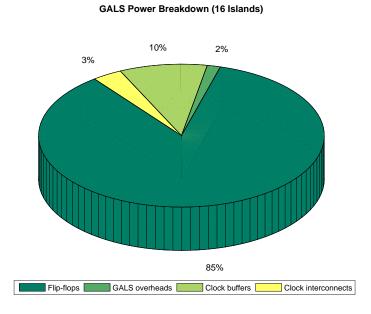

| 3.6  | Design power breakdown at 218MHz clock (65nm)                                                  | 41 |

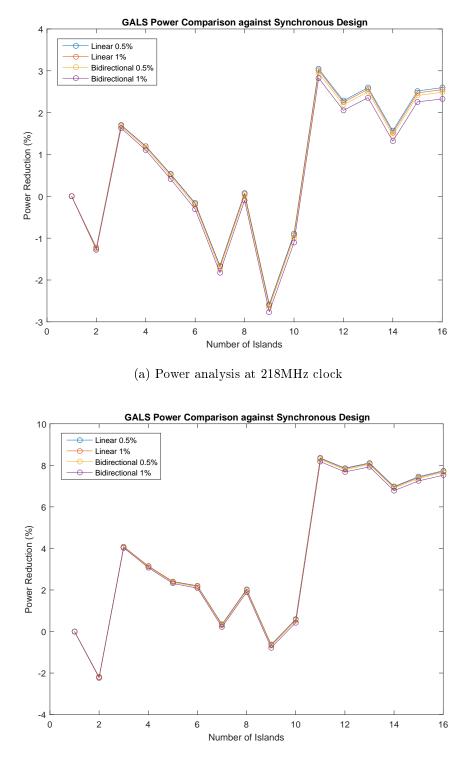

| 3.7  | Power efficiency analysis of GALS versus synchronous design (65nm) $~$                         | 42 |

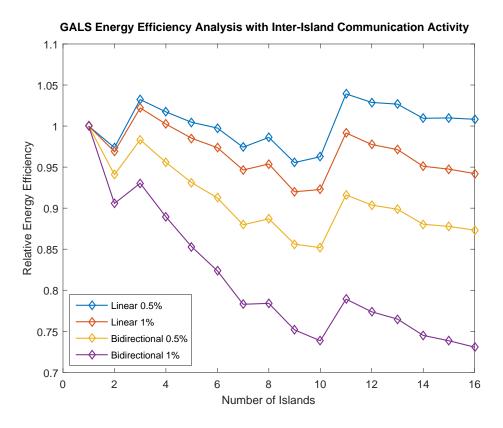

| 3.8  | REE analysis of GALS versus synchronous chip at 544MHz clock (65nm) $$ .                       | 44 |

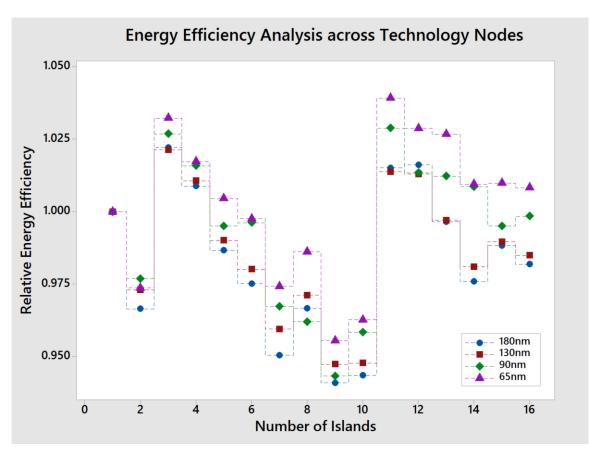

| 3.9  | Trend of REE with process technology (41,210 FFs)                                              | 45 |

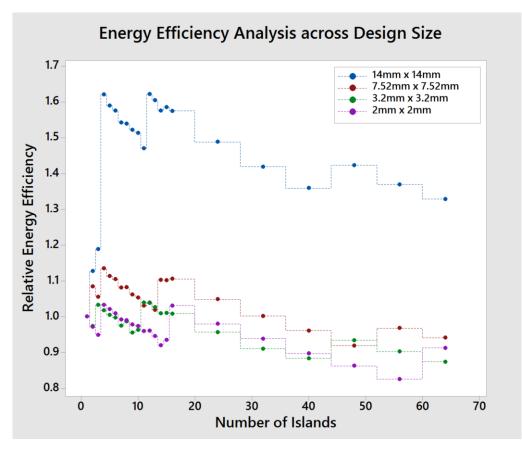

| 3.10 | Trend of REE with design size $(65nm)$                                                         | 46 |

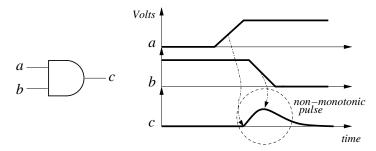

| 4.1  | Hazardous switching of an AND gate                                                             | 50 |

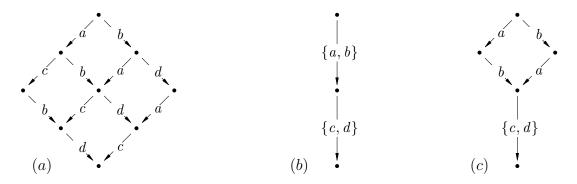

| 4.2  | Temporal representations of systems having concurrent, parallel and mixed                                                                                                 |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | concurrent-parallel behaviours: $(a)$ interleaving model for asynchronous                                                                                                 |    |

|      | behaviour; $(b)$ step model for synchronous behaviour; and $(c)$ mixed model                                                                                              |    |

|      | for mixed synchronous-asynchronous behaviour.                                                                                                                             | 51 |

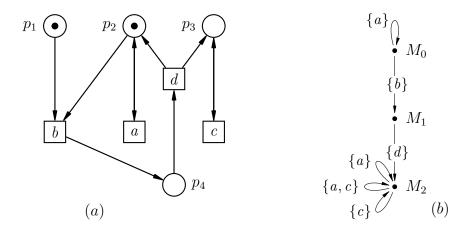

| 4.3  | A safe persistent PT-net and its concurrent reachability graph.                                                                                                           | 56 |

| 4.4  | A safe PT-net and its concurrent reachability graph.                                                                                                                      | 57 |

| 4.5  | Three safe PT-nets and their concurrent reachability graphs                                                                                                               | 58 |

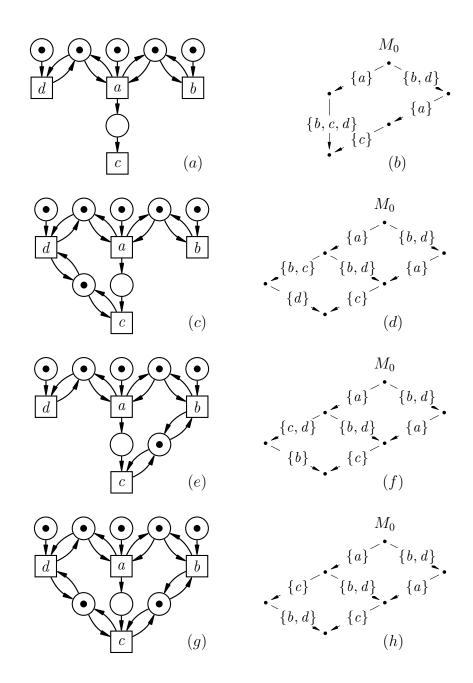

| 4.6  | A safe PT-net $\mathcal{N}(a)$ ; and its concurrent reachability graph $CRG(\mathcal{N})(b)$ .                                                                            | 61 |

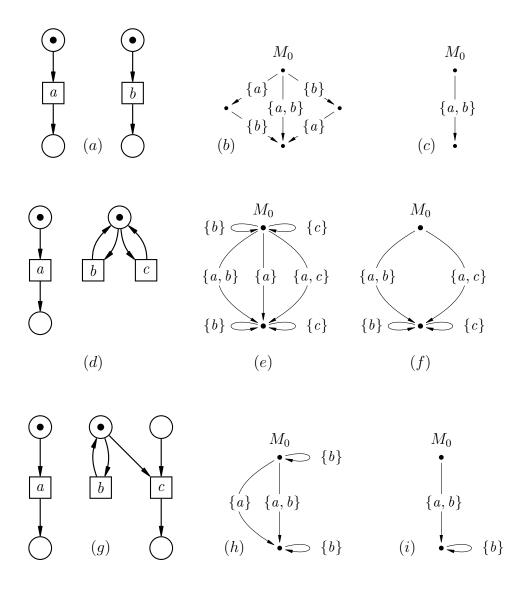

| 4.7  | Three safe persistent PT-nets $\mathcal{N}$ $(a, d, g)$ ; their concurrent reachability                                                                                   |    |

|      | graphs $CRG(\mathcal{N})$ $(b, e, h)$ ; and the corresponding $CRG^{max}(\mathcal{N}) \preccurlyeq_{pers}^{local} CRG(\mathcal{N})$                                       |    |

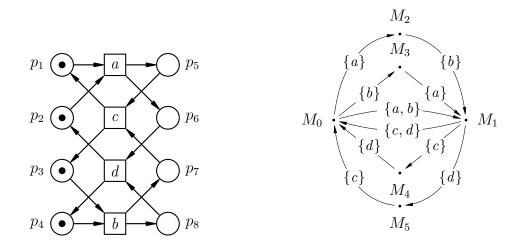

|      | obtained in the pruning procedure $(c, f, i)$ .                                                                                                                           | 66 |

| 4.8  | A safe persistent PT-net $\mathcal{N}(a)$ ; its concurrent reachability graph $CRG(\mathcal{N})$                                                                          |    |

|      | (b); and $CRG^{max}(\mathcal{N}) \preccurlyeq^{local}_{pers} CRG(\mathcal{N})$ obtained in the pruning procedure                                                          |    |

|      | $(c). \qquad \ldots \qquad $                              | 67 |

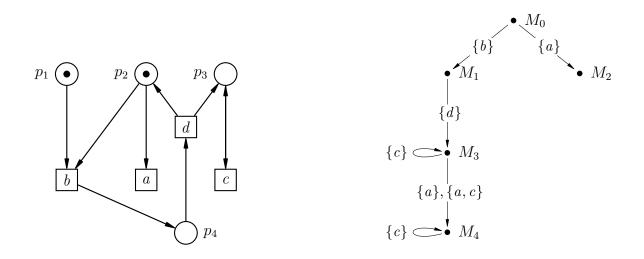

| 4.9  | A safe persistent PT-net $\mathcal{N}(a)$ ; its concurrent reachability graph $CRG(\mathcal{N})$                                                                          |    |

|      | (b); $CRG^{max}(\mathcal{N})$ obtained in the pruning procedure which does not satisfy                                                                                    |    |

|      | $CRG^{max}(\mathcal{N}) \preccurlyeq^{local}_{pers} CRG(\mathcal{N})$ (c); a persistent and safe PT-net $\mathcal{N}' = \mathcal{N}_{b\leftrightarrow c}$                 |    |

|      | (d); and its concurrent reachability graph $CRG(\mathcal{N}') = CRG^{max}(\mathcal{N}')$ which                                                                            |    |

|      | trivially satisfies $CRG^{max}(\mathcal{N}') \preccurlyeq^{local}_{pers} CRG(\mathcal{N}')$ (and also $CRG^{max}(\mathcal{N}') \preccurlyeq^{global}_{pers}$              |    |

|      | $CRG(\mathcal{N}'))$ (e)                                                                                                                                                  | 68 |

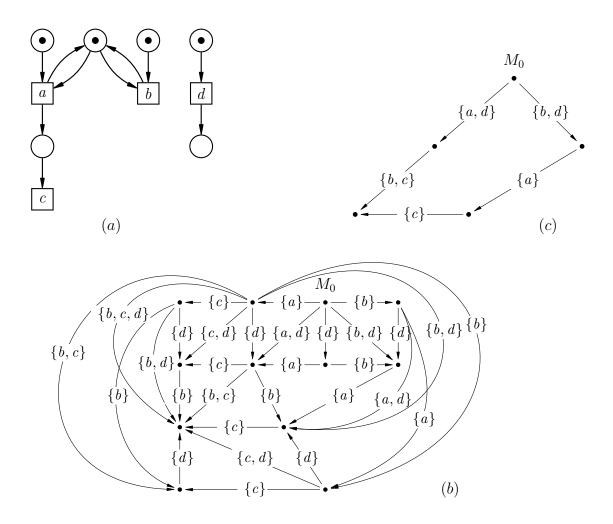

| 4.10 | A safe persistent PT-net $\mathcal{N}(a)$ ; $CRG^{max}(\mathcal{N})$ not satisfying $CRG^{max}(\mathcal{N}) \preccurlyeq_{pers}^{local}$                                  |    |

|      | $CRG(\mathcal{N})$ (b); $\mathcal{N}' = \mathcal{N}_{d\leftrightarrow c}$ (c); $CRG^{max}(\mathcal{N}')$ (d); $\mathcal{N}'' = \mathcal{N}_{b\leftrightarrow c}$ (e); and |    |

|      | $CRG^{max}(\mathcal{N}'')$ (f). Both $\mathcal{N}'$ and $\mathcal{N}''$ have been obtained as by-products of                                                              |    |

|      | the successful runs of the pruning and modification algorithm. It is not                                                                                                  |    |

|      | possible to obtain in this way $\mathcal{N}'''$ in $(g)$ even though $CRG^{max}(\mathcal{N}'') \preccurlyeq^{global}_{pers}$                                              |    |

|      | $CRG(\mathcal{N})$ (h)                                                                                                                                                    | 70 |

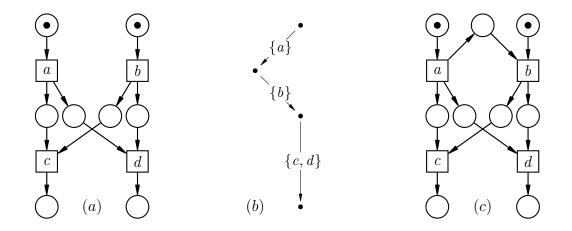

| 4.11 | A pt-net generating the concurrent reachability graph of Figure $4.2(c)$            |     |

|------|-------------------------------------------------------------------------------------|-----|

|      | under the assumption that $a$ and $b$ belong to two different clock domains,        |     |

|      | while $c$ and $d$ belong to a third clock domain $(a)$ ; and another mixed          |     |

|      | synchronous-asynchronous implementation of the same system (assuming                |     |

|      | the same clock domains as in $(a)$ both behaviourally $(b)$ and as a derived        |     |

|      | PT-net $(c)$                                                                        | 73  |

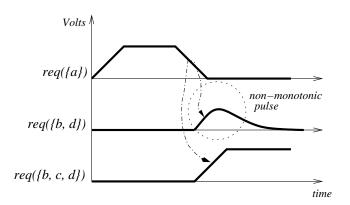

| 4.12 | Hazardous switching in mixed synchronous-asynchronous step execution                |     |

|      | semantics                                                                           | 74  |

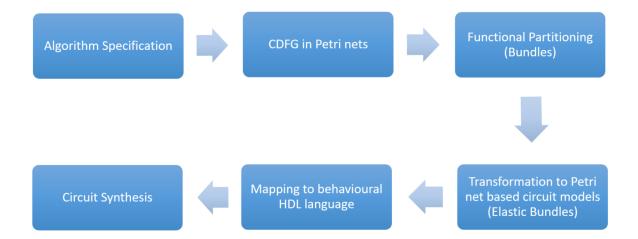

| 5 1  | Design methodology flow                                                             | 77  |

| 5.1  | Design methodology flow                                                             | 77  |

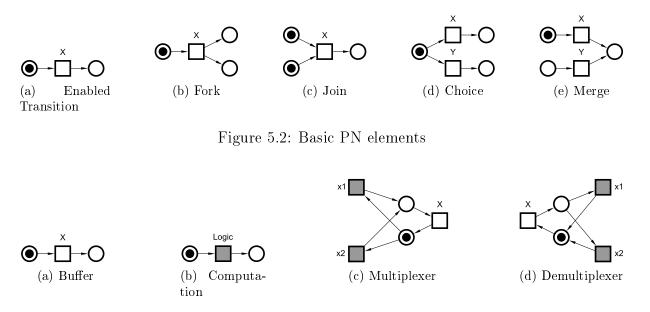

| 5.2  | Basic PN elements                                                                   | 79  |

| 5.3  | PN building blocks for digital systems                                              | 79  |

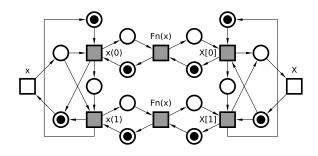

| 5.4  | Example of PN model designs                                                         | 79  |

| 5.5  | Wagging $[2]$                                                                       | 80  |

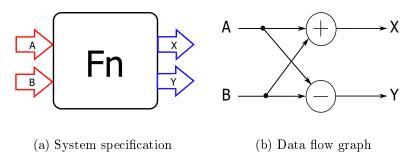

| 5.6  | Conceptual design                                                                   | 81  |

| 5.7  | PN models of conceptual design                                                      | 82  |

| 5.8  | Pruned reachability graphs describing bundles                                       | 83  |

| 5.9  | Modelling bundles with Policy Nets                                                  | 84  |

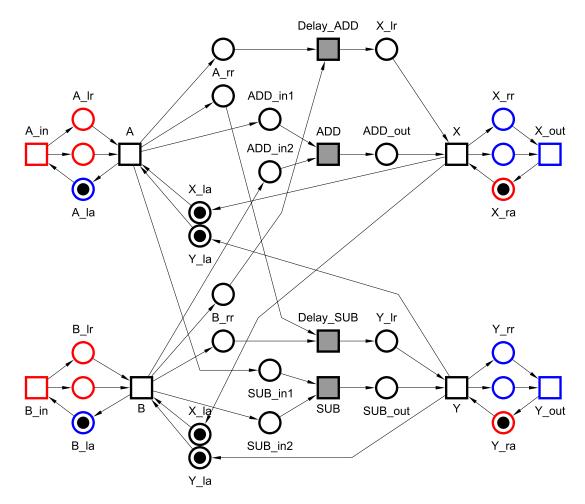

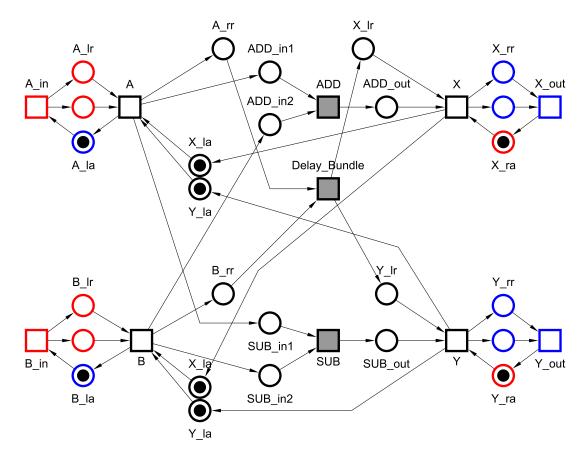

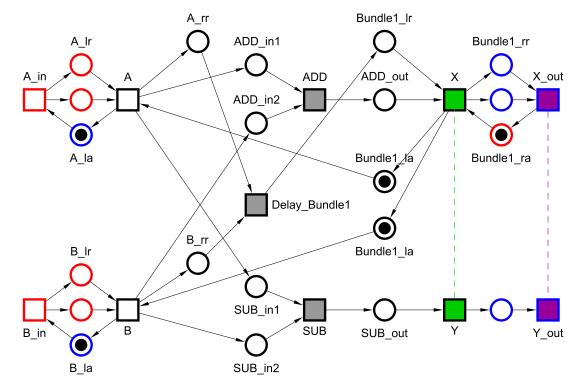

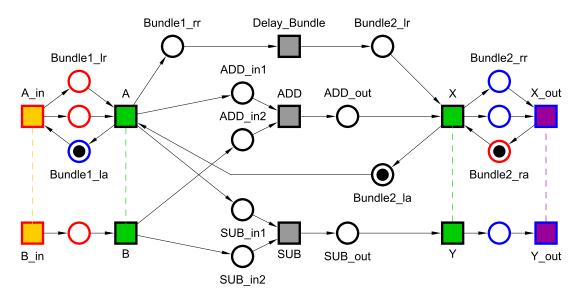

| 5.10 | Transformation to bundled-data asynchronous pipeline                                | 86  |

| 5.11 | Elastic-bundle pipeline transformation (bundle set 1) $\ldots \ldots \ldots \ldots$ | 87  |

| 5.12 | Elastic-bundle pipeline transformation (bundle set 2) $\ldots \ldots \ldots$        | 87  |

| 5.13 | Elastic-bundle pipeline transformation (bundle set 3) $\ldots \ldots \ldots \ldots$ | 88  |

| 5.14 | Fork join circuit                                                                   | 89  |

| 5.15 | Bundled-data asynchronous circuit of conceptual design                              | 91  |

| 5.16 | Elastic-bundle circuit (bundle set 1)                                               | 91  |

| 5.17 | Elastic-bundle circuit (bundle set 2)                                               | 92  |

| 5.18 | Elastic-bundle circuit (bundle set 3)                                               | 92  |

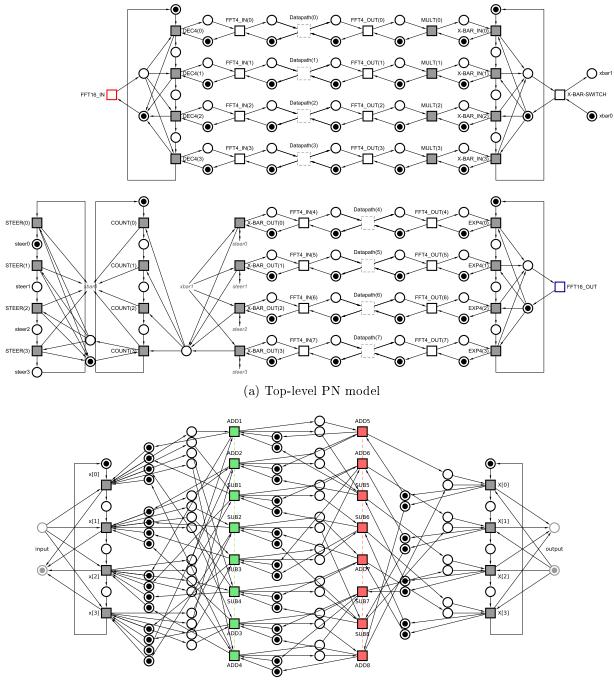

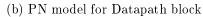

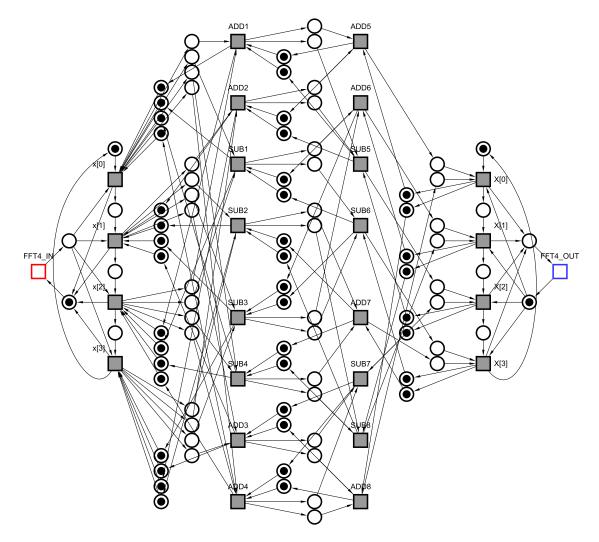

| 5.19 | PN model for 16-point FFT                                                           | 94  |

| 6.1  | Petri net of asynchronous 4-point FFT                                               | 191 |

| 6.2  | Policy net of 4-point FFT with temporal partitioning                                | 192 |

| 6.3 | Policy net of 4-point FFT with maximal partitioning                             |

|-----|---------------------------------------------------------------------------------|

| 6.4 | Policy net of 4-point FFT with ADD/SUB reuse partitioning                       |

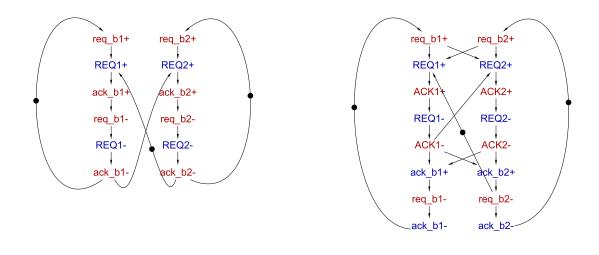

| 6.5 | Signal transition graph (STG) for 4-point FFT reuse bundle control $\ldots$ 194 |

| 6.6 | 4-point FFT pipeline stage 1 bundle control circuit                             |

| 6.7 | 4-point FFT pipeline stage 2 bundle control circuit                             |

# List of Tables

| 3.1 | Process technology and design parameters           | 28 |

|-----|----------------------------------------------------|----|

| 3.2 | Technology parameter $3 \cdot \sigma$ variations   | 30 |

| 3.3 | GALS wrapper specification                         | 36 |

| 5.1 | Synthesis results for several 16-point FFT designs | 95 |

### List of Abbreviations

- **ASIC** Application-Specific Integrated Circuit

- **CAD** Computer Aided Design

- **CDFG** Control Data Flow Graph

- $\mathbf{CDN}$  Clock Distribution Network

- ${\bf CRG}$  Concurrent Reachability Graph

- **DFG** Data Flow Graph

- **DSM** Deep Submicron

- **EDA** Electronic Design Automation

- **EMI** Electro-Magnetic Interference

- FF Flip Flop

- ${\bf FFT}$  Fast Fourier Transform

- GALS Globally Asynchronous Locally Synchronous

- HLS High-Level Synthesis

- **IC** Integrated Circuit

- $\mathbf{NoC}$  Network-On-Chip

- ${\bf PN}$  Petri Net

- **REE** Relative Energy Efficiency

- **RT** Relative Timing

- **RTL** Register-Transfer Level

- SoC System-On-Chip

- ${\bf STG}$  Signal Transition Graph

### Chapter 1

### Introduction

#### 1.1 Motivation

Traditional circuit design styles have been following one of the two main strands, namely synchronous and asynchronous. In a nutshell, these two approaches differ in their techniques of synchronising interaction between circuit elements. Asynchronous designs adopt 'on request' synchronisation where interaction is regulated by means of handshake control signals. They are designed to be adaptive to delays of signal propagation. Synchronous designs, on the other hand, assume worst case delay between circuit elements and determine a global periodic control signal for synchronisation called the *clock*. The clock signal limits the many sequencing options considered in asynchronous control. Synchronous circuits are, therefore, considered to be a proper subset of asynchronous circuits [3]. Asynchronous logic was the dominant design style with most early computers. In particular, David Muller's speed-independent circuits, dating back to the late 1950s, have served many interesting applications such as the ILLIAC I and ILLIAC II computers [4]. However, since 1960, an era when fabrication of integrated circuits (ICs) became a feasible business, synchronous design became the mainstream technique as it met the market needs with its shorter design flow cycle. Today, majority of designs are synchronous, well etched in the heart of semiconductor industry together with superior CAD tools and EDA flows.

IC designs these days are predominantly system-on-chip (SoC) implementations. Most SoCs consist of various intellectual property (IP) blocks embedded into one chip, with

each block having its own timing requirement. This design technique favours the reuse of pre-designed and pre-verified IP blocks, benefiting the semiconductor industry with large productivity gains [5]. The complexity of designing a SoC has grown rapidly over the years due to demand for increased functionality, faster processing speeds and the increasing impact of previously ignorable effects on chip reliability. One of the main reasons is that transitioning to very deep submicron manufacturing (DSM) process has revealed process and environmental variation related problems coupled with the complexity to manage a global clock distribution network (CDN). Moreover, the traditional synchronous clocking style, being more appealing towards processor and instruction-flow designs, is not apt to handle the heterogeneous timing nature of modern SoCs. The semiconductor industry has been constantly researching and adopting new methodologies to improve designer productivity. Consequently, two distinct strategies have emerged, namely Physical Partitioning and Functional Partitioning, to tackle the design challenges of modern SoCs. Design partitioning creates smaller manageable islands with optimal CDNs that would reduce the effect of DSM variability whilst allowing individual islands to operate at their native clock speeds, thereby offering superior design quality than traditional globally clocked SoCs.

Some of the well-known physical partitioning techniques are ARM's big.LITTLE architecture [6], Teklatech's FloorDirector partitioning engine [7], NoCs [8, 9] and GALS-based physical partitioning [10, 11, 12, 13, 14, 15, 16]. These techniques partition a digital design based on physical characteristics to simplify clock distribution, reduce global interconnect complexity, reduce electro-magnetic interference (EMI), improve energy-efficiency and implement voltage frequency scaling on a coarse-grained level. Functional partitioning, on the other hand, partitions a design based on system functionality creating timing-related functional islands that are fine-grained. This offers greater flexibility for design optimisation, thus demonstrating scope for larger benefits than those gained from the physical partitioning approach. High-level synthesis flows such as BlueSpec [17, 18] and Chisel [19]; dataflow synthesis flows such as Click [20] and eTeak [21]; and Petri net (PN) based partitioning techniques such as [22] and [23] fall under this category. With exception of Click, eTeak, PN based partitioning and GALS-based physical partitioning which are based on asynchronous design principles, all the other techniques are implemented using traditional synchronous EDA tool flow.

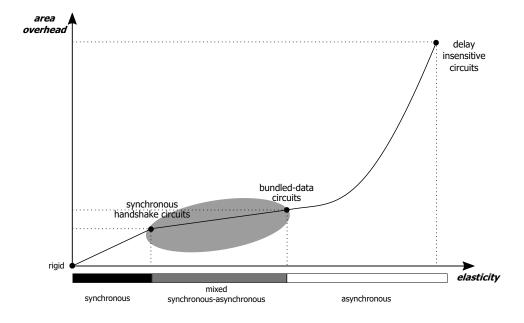

In the recent decade, the semiconductor industry has witnessed a strong revival of asynchronous design principles due to its robustness to DSM variability coming from finegrained circuit timing flexibility, its inherent elasticity and heterogeneity offering great design flexibility, its lower energy consumption profile coming from inherent automatic fine-grained clock gating, and its independence from the need for global clock distribution. Currently, the traditional asynchronous design approach is still infeasible commercially due to the lack of mature CAD tools, significant overheads of asynchronous control protocol, inability to reuse synchronous IP cores and high transitioning costs. However, due to growing semiconductor variability and demand for energy-aware computing, it has been predicted that it is only a matter of time before asynchronous logic penetrates a vast majority of SoCs [24]. Recent innovations in asynchronous design flows such as those in [25, 26, 27, 28, 29, 30, 31, 32, 33] have enabled rapid integration of asynchronous logic into synchronous CAD tools thereby bridging the gap between asynchronous design and designer productivity. In the realm of SoCs, this trend has resulted in an active area of research revolving around mixed synchronous-asynchronous digital design [34, 35, 12, 36, 13, 37, 38, 39, 40, 41, 16, 23, 42, 43]. Figure 1.1 illustrates the positioning of this research area.

Mixed synchronous-asynchronous design can be viewed as a revolutionary step in VLSI design paving the way for commercial adoption of asynchronous design techniques in future SoCs. With a growing trend of synchronous-asynchronous CAD tool flow integration, the mixed synchronous-asynchronous paradigm shows promise to survive the market forces of the semiconductor industry mainly due to the scope for reuse of synchronous design styles in a common EDA framework. However, there is a lack of tools and design methodologies to facilitate mixed synchronous-asynchronous design. So far, this research area has been mainly explored on the basis of GALS systems [44]. Most GALS design implementations emphasised on physical partitioning and followed an assemble-and-validate design style.

Figure 1.1: Illustration of mixed synchronous-asynchronous circuits

on a very coarse-grain level defined by top-level hierarchical boundaries. Furthermore in the realm of circuits, GALS design would only comprise a subset of the shaded area shown in Figure 1.1. In fact, the mixed synchronous-asynchronous design paradigm would encapsulate a range of design practices starting from synchronous handshake circuits [26], which are synchronous circuits embracing principles of asynchronous elasticity, all the way to bundled-data circuits [45, 46], which are asynchronous circuits embracing principles of synchronous rigidity. Hence, we propose a strong motivation for three distinct research areas in this field:

- 1. Discovery of sub-classes of mixed synchronous-asynchronous circuits

- 2. Specification of a common formal method for mixed synchronous-asynchronous circuit description, and

- 3. Reasoning behind functional and physical partitioning strategies for mixed synchronousasynchronous SoC design.

#### 1.2 Research Goals and Thesis Contribution

Entering the paradigm of mixed synchronous-asynchronous circuits, we encountered the following questions which defined the research goals of this thesis:

- How do we model and verify circuits exhibiting mixture of synchronous and asynchronous behaviour?

- What is the ideal strategy for designing mixed synchronous-asynchronous SoCs; is it the physical partitioning approach or a functional partitioning strategy?

- What level of granularity is justified for synchronous and asynchronous logic elements in SoC design?

This thesis is centred around finding answers to these questions.

Decades of research have undergone in GALS-based physical partitioning methodology for mixed synchronous-asynchronous SoC design. However, the method has failed to gain traction commercially. It was unclear as to why there was no clear consensus about GALS design in the research community. Thus, the first research goal was to develop an extensive model that could characterise the physical and functional aspects of GALS SoCs and analyse the design technique's benefits and drawbacks. An extensive parametric model considering variability of several technology nodes was developed and GALS design was analysed versus its fully synchronous counterpart.

Secondly, it was conceptualised that mixed synchronous-asynchronous systems would require a unique mathematical model to represent its behaviour. The theory of step persistence and *bundles* was developed to cater this goal. Petri nets with step semantics were used to represent mixed synchronous-asynchronous behaviour. Implications of the model in verification and synthesis of mixed synchronous-asynchronous circuits were studied. A pruning algorithm was developed that would generate a suitable mixed synchronousasynchronous behavioural model by pruning a system's concurrent specification to achieve desired design characteristics. This result demonstrated how a fully asynchronous design could be formally re-engineered to a mixed synchronous-asynchronous design that couples elastic asynchronous design flexibility with rigid synchronous design simplicity. The final research goal was motivated from the exploration of research area identified in Figure 1.1. This led to a novel method for synthesising mixed synchronous-asynchronous circuits with varying levels of rigidity. The hypothesis was that *bundles* would reduce the area overheads of asynchronous design by relaxing granularity of handshake control. A Petri net based dataflow modelling technique was developed to model digital systems on a higher level of abstraction than RTL. Functional partitioning was then introduced in these dataflow models by identifying sets of *bundles* that could restrict elasticity whilst retaining functional behaviour. Taking the case of asynchronous bundled-data circuits, these sets of *bundles* were extended to a novel notion of *Elastic Bundles* which basically re-partitioned the design into coarse-grained locally clocked elements (synchronous) and fine-grained locally clocked elements (asynchronous). This net transformation enabled synthesis of the mixed synchronous-asynchronous circuit under standard EDA tool flow.

#### **1.3** Thesis Organisation

The thesis is structured as follows:

Chapter 1 presents the motivation behind this research and outlines the main contributions of this thesis.

Chapter 2 introduces the formal modelling languages used throughout the thesis and provides background on the asynchronous synthesis flow adopted in this research.

**Chapter 3** studies the impact of GALS-based physical partitioning in SoC design and presents the first contribution, a simulation framework that evaluates GALS design versus its fully synchronous counterpart considering physical and functional parameters.

Chapter 4 presents the second contribution, theory of step persistence and bundles, which provides a mathematical model to model and verify mixed synchronous-asynchronous circuits.

**Chapter 5** applies the concepts discussed in Chapter 4 to synthesise asynchronous circuits of varying levels of rigidity. The notion of 'Elastic Bundles' is introduced to enforce rigidity in fully asynchronous circuits, demonstrating mixed synchronous-asynchronous circuits consisting of granular locally clocked circuit elements. The final contribution is a novel method for modelling and synthesising 'Elastic Bundles'.

Chapter 6 summarises the key results and contributions, and presents directions for future work.

**Appendix A** presents the MATLAB code written to derive the results shown in Chapter 3.

**Appendix B** presents main parts of the verilog code for the 16-point FFT design discussed in Chapter 5.

**Appendix C** presents the synthesis timing constraints used to synthesise the 4-point FFT Elastic-bundle Maximal circuit of Chapter 5.

**Appendix D** presents the Petri net and Policy net models of the 4-point FFT architecture on the basis of which the results of Chapter 5 were derived.

### Chapter 2

### Background

This chapter summarises the fundamental concepts on the basis of which the thesis is constructed. Section 2.1 introduces the formal modelling languages used to model and verify digital systems in this thesis. In Section 2.2, the principles of bundled-data asynchronous pipelines is discussed and the CAD flow adopted to synthesise these circuits is summarised.

#### 2.1 Behavioural Modelling

In this section, we introduce the modelling languages used for the specification and verification of digital system behaviour. We recall definitions and notations of these formal models used throughout the thesis, specifically of step transition systems, Petri nets and step semantics of Petri nets. These preliminaries are based on the literature presented in [47, 48, 49, 50, 51, 3].

#### 2.1.1 Step Transition Systems

This section introduces the step transition system model which is the chosen modelling language to describe the behaviour of both asynchronous circuits as well as synchronous circuits in this thesis. We define this model formally as follows:

Let T be a finite set of net transitions representing actions of a concurrent system. A set of transitions is called a *step*, and we use  $\alpha, \beta, \gamma, \ldots$  to range over all steps  $\mathcal{P}(T)$ . Sometimes we identify a step  $\alpha$  with its characteristic function  $\alpha : T \to \{0, 1\}$ , and then write  $\alpha = \sum_{a \in T} \alpha(a) \cdot a^{1}$ . The size  $|\alpha|$  of  $\alpha$  is defined as the number of its elements.

#### Definition 2.1.1. (step transition system)

A step transition system (or ST-system) over a set of net transitions T is a triple  $STS = (Q, A, q_0)$  consisting of a set of states Q, including the initial state  $q_0 \in Q$ , and a set of labelled arcs  $A \subseteq Q \times \mathcal{P}(T) \times Q$ . It is assumed that:

- $(q, \emptyset, q) \in A$  for all  $q \in Q$ ;<sup>2</sup>

- the transition relation is deterministic, i.e., if  $(q, \alpha, q') \in A$  and  $(q, \alpha, q'') \in A$  then q' = q'';

- each state is reachable, i.e., if  $q \in Q$  then there are sequences of steps  $\alpha_1, \ldots, \alpha_n$  $(n \ge 0)$  and states  $q_1, \ldots, q_n = q$  such that  $(q_{i-1}, \alpha_i, q_i) \in A$  for  $1 \le i \le n$ .

For an ST-system STS as above, we introduce the following notations:

- $q \xrightarrow{\alpha} q'$  and  $q \xrightarrow{\alpha}$  whenever  $(q, \alpha, q') \in A$ ;

- $En_{STS}(q) = \{ \alpha \mid q \xrightarrow{\alpha} \} \subseteq \mathcal{P}(T) \text{ is the set of all steps enabled at a state } q;$

- $En_{STS} = \bigcup_{q \in Q} En_{STS}(q) \subseteq \mathcal{P}(T)$  is the set of all the enabled steps of STS;

- max(q) = {α ∈ En<sub>STS</sub>(q) | ∀β ∈ En<sub>STS</sub>(q) : α ⊄ β} is the set of all maximal steps enabled at a state q.

- $ready_{STS}(q) = \bigcup En_{STS}(q) = \bigcup_{\alpha \in En_{STS}(q)} \alpha \subseteq T$  is the set of all transitions ready to be executed at a state q, i.e., those belonging to steps enabled at q.

#### 2.1.2 Petri nets

Petri nets, introduced by C. A. Petri in his PhD dissertation [52], are widely used as a formal model to express concurrent systems. It is a powerful language which can be used to generate graphical and mathematical representation of asynchronous digital circuits and other distributed systems [50, 51, 3, 53, 54]. The *place/transition net* (or PT-net) is the most frequently used and best studied class of Petri nets where a place can hold any

<sup>&</sup>lt;sup>1</sup>The '  $\cdot$  ' operator used here denotes scalar multiplication.

<sup>&</sup>lt;sup>2</sup>For technical reasons we want to keep empty steps, as they might be important in future algorithms.

number of tokens. In this section, we recall definitions, notations and basic properties of place/transition nets.

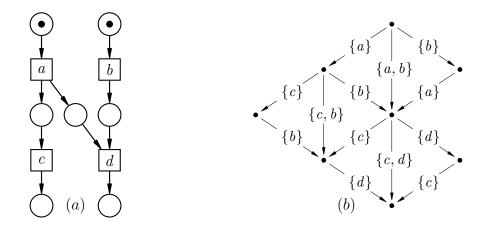

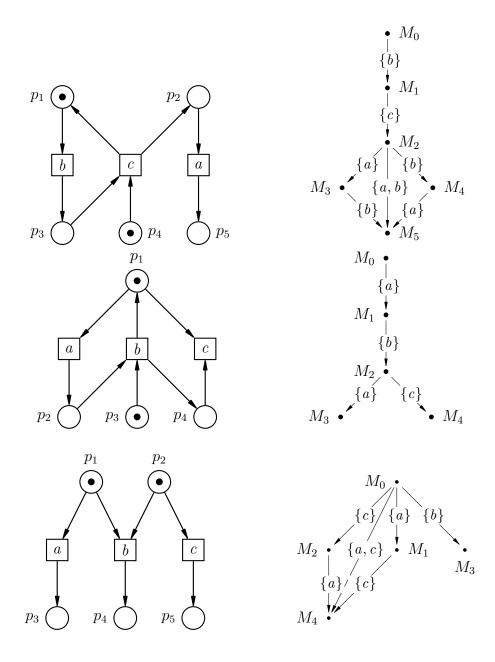

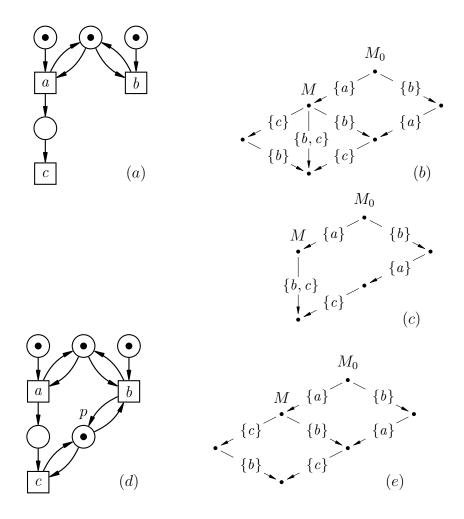

Figure 2.1: A PT-net  $\mathcal{N}(a)$ ; and its concurrent reachability graph  $CRG(\mathcal{N})(b)$ . Note that arcs (in fact, self-loops) labelled by the empty step are not shown in  $CRG(\mathcal{N})$ .

#### Definition 2.1.2. (place/transition net)

A place/transition net (or PT-net) is a tuple  $\mathcal{N} = (P, T, W, M_0)$ , where P and T are finite disjoint sets of respectively places and transitions,  $W : (P \times T) \cup (T \times P) \to \mathbb{N}$  is an arc weight function, and  $M_0 : P \to \mathbb{N}$  is an *initial marking* (in general, any mapping  $M : P \to \mathbb{N}$  is a marking).

We use the standard conventions concerning the graphical representation of PT-nets, as shown in Figure 2.1(a). For every element  $x \in P \cup T$ , we use

•

$$x = \{y \mid W(y, x) > 0\}$$

and  $x^{\bullet} = \{y \mid W(x, y) > 0\}$

to denote the pre-set and post-set of x, respectively. If  $x \in T$ , then any  $p \in {}^{\bullet}x$  is a pre-place of x, and any  $p \in x^{\bullet}$  is a post-place. The dot-notation extends in the usual way to a set  $X \subseteq P \cup T$ :

•

$$X = \bigcup_{x \in X} \bullet x$$

and  $X^{\bullet} = \bigcup_{x \in X} x^{\bullet}$ .

Moreover, for every place  $p \in P$  and step  $\alpha \in \mathcal{P}(T)$ , we denote:

$$W(p, \alpha) = \sum_{a \in T} \alpha(a) \cdot W(p, a)$$

and  $W(\alpha, p) = \sum_{a \in T} \alpha(a) \cdot W(a, p)$ .

In other words,  $W(p, \alpha)$  gives the number of tokens that the execution of  $\alpha$  removes from p, and  $W(\alpha, p)$  is the total number of tokens inserted into p after the execution of  $\alpha$ .

#### Definition 2.1.3. (place/transition net behaviour)

Let M be a marking of  $\mathcal{N}$ . A step  $\alpha \in \mathcal{P}(T)$  is *enabled* and may be *executed* at M if, for every  $p \in P$ :

$$M(p) \ge W(p, \alpha) . \tag{2.1}$$

We denote this by  $M[\alpha)$ . Executing such a step leads to the marking M', for every  $p \in P$  defined by:

$$M'(p) = M(p) - W(p, \alpha) + W(\alpha, p) .$$

(2.2)

We denote this by  $M[\alpha\rangle M'$ . Moreover, for a singleton step  $\alpha = \{a\}$ , we write  $M[a\rangle$  and  $M[a\rangle M'$  rather than  $M[\{a\}\rangle$  and  $M[\{a\}\rangle M'$ .

The concurrent reachability graph of  $\mathcal{N}$  is the ST-system

$$CRG(\mathcal{N}) = ([M_0\rangle, A, M_0)$$

over T where:

$$[M_0\rangle = \{M_n \mid \exists \alpha_1, \dots, \alpha_n, M_1, \dots, M_{n-1} \forall 1 \le i \le n : M_{i-1}[\alpha_i\rangle M_i\}$$

(2.3)

is the set of reachable markings and  $(M, \alpha, M') \in A$  iff  $M[\alpha\rangle M'$ . Furthermore, we call  $\alpha_1 \dots \alpha_n$ , as in the formula (2.3), a step sequence and write  $M_0[\alpha_1 \dots \alpha_n\rangle M_n$ . Figure 2.1(b) shows the concurrent reachability graph of the PT-net in Figure 2.1(a).

Remark 2.1.1. Note that for any Petri net  $\mathcal{N}$ ,  $CRG(\mathcal{N})$  is an ST-system, but we have different requirements for steps enabled in  $CRG(\mathcal{N})$  and in an arbitrary ST-system. This is intentional distinction. In Chapter 4, we define sub-ST-systems, and a sub-ST-system of a CRG might not be a CRG of a Petri net.

#### Definition 2.1.4. (sequential and concurrent conflict)

Two distinct transitions, a and b, of  $\mathcal{N}$  are in:

- sequential conflict at a marking M whenever  $M[a\rangle$  and  $M[b\rangle$ , but  $M[ab\rangle$  does not hold;

- concurrent conflict at a marking M whenever M[a⟩ and M[b⟩, but M[{a,b}⟩ does not hold.

Note that sequential conflict implies concurrent conflict, but reverse implication does not hold; e.g., transitions a and b in Figure 2.2 are in concurrent conflict but not in a sequential one.

Figure 2.2: A safe persistent PT-net  $\mathcal{N}(a)$ ; and its concurrent reachability graph  $CRG(\mathcal{N})(b)$ .

#### Definition 2.1.5. (safe net)

$\mathcal{N}$  is safe if, for all reachable markings  $M \in [M_0)$  and places  $p \in P$ ,  $M(p) \leq 1$ .

Note that reachable markings of safe nets can be treated as sets of places. Moreover, being a safe PT-net does not depend on the chosen semantics, i.e., the sequential semantics where only singleton steps are executed, or the full step semantics.

A step  $\alpha$  of a PT-net  $\mathcal{N}$  is:

- *active* if there is a reachable marking of  $\mathcal{N}$  enabling it;

- positive if  $W(\alpha, p) \ge W(p, \alpha)$ , for every  $p \in P$ ;

- disconnected if  $({}^{\bullet}a \cup a^{\bullet}) \cap ({}^{\bullet}b \cup b^{\bullet}) = \emptyset$ , for all distinct  $a, b \in \alpha;^3$

- lying on self-loops if W(p, a) = W(a, p), for all  $a \in \alpha$  and  $p \in P$ .

Clearly, the empty step is lying on self-loops, and if  $\alpha$  is lying on self-loops then it is also positive.

<sup>&</sup>lt;sup>3</sup>The notion of disconnectedness as defined here is not related to the standard graph-theoretic notion of disconnectedness (i.e., that a graph is disconnected if there is a pair of vertices without a connecting path).

#### Fact 2.1.1. (marking monotonicity)

If  $M[\alpha)$  and  $M'(p) \ge M(p)$ , for all  $p \in P$ , then  $M'[\alpha)$ .

#### Fact 2.1.2. (step monotonicity)

If  $M[\alpha)$  and  $\beta \subseteq \alpha$ , then  $M[\beta(\alpha \setminus \beta))$ .

#### Fact 2.1.3. (disconnectedness)

A step  $\alpha$  is enabled at a reachable marking M of a safe PT-net iff  $\alpha$  is disconnected and consists of transitions enabled at M.

*Remark* 2.1.2. The above facts are very intuitive and look trivial. However, they have a crucial importance in the discussion on persistence in Chapter 4.

#### 2.2 Bundled-Data Asynchronous Pipelines

In this section, the principles of bundled-data asynchronous pipelines is discussed and a summary of the relative-timing (RT) based CAD flow is provided. The concepts presented in this section are based on literature presented in [45, 46, 55, 32, 1].

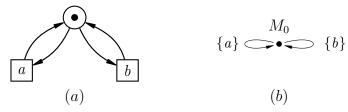

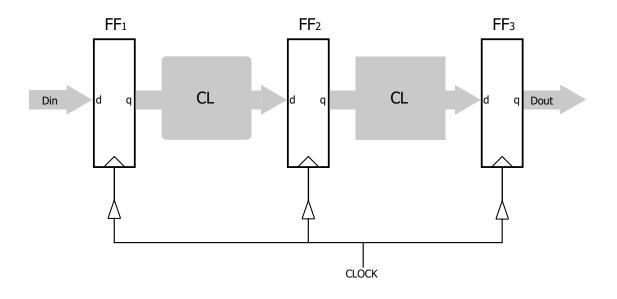

#### 2.2.1 Synchronous vs. Asynchronous Pipelines

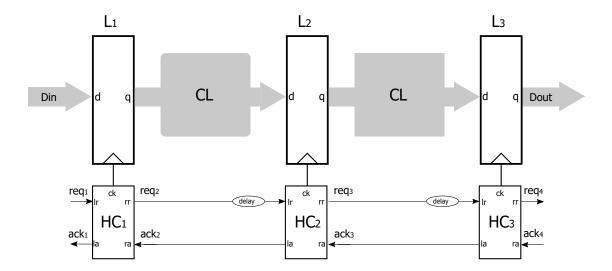

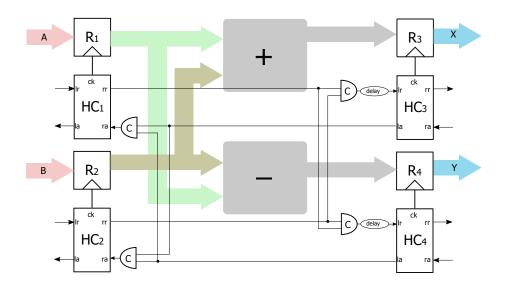

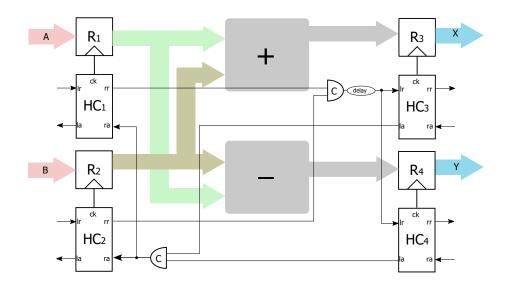

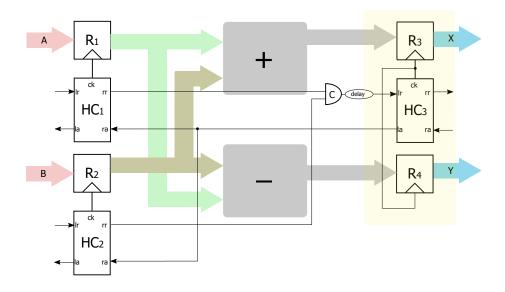

Pipelining is a principle element of high-performance digital design catering both synchronous as well as asynchronous systems. The fundamental difference between synchronous and asynchronous pipelines lies in the communication channel that enables data items to move from one pipeline stage to the next. Figure 2.3 illustrates this with a simple example showing a traditional synchronous linear pipeline and an asynchronous linear pipeline. In synchronous pipelines, a global clock signal handles the communication between pipeline stages in a lock step fashion. A critical requirement of such a globally clocked system is that each stage's worst-case data path delay should be lower than the fixed clock period. Hence, traditional synchronous systems feature a rigid communication scheme where all pipeline stages operate at a fixed clock frequency.

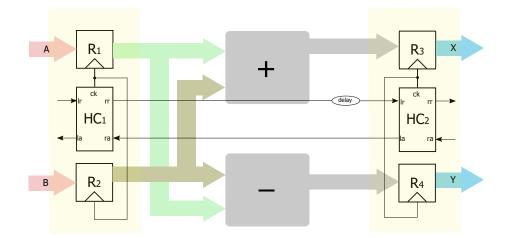

In contrast, asynchronous pipelines do not have a global clock and achieve communication between pipeline stages by handshaking between neighbouring registers. Figure 2.3b

(a) Synchronous pipeline

Figure 2.4: Four-phase and two-phase asynchronous signalling protocols

depicts a bundled-data asynchronous pipeline where the global clock signal is replaced by handshake control (HC) logic blocks that implement fine-grained local locking at registers. A request-acknowledge based handshake protocol consisting of handshake signals, request (req) and acknowledge (ack), advance data items on a per-stage basis. Delay elements, implemented as inverter chains, matching each stage's critical path delay, are inserted on req signals to ensure data stability and validity before reaching the next pipeline stage. Thus, in comparison to synchronous design, bundled-data handshaking can be viewed as system of multiple fine-grained local clocks whose period is determined by actual critical path delay of individual pipeline stages.

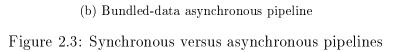

#### 2.2.2 Bundled-data protocols

The scheme of using a synchronous-style data path coupled with a bundling signal (req) that enforces a worst-case delay for valid data being received stable at a neighbouring pipeline stage is what defines the class of bundled-data asynchronous circuits [46]. Bundled-data handshaking can follow two basic asynchronous signalling protocols, namely four-phase and two-phase. Figure 2.4 illustrates these two communication protocols. In the case of four-phase handshaking, req and ack are initially deasserted low. A transaction is initiated with a rising req from the sender. The receiver responds with a rising ack acknowledging the transaction. These two signals are then deasserted low to allow for

Figure 2.5: Relative-timing based asynchronous design flow (reproduced from [1])

the next transaction. The four-phase handshake protocol is also known as return-to-zero (RTZ) signalling or level signalling. In the case of two-phase handshaking, a single toggle of *req* initiates a transaction which is followed by a single toggle of *ack* acknowledging the transaction. The two-phase handshake protocol is also known as non-return-to-zero (NRZ) signalling or transition signalling. This protocol only requires a single round-trip communication per transaction as compared to double round-trip communications in four-phase signalling. Between the two protocols, the four-phase protocol is widely used due to simpler hardware design.

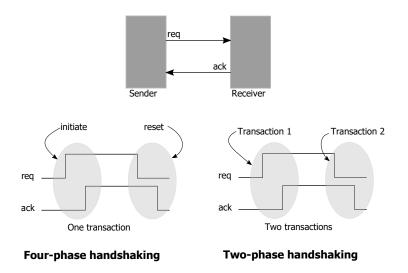

#### 2.2.3 RT-based Bundled-Data Circuit Synthesis

Relative timing (RT) is a method of modelling and controlling the firing order of two events based on logic path delays. This method can accurately capture, model and validate heterogeneous timing behaviour of synchronous as well as asynchronous circuits [32]. RT constraints are enforced during circuit synthesis so that hazardous states are filtered out. RT constraints consist of a common timing reference, called as point-of-divergence (pod), and a pair of events ordered in time, called as point-of -convergence (poc) [1]. Pathbased RT constraints specify the order of arrival of two paths from a common causal pod to ordered events poc. Such RT constraints are represented as  $pod \mapsto poc_0 + m \prec poc_1$ where  $poc_1$  is ordered to fire after  $poc_0$  occurs in time with margin m.<sup>4</sup> Let us consider the bundled-data linear pipeline in Figure 2.3b to illustrate this further. The delay element between stages  $L_1$  and  $L_2$  can be sized by enforcing the following RT constraint:

$<sup>^{4}\</sup>mapsto$  is an arrow symbol used here to define the function.  $\prec$  is a relation operator denoting precedence.

#### $req_1 \uparrow \mapsto L_2/d + margin \prec L_2/ck \uparrow$

The RT-based design flow enables rapid development of asynchronous designs by providing a set of characterised asynchronous templates that can be easily integrated with synchronous CAD tools [32]. These templates can be inserted in designs with supporting clocked CAD tool constraints for synthesis, place and route, timing driven sizing, optimisation and validation. A version of RT asynchronous design flow taken from [1] is shown in Figure 2.5.

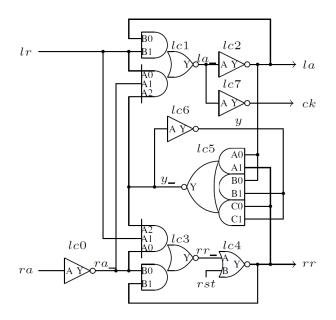

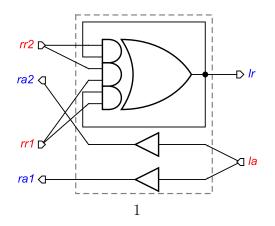

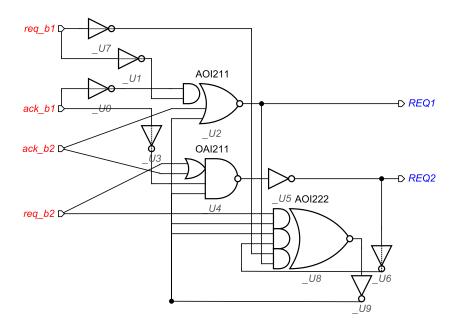

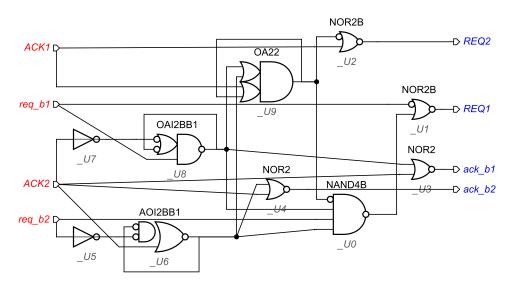

The RT design flow enables the adoption of bundled-data asynchronous circuits in the traditional synchronous design flow with little expertise in asynchronous design. First, the bundled-data design is partitioned into data path logic and control logic. The data path is synthesised using normal synchronous CAD synthesis procedures. Handshake clocking is, then, implemented by replacing the global clock with the HC logic blocks as shown in Section 2.2.1. Characterised asynchronous design elements of the HC block are used to implement the control logic. Figure 2.6a shows the circuit implementation of an HCblock based on four-phase handshaking as characterised in [32]. The HC circuit's verilog implementation in our in-house 90nm Faraday library is shown in Figure 2.6b. Next, RT constraints are specified based on the timing constraints elaborated in [32]. These constraints are integrated into clocked CAD tool flow by specifying them as **sdc** constraints which are supported by commercial tools. For example, RT constraints represented by set max delay and set\_min\_delay commands are used to perform timing driven synthesis. These constraints are responsible for constraining the data path logic and adding delay elements on the control path. Finally, the RT constrained architecture is passed through usual clocked CAD tools and flows. In this fashion, bundled-data asynchronous circuits can be synthesised by leveraging clocked CAD tool flow.

(a) HC Circuit Implementation (reproduced from [1])

```

module handshake_ctl(

input wire Ir, ra, reset,

output wire rr, la, ck

);

wire ra_,la_,rr_,y_,y;

lc0 ( .l(ra), .0(ra_) );

lc1 ( .B1(lr), .B2(ra_), .B3(y_), .A1(lr), .A2(la), .0(la_) );

lc2 ( .l(la_), .0(la) );

lc3 ( .B1(ra_), .B2(lr), .B3(y_), .A1(ra_), .A2(rr), .0(rr_) );

lc4 ( .l1(rr_), .l2(reset), .0(rr) );

lc5 ( A1(la) B1(y) C1(rr) 0(y ) );

INVX 1

AOI23X1

INVX1

A0I23X1

NR2X1

( .A1(la), .B1(y), .C1(rr), .O(y_) );

MA0I222X1 lc5

lc6 ( .l(y_), .O(y) );

lc7 ( .l(la_), .O(ck) );

INVX1

INVX1

```

endmodule

```

(b) Verilog Implementation of HC in 90nm Faraday library

```

Figure 2.6: Characterised handshake control element for bundled-data circuits

### Chapter 3

# Physical Partitioning and its Limitations

One of the first partitioning techniques for mixed synchronous-asynchronous digital designs, and a popular one, was introduced by Chapiro in his doctoral thesis titled 'Globallyasynchronous locally-synchronous systems' [44]. Chapiro's technique abbreviated as GALS was designed to exploit the advantages of asynchronous design while maximally reusing the products of the synchronous design flow. This is achieved by partitioning a system into synchronous islands that inter-communicate by asynchronous handshaking. Over the last couple of decades, GALS system design has been widely researched as an alternative to synchronous SoC designs mainly as a physical partitioning strategy. However, this technique has gained mixed reviews from the research community with no clear indication of its future in SoC design. In this chapter, we are motivated to investigate the GALS physical partitioning technique and review its applicability to SoC design.

#### 3.1 Introduction

Globally asynchronous locally synchronous (GALS) design [44] is a promising approach that can reduce the design complexity of modern SoCs and improve energy efficiency by incorporating heterogeneity. This design principle has been mainly implemented as a physical partitioning strategy for SoC design where top-level hierarchical blocks of varying clock speeds such as heterogeneous IP cores are partitioned into distinct clock domains

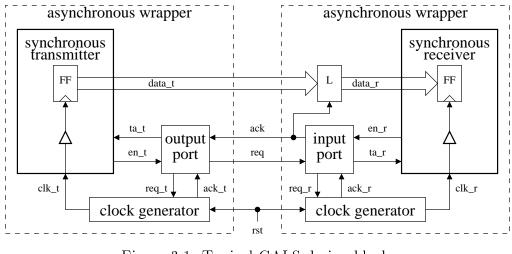

Figure 3.1: Typical GALS design block.

known as synchronous islands. Clock distribution is handled locally in synchronous islands and communication across clock domain boundaries is achieved by asynchronous design principles. A typical GALS system is shown in Figure 3.1. Each synchronous island has its own local clock which would be "paused" during data transfer and resumed after acknowledging the transfer. Synchronous islands are enclosed within asynchronous wrappers which handle asynchronous handshake control and local clock management.

GALS design can provide genuine scope for power savings, performance improvement and energy efficiency compared to its synchronous counterpart owing to its scheme of multiple clock domains. One of the main benefits is a simplified clock distribution network (CDN) offering significant power savings and performance improvement. GALS methodology, however, induces certain design overheads such as latency penalty between clock domains which would impose restrictions on the partitioning granularity. There are several research works such as [10, 56, 57, 58, 35, 12, 36, 37, 41, 15] that demonstrate the potential of GALS design but the benefits reported are not consistent and in some cases contradictory. Most of them follow an assemble-and-validate design style and lack system analysis procedures to justify GALS partitioning scenarios.

The authors in [11, 58] make a good effort to judge the applicability of GALS methodology by comparing the power and performance figures against a fully synchronous design. They showed that GALS performance penalty is around 6.3% when using pausable clocks with five clock domains. The main reason for system throughput reduction is due to frequent inter-island communications and the presence of communication feedback loops. The observations were made from a processor case study and hence, the same effect would not hold true for application specific designs. For example, parallel pipelined data path implementations of complex operations such as FFT [1] or JPEG Encoder [41] will have fewer such loops and would show much lower performance penalty with GALS. The study also demonstrated 10% of average power savings across several GALS implementations. However, the effect of process variations was not accounted in the study. This effect is quite important for comparing digital design implementations, especially for newer semiconductor process technologies, because a growing portion of clock period budget is allocated for variability which directly has an impact on the CDN power and maximum clock frequency per island.

Yu and Bass studied the impact of CDN design on the peak performance of processor cores considering both GALS and globally synchronous design styles [41]. The GALS processor being of a constant size has the highest peak performance compared to the larger synchronous processor array due to lower clock skew. Further decrease in peak performance of the synchronous processor is seen due to additional skew penalty from process and environment variations, and a performance figure of 76.8% to the GALS case is reported for an array of 121 processors. Their main contribution was the performance analysis of several applications on GALS and synchronous processor array architectures. Each application was mapped onto the processor cores and performance was compared. Performance reduction from GALS was in the range of 0% to 2.3% and power savings of upto 40% was demonstrated. Their method of analysis is for a GALS chip multiprocessor with FIFO style of synchronisation wherein computations are localised within each processor's clock domain. Inter-island communications are less frequent thus explaining the low performance degradation figure. Similar performance results are expected from GALS-based application specific designs.

Hemani *et al* suggested that significant clock power reduction of about 70% can be obtained by dividing a system into N equally sized islands [10]. However, till date, there are only a few of GALS implementations that report actual power performance measurements of GALS fabricated chips. In [36], a GALS baseband processor was designed and fabricated on 250 nm process, and compared with its synchronous implementation. Power savings of only 1% were reported when about 17% was to be expected. The authors in [16] evaluated GALS versus synchronous implementation of an OFDM baseband transmitter in 40nm CMOS technology. 20% power savings in the clock power was reported with a total of 6% power reduction in the overall chip power. Furthermore, the number of levels in the clock tree dropped from 27 to less than 10 in the GALS implementation. It was reported that the design was partitioned into six islands based on functional and physical criteria. However in both the implementations, the choice of partitioning granularity and boundaries is unclear.

The applicability of GALS methodology to modern SoC design will depend on several factors such as system dataflow, design size and process technology. One of the main benefits of GALS is a CDN which consumes lower power and delivers a low-skew clock. However, these gains will have to be weighed against the penalties introduced due to the GALS synchronisation protocol in order to determine overall system improvement. A calculated system level analysis is hence required before choosing to GALSify a system and many studies lack this. In this chapter, we discuss the parameters and metrics required to conduct such a trade-off analysis.

The chapter is organised as follows. Section 3.2 discusses the analysis methodology and simulation framework for analysing GALS chip partitioning. Section 3.3 discusses the results obtained from the physical partitioning simulation. Section 3.4 concludes this chapter and presents scope for future work.

# 3.2 Methodology

# 3.2.1 Characterising a GALS Design

Several design parameters will influence the decision towards a GALS architecture. This section discusses some of the key factors that govern an effective GALS implementation.

## 3.2.1.1 Clock Distribution Network

The clock distribution network is a very important component of a synchronous design governing its functioning and performance. Any violation to the clock timing specific-

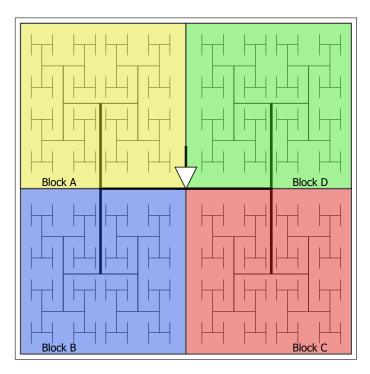

Figure 3.2: Global CDN and GALS partitioning.

ations can affect logical operation of the circuit and lead to design functional failure. Moreover, the CDN can consume up to about 40% of the chip dynamic power in high performance designs [59] and hence any optimisation reducing the clock tree power is considered a significant design improvement. For example, the authors in [60] demonstrated overall chip power savings of 25% by optimising the CDN using a combination of energy recovery and clock gating techniques. CDN design depends on the chip floorplan size, total load to distribute the clock signal and clock design constraints such as buffer/load rise time and skew budgets. For instance, greater area to distribute the clock requires stronger buffers to deliver clock signal due to larger interconnect capacitance.

GALS design has been shown to reduce the clock switching power of larger designs by partitioning into smaller CDNs [10]. Figure 3.2 shows a clock tree distribution network of a generic design and a trivial case of GALS partitioning. It can be visualised that clock power is reduced due to removal of the global clock tree. There will, however, be an optimal number of partitions for any design to benefit from such CDN power savings [57]. This effect is seen due to additional power consumption from GALS architecture overheads: wrapper circuit and local clock generator. In this study, we extend the analysis to determine the CDN power savings for a design over different process technologies.

#### 3.2.1.2 Sensitivity to Process Variations

Clock signals act as control signals that guide data movement between registers in a sequential data path. The timing of these signals has to be precise for proper system operation. Any delay uncertainty can cause system failure if the CDN design has not accounted these effects.

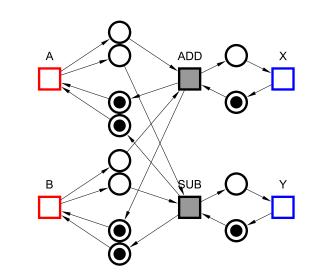

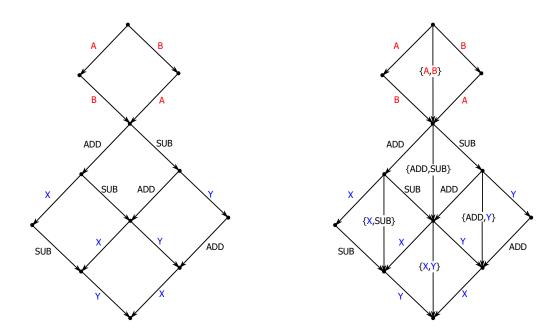

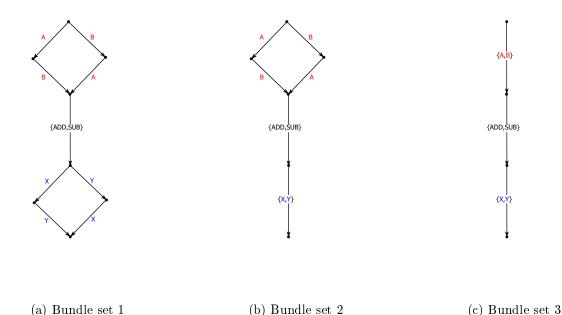

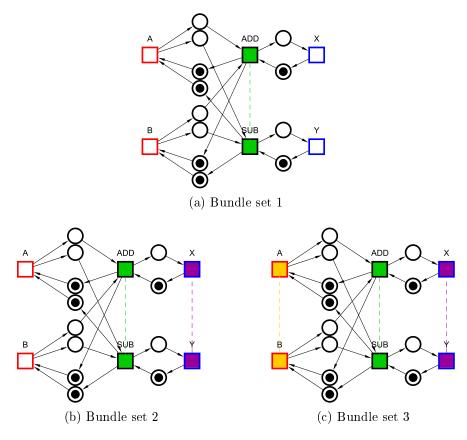

Each element of a clock path is sensitive to process, environmental and geometric variations which lead to different clock arrival times at the sinks of the CDN. This temporal difference is simply the clock skew that has to be characterised by the designer and accounted for, which if not, would violate the setup and hold time constraints required for safe data latching. Timing violations are avoided by either reducing the delay uncertainty of the CDN or relaxing the timing constraints [59]. The latter involves accommodating a larger clock skew budget by increasing the clock period of the design at the cost of reduced system performance. Delay uncertainty of the CDN is reduced by desensitising the interconnects in the clock net [61] and/or increasing the clock buffer sizes [62]. This, however, comes at cost of higher power consumption.